rloc

Модератор-

Постов

3 249 -

Зарегистрирован

-

Победитель дней

14

Весь контент rloc

-

прецизионный усилитель

rloc ответил ivanoviv тема в Вопросы аналоговой техники

1) По исходным данным на входе усилителя имеем сигнал размахом 0.5 В. Наиболее вероятно нагрузка 50 Ом. Мощность сигнала на ней составит около 4 дБм. 2) Тепловой шум - широкополосный. При прохождении через усилитель он будет иметь две составляющие: одна за счет простого добавления, вторая за счет переноса усилителем с нулевой частоты. Второй составляющей попробуем пока пренебречь и считать усилитель условно линейным на рассматриваемой частоте. 3) Спектральная плотность мощности теплового шума (СПМШ) при комнатной температуре составляет -174 дБм/Гц, которую можно разбить на две составляющие: амплитудную и фазовую, с условно равными мощностями и соответственно СПМШ каждой равной -177 дБм/Гц. 4) Теоретически генератор при комнатной температуре и мощности 4 дБм может иметь на выходе относительно несущей амплитудный и фазовый шум при больших отстройках на уровне -181 дБн/Гц 5) Возьмем для примера усилитель AD8056. Он имеет при больших отстройках плотность шума 6 нВ/sqrt(Гц), абсолютное значение СПМШ на нагрузке 50 Ом составит -151 дБм/Гц или иначе можно сказать коэффициент шума равный 23 дБ (токовыми шумами в 1 нА/sqrt(Гц) можно принебречь). При добавлении резисторов обратной связи шумы только увеличатся, так например в схеме с неинвертирующим включением и делителем в обратной связи 820 Ом и 270 Ом (820||270 = 203) получим добавочные шумы на уровне 1.8 нВ/sqrt(Гц), что в данном случае значительно меньше собственных шумов усилителя и можно пока пренебречь. 6) Характер шумов на выходе AD8056 нам неизвестен, из практики можно положиться на преимущественное преобладание фазовой составляющей. Таким образом добавочный фазовый шум усилителя составит -155 дБн/Гц для сигнала 4 дБм. Для сравнения ФШ OCXO фирмы Maxic Xtal при отстройке более чем на 10 кГц составляет <-165 дБн/Гц. 7) Как будут трансформироваться фликкерные шумы усилителя в фазовые сказать сложно, нужно как минимум знать уровень интермодуляционных составляющих при выходной амплитуде 2 В. По AD8056 нашел только уровень гармонических составляющих. 8) Логические элементы можно представить в виде усилитель + ограничитель, не вижу препятствий мешающих подать на вход синус. -

прецизионный усилитель

rloc ответил ivanoviv тема в Вопросы аналоговой техники

Если речь идет о кварцевом генераторе, то применять ОУ для раздачи - не самый лучший вариант. Любой ОУ даст коэффициент шума не лучше 10дБ за счет собственных шумов и резисторов обратной связи - это приведет к росту фазовых шумов (джиттера). Для раздачи лучше использовать логические элементы из серии "Tiny Logic" или "Little Logic", а еще лучше "unbuffered" серию микросхем фирмы National, специально разработанную для кварцевых генераторов. Уровень сигнала можно регулировать напряжением питания соответсвующих буферов, а если нужен чистый синус, то поставить на выходе ФНЧ фильтры (есть готовые). -

Во второй статье (fig.11) получается, что "noise floor" у мощного диодного удвоителя находится на уровне -185 дБн/Гц Low Noise, VHF Crystal-Controlled Oscillator Utilizing Dual, SC-Cut Resonators 01539856.pdf Spectral performance of frequency multipliers and dividers 00270014.pdf

-

DBM со сдвигом в 90 гр.

-

Вспомнил, у Temex есть малошумящие генераторы на ПАВ, поднимают шумы с -182 дБн/Гц (320M => 640M). Думаю генераторы Pascall и Synergy актуальны. Догадываюсь каким образом это достигается: для случая удвоения упоминал Driscoll, для произвольного случая несколько сложнее (отдаленно вспоминается статья Agilent про SPD, никак не найду).

-

Мне сообщили, что до недавнего времени квоты на экспорт по этим генераторам не предоставлялись, как раз из-за опаски потрошения. По той фирме, что запрашивала квоту в мае, тщательным образом наводились справки ) Так, что будьте осторожны.

-

Мне пришел ответ, что LNXO100 делаются в Германии и цена для России на май месяц 1480Eu. Вполне демократично по сравнению с остальными и лицензировать ничего не надо.

-

Это по информации на предыдущую версию генератора? Шумы -178 дБн/Гц без фильтра, как у TEMEX, тоже очень неплохи. У меня пока по теории не все стыкуется, в ближайшее время попробую сформулировать вопросы.

-

Судя по волнистому характеру кривой, шумы находятся за пределом чувствительности прибора. Надо как-нибудь обсудить теоретические основы. Тема очень интересная, много спорных моментов.

-

Удивительно, но практически побитное совпадение двух кривых )

-

Этот констрейтс действует только на те элементы у которых есть аттрибут RLOC cgd.pdf :

-

Куда девались танталовые конденсаторы EPCOS

rloc ответил VCO тема в Компоненты

KEMET Agrees to Acquire EPCOS Tantalum Capacitor Business -

измерение TDR

rloc ответил Michael58 тема в Метрология, датчики, измерительная техника

Был в этом древнем HP8753C такой режим, но как часто бывает, опциональный. По описанию очень интересным выглядит векторный рефлектометр CABAN R54, и цена небольшая, и скорость высокая, и габариты небольшие - одним словом есть чем похвастаться на международной выставке. -

измерение TDR

rloc ответил Michael58 тема в Метрология, датчики, измерительная техника

Почти у всех современных VNA есть функция "time domain" (Distance-To-Fault). Например в N9923A достаточно ввести "velocity factor" и сразу видны все неоднородности линии в мм. Всегда считал, что частотный метод более точный чем временной. -

ADF41020: 18 GHz Microwave PLL Synthesizer

rloc ответил VCO тема в RF & Microwave Design

Analog Devices недавно порадовала нас выходом еще одной высокочастотной дробной PLL ADF4159: -

Если низкие частоты подаются извне (не после внутреннего делителя), возникает вопрос о скорости нарастания сигнала. Возможно не хватает дополнительного усилителя-ограничителя.

-

У Александра получается лучше, чем -140 дБн/Гц при 50 МГц A Broadband, Low Phase Noise, Fast Switching PLL Frequency Synthesizer A_Broadband_Low_Phase_Noise_Fast_Switching_PLL_Frequency_Synthesizer.pdf

-

A new concept in Frequency Synthesis

rloc ответил Vitaly_K тема в RF & Microwave Design

Любой синтезатор из серии MTS2500, шаг сетки - 1 Гц. С ценою возможно ошибаюсь, 200$ - это было за модель с шагом 0.5 МГц. -

A new concept in Frequency Synthesis

rloc ответил Vitaly_K тема в RF & Microwave Design

А если взять к примеру синтезаторы фирмы Synergy: и шумы будут ниже, и цена порядка 200$, и диапазон октавный, и фирма известная и крупная? Спорить не буду, не легко Вас переубедить. Тем же самым "топором да долотом" потом придется новоиспеченный чип на макетку ставить и обвязку всякую делать. Хорошо, что Вы подметили аналогию с DDS, решаемые проблемы будут очень близки. -

A new concept in Frequency Synthesis

rloc ответил Vitaly_K тема в RF & Microwave Design

Vitaly_K, у Вас уже была собрана макетная плата, фотографии которой можно найти в статьях. Кто ее конструировал, собирал и отлаживал? В таких случаях часто приходится следовать принципу "сам себе и жнец, и швец, и на дуде игрец". В интегральном исполнении тоже есть свои нюансы, но согласитесь, дешевле несколько вариантов макеток сделать, чем несколько чипов. К тому же шумы сейчас настолько огромны, что скрываются все недостатки. Читал материалы конференций IEEE, где очень часто пишут сколько много калибровок приходится вводить в чип, чтобы получить рабочий образец. Поэтому надо максимально отработать на макете - это и дешевле, и проще, и быстрее. -

A new concept in Frequency Synthesis

rloc ответил Vitaly_K тема в RF & Microwave Design

Никак у меня не получается донести до Вас идею. Если поставить внешние триггеры (D-trigger со входными сигналами D, CLK и выходом Q) по каждому разряду, то фронты/спады сигналов будут отсчитываться строго от фронта тактового сигнала и не будут зависеть от разброса задержек и дрожания сигналов после FPGA. Таким образом мы полностью исключаем влияние FPGA на качество сигнала и забываем про ModelSim. Перечислим основные преимущества моего предложения: 1) Погрешность разброса задержек сигналов можно сделать на уровне 0.005 нс, для сравнения, внутри FPGA, с учетом всего пути распространения - не лучше 0.2 нс. 2) Уровень фазовых шумов - как минимум на 20 дБ лучше. 3) На макете есть прекрасная возможность вручную отъюстировать все параметры: задержки в небольших пределах (путем накладывания диэлектрика с высоким эпсилон на соответствующую линию), номиналы суммирующих резисторов. В интегральном исполнении потребуется только подстройка лазером, что на первых порах может быть не доступно. Мой вывод такой: пока макет не будет доведен до рабочего образца с тщательным просчетом всей математики, ждать каких-нибудь результатов от интегрального исполнения бесполезно. -

A new concept in Frequency Synthesis

rloc ответил Vitaly_K тема в RF & Microwave Design

Vitaly_K, решил перенести наш разговор в соответствующую тему, чтобы не мешать Vecheslav. Я с Вами абсолютно не согласен. Во-первых у меня есть положительный опыт макетирования высокоскоростного многоразрядного сигма-дельта ЦАП с точно такими же резисторами по выходу. До 100 МГц шумы получались просто великолепные, больше было проблем со спурами. Давайте уточним, откуда по выходу FPGA возникает фазовый шум? Основной его источник - это случайное дрожание фронта/спада выходного сигнала (фликкер, дробовый шум) и низкая ЭМС с соседними сигналами и питанию. Подумайте внимательно, какой будет детерминированный разброс в задержках при буферизации на LL-триггерах на печатной плате и насколько он будет отличаться от разброса внутри FPGA? Напомню, что внутри FPGA задержка распространения сигнала в основном определяется не длиной линий, а количеством КМОП транзисторов коммутирующих эти линии. И еще один вопрос: если не использовать схем "dithering", на что больше будет влиять детерминированный разброс по задержкам: на фазовый шум или на величину спур? -

Можете не сомневаться, шумы получатся такие же низкие. С adf4002 не проверял, это был только альтернативный вариант. Согласен, есть некоторая неопределенность в задержке сигнала на выходе adf4002. В самой идеи ничего нового нет, все хорошо забытое старое, достаточно взглянуть на внутреннюю структуру NB7N017M, есть и много других примеров, под рукой пока не нашел. Я для себя нашел способ работать на CPLD на частотах выше 500 МГц, поэтому альтернативный вариант отпал. Немного повторюсь, на LL-триггере можно сделать фиксированный делитель с низкими шумами и входной частотой не менее 1.5 ГГц, выше просто не проверял, хотя запас есть и чувствуется не маленький.

-

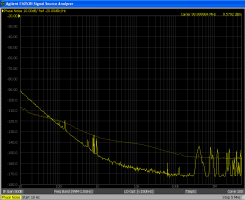

Для сравнения приведу шумы самого ГК 100 МГц и на выходе CPLD без LL после деления на 5 (светлая линия), можно сравнить с картинкой выше. Этот результат будет очень полезен Vitaly_K, буферизация всех сигналов с помощью LL-trigger поможет более чем на 20 дБ улучшить шумы в его синтезаторе. Думаю результат будет не хуже, чем при интегральном исполнении и сразу решится вопрос "стоит ли овчинка выделки". P.S. Не исключаю возможности дискретного исполнения фазового детектора на LL с шумами лучше Hittite.

-

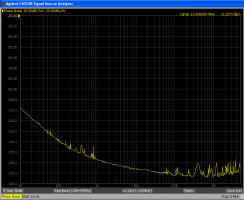

Есть еще один очень красивый способ получения хороших шумов при делении на частотах до 400 МГц. 1) adf4002 + триггер из серии "Little Logic" по выходу. 2) CPLD + LL-trigger. В любом случае фазовые шумы получаются на порядок лучше hmc394, также немаловажно значительно более низкое потребление и как следствие меньшее значение пролаза деленной частоты в выходной сигнал по питанию при одинаковых номиналах фильтрующих элементов. Я предпочитаю второй вариант из-за большей гибкости и универсальности. Для примера привожу шумы ГК 100 МГц, деленного на 5 с использованием XC2C32A-6QFG32C + 74AUP1G80GW: