toshas

Свой-

Постов

419 -

Зарегистрирован

-

Посещение

Весь контент toshas

-

На сколько тактов сбрасывает ? Какими пачками идет вычитывание по axi ? Посмотрите на готовность к передаче ядра pcie.

-

Может в этом причина ? Посмотрите анализатором очередность транзакций на шине axi.

-

Release Notes for Vivado 2015.3 are available http://www.xilinx.com/support/documentatio...all-license.pdf Changes: https://forums.xilinx.com/t5/Xcell-Daily-Bl...ado/ba-p/658674 Интересен данный пункт: •PCIe + 8-channel DMA for Virtex-7, 20nm UltraScale, and 16nm UltraScale+ devices Известно сколько будет стоить лицензия на него ? Аналоги от plda и nwlogic довольно дороги.

-

увеличения количества слотов в PC

toshas ответил 1113 тема в ISA/PCI/PCI-X/PCI Express

x16 + 6*x8 +9*x1 = 73 скоростных линии это не менее XC7VX550T (5000usd) + цена soft-core pcie + некая хитра логика коммутации ядер -> не жизнеспособно. или это PLX PEX (минимальный порт x4) 25шт. x4 портов = 100 линий, таких нет (макс 96), значит два каскадом (увеличит латентность на втором каскаде), скажем 8780(16up+6*x8+16down) + 8764(16up+9*x4) ~ 700usd -

Добавление даты в проект

toshas ответил Kluwer тема в Среды разработки - обсуждаем САПРы

Для Xilinx есть еще такой вариант: на этапе bitgen добавить время в файл прошивки, а потом через специальный примитив USR_ACCESS получить к нему доступ из работающего проекта. http://www.xilinx.com/support/documentatio..._usr_access.pdf -

Патент на новый тип персонального компьютера

toshas ответил one_man_show тема в ARM

Intel тоже хочет не отстать http://www.intel.com/content/www/us/en/com...pute-stick.html -

xapp1171-pcie-central-dma-subsystem.pdf

-

еще один аналог, тоже бесплатный - Colasoft Packet Builder

-

появился второй том, но уже по 1 760 http://www.combook.ru/product/11038852/

-

ActiveHDL+ISE (IP core)

toshas ответил hendehoh тема в Среды разработки - обсуждаем САПРы

на примере 8b10b: aurora_8b10b_v8_3.v - модуль верхнего уровня, который нужно использовать в своем проекте aurora_8b10b_v8_3_exdes.v - example design, пример использования, включает генерацию и проверку передаваемых данных aurora_8b10b_v8_3_tb.v - тестбенч для проведения симуляции example design -

ActiveHDL+ISE (IP core)

toshas ответил hendehoh тема в Среды разработки - обсуждаем САПРы

Найдите файл верхнего (top) уровня, тогда вся иерархия соберется автоматически. Также обратите внимание на exdes - пример установки этого самого top. -

Добрый день! Эти спецификации конечно еще далеко не финальные. Но закладываться надо уже сейчас (особенно внешний кабель 3.0). И получить хотя бы общее понимание к чему идем было бы полезно. Нет ли у кого-нибудь доступа к этим документам и возможности поделиться ? https://www.pcisig.com/specifications/pciex...ew_zone/archive PCIe 4.0 Base Spec Rev 0.5 THIS IS A DRAFT SPECIFICATION ONLY AND, AS SUCH, IS SUBJECT TO FURTHER REVISION AND REVIEW WITHOUT NOTICE. THIS DRAFT SPECIFICATION IS PROVIDED TO YOU FOR REVIEW PURPOSES ONLY AND SHOULD NOT BE RELIED UPON FOR DESIGN OR MANUFACTURING PURPOSES. •Download the PCIe 4.0 Base Spec Rev 0.5 - non change bar (12.2 MB) •Download the PCIe 4.0 Base Spec Rev 0.5 - change bar (13.4 MB) PCIe 3.0 External Cabling Spec Rev 0.5 THIS IS A DRAFT SPECIFICATION ONLY AND, AS SUCH, IS SUBJECT TO FURTHER REVISION AND REVIEW WITHOUT NOTICE. THIS DRAFT SPECIFICATION IS PROVIDED TO YOU FOR REVIEW PURPOSES ONLY AND SHOULD NOT BE RELIED UPON FOR DESIGN OR MANUFACTURING PURPOSES. •Download the PCIe 3.0 External Cabling Spec Rev 0.5 (2.03 MB)

-

http://www.xilinx.com/support/documentatio...le-overview.pdf http://www.xilinx.com/publications/prod_mk...ction-guide.pdf http://www.xilinx.com/publications/prod_mk...ction-guide.pdf Из нового: Новые блоки памяти увеличенного объема UltraRam 288Kb (всего до 432Mb на топовом Virtex). Поддержка аппаратного блока PCIe x8 gen 4 и x16 gen 3. В новых Zynq теперь 4 ядра основных, 2 ядра вспомогательных и отдельный gpu. Некоторые кристаллы получили видеокодек VCU H.265 (up to 4Kx2K at 60fps or 8Kx4K at a reduced frame rate (~15 fps).). В целом линейки сильно запутали, например, в топовых Kintex убрали ядро PCIe (KU9P,KU13P), или топовые кристаллы теперь в некоторых местах слабее старых (в KU115 5,520 DSP в новом KU13P только 3,528). Будем надеяться на ошибки типа copy-paste. Применили новых попугаев Effective LEs (K). До сих пор правится линейка Kintex UltraScale! Убрали KU075 и KU100, добавили KU085 и KU095.

-

Причем не все вендоры хотят их афишировать http://forums.xilinx.com/t5/Virtex-Family-...ery/td-p/476482

-

Возникла пара вопросов: 1) (По вашему опыту) Нарезка проекта на такое количество блоков в том числе мелких и их последующая плотная компоновка действительно дает сильный выигрыш ? 2) Как быть с сохранением порядка данных на приемной стороне в случае перезапроса пакета на одном из буферов ? 3) Если ошибки возникают и требуется перезапрос, а ацп остановить нельзя все равно рано или поздно на передающей стороне возникнет переполнение, и данные потеряются, тогда зачем их перезапрашивать в данный момент ? или скорость обмена плис-плис заведомо гораздо больше скорости получения данных с ацп ? тогда 2,3 отпадают. Спасибо!

-

В 14.7 для этого нужно добавить .elf файл в проект ISE. Тогда получать .bit файл с обновленной программой можно перезапуском только bitgen'а.

-

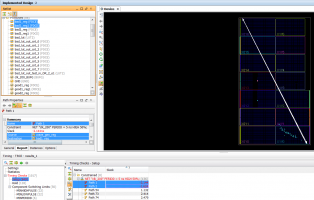

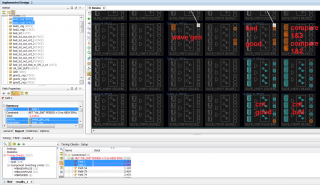

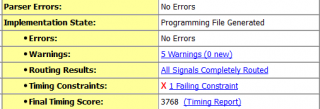

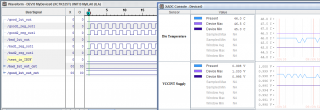

Добрый день! Необходимо показать, что нарушение временных ограничений приводит к неправильной работе схемы. Сделан простой проект для отладочной платы на Kintex 7: 1. генератор меандра на триггере 2. две параллельных цепи триггеров 3. сравнение значений на выходе триггеров 4. заданы временные ограничения (5 нс) и соответственно этому триггеры тактируются 5. один из триггеров вынесен максимально далеко от остальных для нарушения таймингов. 6. подключен chipscope для наблюдения ошибок и их подсчета В результате - по отчету тайминг нарушен (при разном размещении от 10 пс до 2 нс) а ошибки не возникают. Что сделано неверно ? Как максимально просто сделать такую демонстрацию ?

-

Одно "но" там ограниченная версия pcie ядра, часов на 12 по-моему.

-

Вопросы по Agilent ADS

toshas ответил Halo_Gen тема в RF & Microwave Design

Спасибо! Все оказалось несколько проще: 1. в модели требуемые параметры выбираем как user-defined, 2. включаем отображение параметров модели на блок-схеме, 3. создаем переменные и указываем их в параметрах требующих изменения, 4. создаем batch-controller с перебором по выбранным переменным -

Спасибо! Но TRD идет на ядре NW, а оно сильно дорогое. Интересует именно Axi Memory Mapped to PCI Express ядро.

-

попробуйте в 12.2 ядро перевести на virtex 6 и этот ngc используйте для 7ки в 14.6

-

Вопросы по Agilent ADS

toshas ответил Halo_Gen тема в RF & Microwave Design

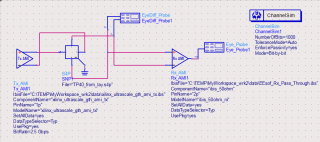

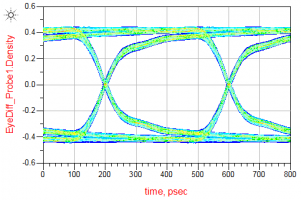

Спасибо за ответ. Модель имеет следующие параметры: (xilinx_ultrascale_gth_ami_tx (Reserved_Parameters (Init_Returns_Impulse (Usage Info) (Type Boolean) (Default False) (Description "Init_Returns_Impulse False")) (GetWave_Exists (Usage Info) (Type Boolean) (Default True) (Description "GetWave_Exists True")) (Use_Init_Output (Usage Info) (Type Boolean) (Default False) (Description "Use_Init_Output False")) (Max_Init_Aggressors (Usage Info) (Type Integer) (Default 2147483646) (Description "Max_Init_Aggressors 2147483646")) (Ignore_Bits (Usage Info) (Type Integer) (Default 0) (Description "Ignore_Bits")) (Tx_Jitter (Usage Info) (Type Float) (Format Gaussian 0 0) (Description "Tx_Jitter")) (Tx_DCD (Usage Info) (Type Float) (Format Value 0) (Description "Tx_DCD")) ) (Model_Specific (TXPRECURSOR (Usage In) (Type Integer) (Format List 0 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31) (Default 0) (Description "TXPRECURSOR")) (TXPOSTCURSOR (Usage In) (Type Integer) (Format List 0 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31) (Default 0) (Description "TXPOSTCURSOR")) (TXDIFFCTRL (Usage In) (Type Integer) (Format List 12 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15) (Default 12) (Description "TXDIFFCTRL")) (TX_PVT (Usage In) (Type Integer) (Format List 0 0 1 2) (Default 0) (Description "TX_PVT; 0 is typical corner, 1 = fast corner, 2=slow corner")) ) ) Как переменную связать с интересующим параметром ? (TXPRECURSOR/TXPOSTCURSOR/TXDIFFCTRL ) -

Вопросы по Agilent ADS

toshas ответил Halo_Gen тема в RF & Microwave Design

Добрый день! Подскажите как в ADS сделать перебор (sweep) параметров модели ? Есть IBIS-AMI модель передатчика, некий канал и заглушка-приемная модель (pass-through). Можно в ручную указывать пред- и пост- искажение источника, но это довольно утомительно, насколько я понял это можно вынести в переменную и сделать пакетную симуляцию (batch mode). Но как именно это сделать разобраться не могу и прошу помощи. Модели и тестовый проект (ADS2014) приложены. Спасибо! MyWorkspace_wrk2.rar -

Приемо-передатчики можно тактировать с внутреннего входа (со стороны логики ПЛИС), но этот путь не является рекомендованным. Посмотрите user guide на трансиверы.

-

Кто-нибудь измерял скорость получаемую на дизайне из xapp1171 ? Спасибо!