Alex77

Участник-

Постов

721 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Весь контент Alex77

-

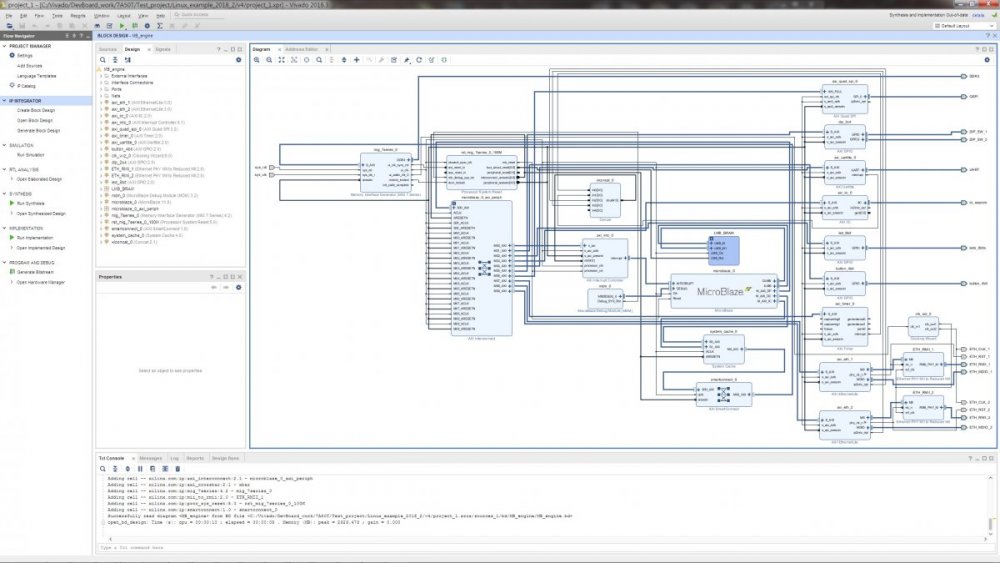

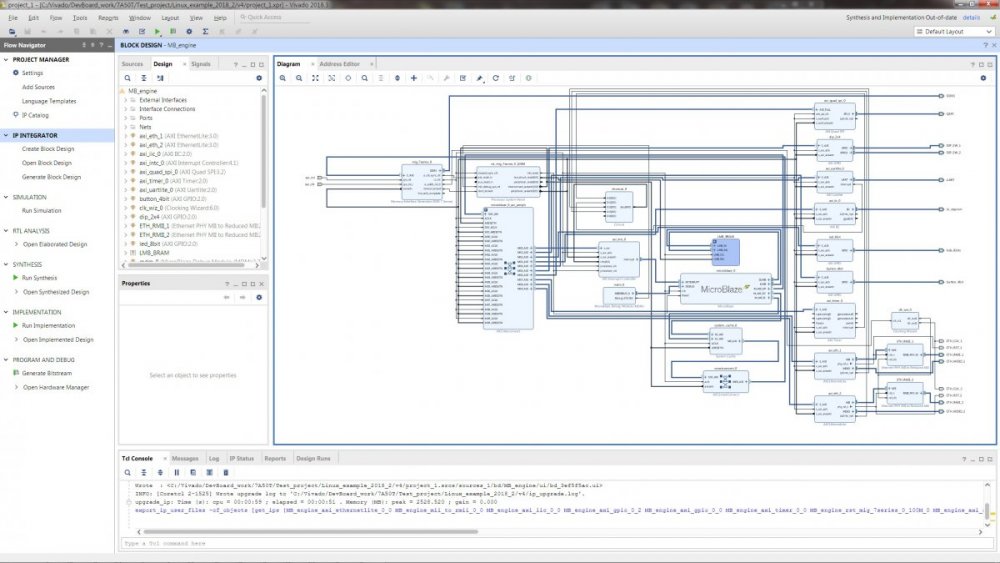

1) в вивадо рисуется схема с учётом реальных выводов. 2) из вивады делается экспорт хардваре+прошика плис в sdk, с последующим запуском sdk 3) в sdk "автоматом" должно сгенериться комплект дров для "вашей" схемы 4) создать демо проект по шаблонам. 5) если ничего не получается - то прочитать руководство пользователя в DocNav-e. их там море...

-

те отказаться от С++ ??? Дак кто ж на это пойдёто-то

-

Vivado 2019.1

Alex77 ответил Flood тема в Среды разработки - обсуждаем САПРы

Добавили микросхемы Vivado Design Suite 2019.1.1 is now available with support for Production devices enabled: Zynq UltraScale+ RFSoC (-2I, -2LI): XCZU39DR XA Kintex-7 (-1Q): XA7K160T XA Zynq UltraScale+ MPSoC (-1Q): XAZU7EV, XAZU11EG, XAZU7EG -

Vivado 2019.1

Alex77 ответил Flood тема в Среды разработки - обсуждаем САПРы

не успел... опередили. интернет в полях вялый -

процесс программирования это есть запись 0 на позицию 1. те каждый байт можно "шить" до восьми раз. как стирается именно эта микросхема я не знаю. аналогичные стираются только блоками по 64-256кб за раз или вся микросхема. процесс программирования обычно это запись во внутренний буфер микросхемы (256-512 байт) с последующим программированием соответствующих ячеек памяти.

-

однажды стертый блок (состояние все "FF") можно сколь угодно записывать информацией до состояния (состояние все "00") (Пример: было после стирания FF, записали первый раз 0x0f, и можно потом записать 0x00, апосля только стирание ). время стирания всего блока обычно равно времени полного программирования оного (точное время зависит от расположения звёзд). ПС: и запись не 1.2 микро а милисекунды.

-

А что вообще есть на "руках"? - схемы - описания - руководства - фото плат / изделия ???

-

увы с этим не сталкивался. как вариант это может быть нечто "электроника-60" ? так вроде такое уже делали на замену.

-

иии ??? или сиё есть великая тайна?

-

ну хотябы "маркировку" можно узнать вычислительного изделия (внутри которого 589 )?

-

И чишо ? В чём бонусы а кромя 10нм ? Хилые давно аналогичное клепают...

-

можно написать админам, они адекватны. там не явная регистрация - но она есть.

-

можно сходить на https://zx-pk.ru/threads/28952-pdp-11-na-fpga.html https://zx-pk.ru/threads/23978-tsifrovaya-arkheologiya-1801-i-vse-vse-vse.html и аналогичные там народ "творит" на плисах разные ретро процессоры, от любительского уровня до достойного. мож чего подскажут/найдёте интересного

-

ug949 глава 3 ???

-

Vivado 2018.3.1 и 2019.1

Alex77 опубликовал тема в Среды разработки - обсуждаем САПРы

вышло малое обновление Vivado Design Suite 2018.3.1 is now available with support for Enhancements in the IBERT IP and GT Wizard for Virtex UltraScale+ 58G Devices Production devices enabled: Virtex UltraScale+ HBM (-1, -2, -2L):- XCVU31P, XCVU33P, XCVU35P, XCVU37P Defense-Grade Zynq UltraScale+ MPSoC Devices:- XQZU11EG, Defense-Grade Kintex UltraScale+ Devices:- XQKU15P, XQKU5P Defense-Grade Virtex UltraScale+ Devices:- XQVU3P Defense-Grade Zynq UltraScale+ RFSoC Devices:- XQZU29DR The follow devices are introduced in this release: Zynq UltraScale+ RFSoC:- XCZU39DR XA Zynq UltraScale+ MPSoC Devices: -XAZU11EG (-1, -1Q), The following devices are introduced in WebPack: XAZU7EV, XAZU7EG For customers using these devices, Xilinx recommends installing Vivado 2018.3.1. For other devices, please continue to use Vivado 2018.3. И грядёт появление 2019. DocNav уже начал обновляться на 2019.1 -

философский вопрос: а к чему эта модель? для какого софта моделирования? там нет готового длл? или там есть рекомендации чем и как компилить? насколь я понимаю нужна длл для работы в виндах? в бытности при компиляции чего либо в либ или длл было важно соглашение по внутренниму представлению имён функций и способам передачи аргументов функциям. другими словами надо понять как это делает мингв и любой другой "современный" компилятор и постараться в новом компиляторе выставить нужные(правильные) опции компиляции.

-

а может посмотреть в сторону HLS Vivado ?

-

монитор 25' 2560*1440 90% и 125% ряд: 90, 100...300 шаг 25% что то мутно получилось загрузит рисунки. но тенденция видна. Шрифт получается чётким, не размытым.

-

Я не Гуру. Мои пять копеек. 1 - не надо путать "берега": блок-дизайн и язык описания схемы. Одно есть надстройка на другим. И для упрощения автоматизма блокдизайна "пожертвовали" типами данных. 2 - если выбирать из сей троицы - то SV. По моиму ИМХУ: vhdl - громоздкое описание (много букв, мало "смысла") verilog - это бета версия SystemVerilog. Например в SV более точно описано что и как инициализируется. Уточнены виды данных (переменные и цепи) и типы данных (те диапазон значений). Продвинутое тестирование. итд итд Так что мой выбор SV. 3 - а если посмотреть со стороны: все три языка идут "лесом", на фоне новых плис (для "аля ИИ") там наверно будут писать только на чемнибудь похожем на С++. другими словами (если проводить аналогии с программированием) это как АСМ и ЯВУ. Для толстых плис ЯВУ, а там где требуется "полировка" по ресурсам/быстродействию там vhdl/sv.

-

Размер шрифта в Vivado 2018.3 везде

Alex77 опубликовал тема в Среды разработки - обсуждаем САПРы

2018.3 tools-settings-display-Scaling (размер системы или в %) -

2018.3 tools-settings-window behavior ?

-

не хочу быть занудой, но: - xilinx НЕ разрабатывал устройство что расположено по выше указанной ссылке, и как следствие претензий к xilinx быть не может (так же санкции тоже не причём). - Вам достаточен тот корпус что есть в той " оркадовской либе" ? или там есть все разновидности корпусов (в частности для 020 это CLG400 и CLG484) - я не очень доверяю китайцам - тк проект самой плисы в примерах приведён на "отвали" и пестрит красными еррорами. - почему не посмотреть на оригинальные (от xilinx/digilent/avnet) демо платы на тамошнее описание (требования) к разводке pcb ? а так же как разведено питание, память и др.

-

а разве есть оригинальные киты для xc7z010s ??? для 020 есть, а для 010 нету. Посему где облом? а то что найдено - так это галимый китай. а китайцы никому (так просто) не отдают...

-

а что собственно мешает использовать вивадо? в древней исе там даже плисы цинк были ещё инженерными образцами...