[email protected]

Участник-

Постов

12 -

Зарегистрирован

-

Посещение

-

А как это сделать? Подскажите

-

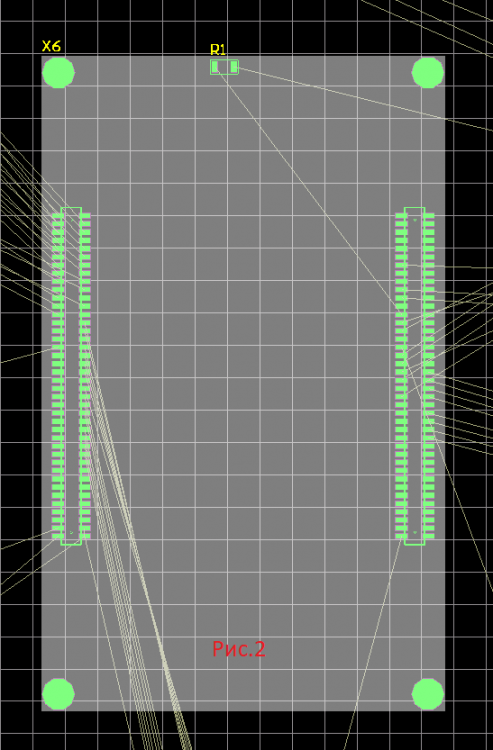

Привет всем! Сделал ПМ для некой платы через штыревые разъемы (Рис. 1). Т.е. на основной плате два ряда штырьевых разъемов в которые будет вставляться другая плата. В зазор между устанавливаемой платой хотелось бы установить SMD компоненты. Но когда помещаю компонент в область под устанавливаемой платой получаю предупреждение (рис 2) (компоненты пересекаются). Подскажите как с этим быть?

-

Спасибо всем за помощь!

-

Ну, пожалуй у меня последний вопросик: По объему изучения эти языки большие? сравнимо, грубо, с Си (Си++) или что-то среднее меджу Си и ассемблер?

-

К сожалению, в связи с тем что только осваиваю ПЛИС, не все понял. Надеюсь в ближайшее время смогу полностью постичь о чем Вы написали. Но Ваши настроения по поводу VHDL уловил)) На Ваш взгляд какой язык выглядит более перспективным. Лазя по интернету складывается ощущение, что VHDL медленно уступает место Verlog и System Verilog (возможно мне только показалось). Ну соответственно почему Вы выбрали SV, а не просто Verilog? В чем их отличия?

-

На счет ModelSim согласен с Вами, там все гораздо быстрее получается. И да, дизайн ModelSim убогий и нелогичный. Vivado только начал осваивать. На счет "В Vivado для блок дизайна есть готовые элементы...." не совсем понял. Если речь идет счетчиках, сумматорах и прочих стандартных элементах, то мне это сейчас ненужно, т.к. в данный момент я осваиваю именно VHDL. Раз уж тут все так весело понеслось)) еще один вопрос не по теме. Вопрос к опытным разработчикам ПЛИС. Что же выбрать на перспективу VHDL, Verilog или System Verilog? Стандартный ответ о Си подробности Верилогов, его лаконичности и консерватизма VHDL становится ясно из учебников и большинства статей о ПЛИС. Интерисует больше о перспективности... и кто из них более оптимален с чтоки зрения используемых ресурсов ПЛИС. Может еще какие особенности?

-

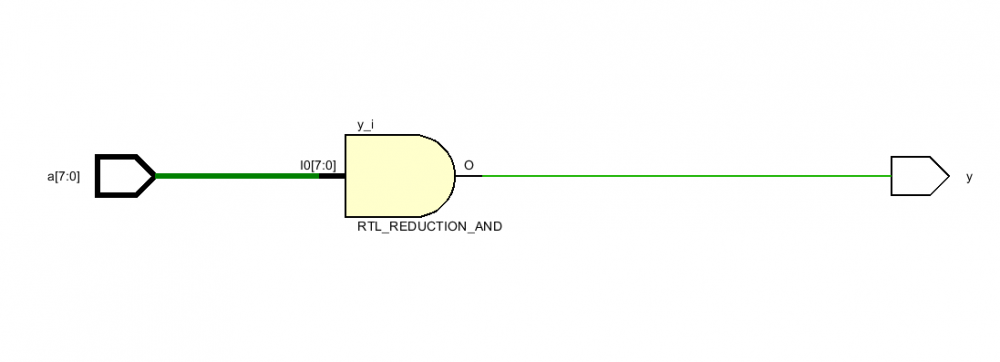

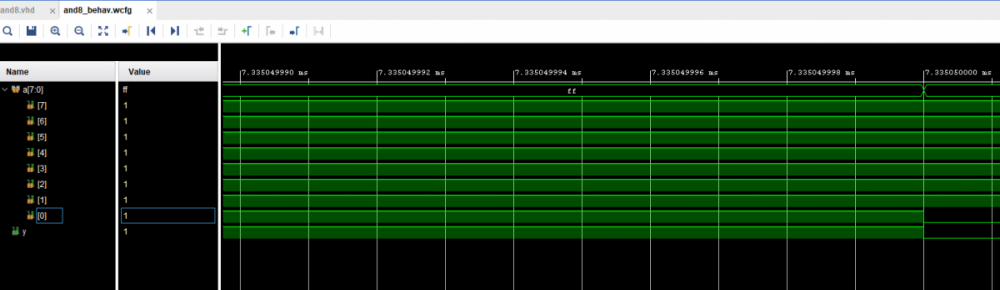

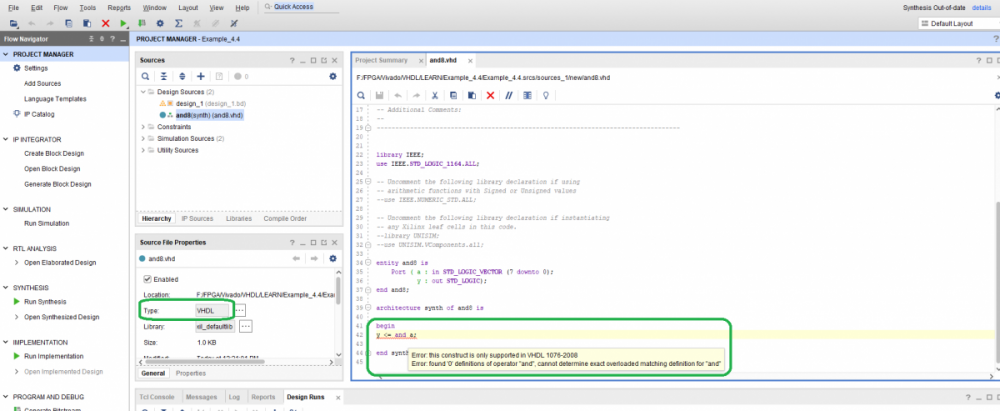

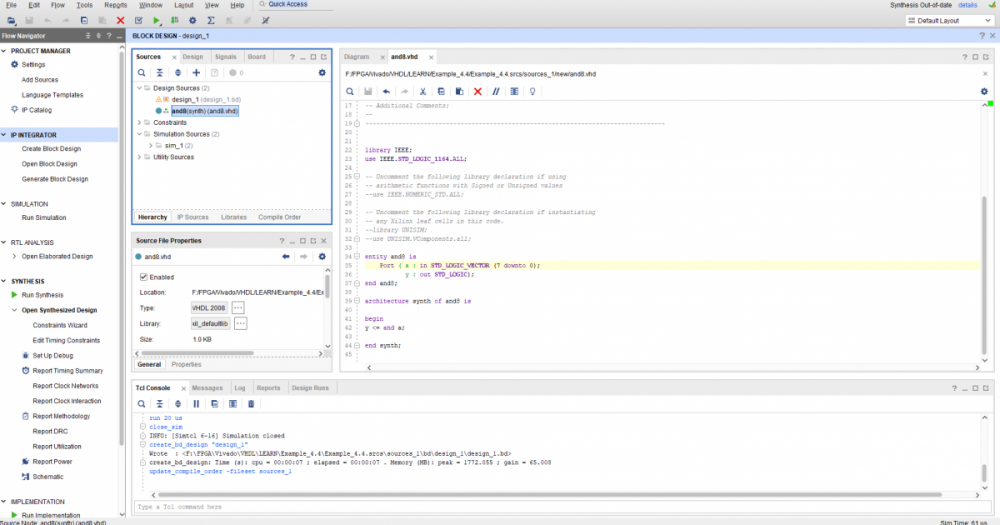

Кажется нашел приемлемое решение проблемы Написал модуль inv8 на VHDL (93), игнорируя ошибку Error ..... . Вставил в графический дизайнер модуль (inv8). Затем, в настройках inv8.vhd уставил язык VHDL 2008. Выглядит и работает как 8-и входовой И. Вроде норм. В симуляции, RTL анализе и сгенерирован битстрим.

-

Возможно я немного некорректно выразился с фразой "VHDL 2008 необходим для описания 8-и входового И". Дело в том что я повторяю примеры приведенные в небезызвестной книге "Цифровая схемотехника и архитектура компьютера" второе издание Дэвид М. Хэррис и Сара Л. Хэррис. Пример 4.4. Восьмивходовой И. Чтобы запустить проект и в Vivado или ModelSim требуется в настройках устанавливать именно VHDL 2008. Т.е. для меня без вариантов... или VHDL 2008 без графического дизайна либо VHDL 1993? Вариантов больше нет? Т.е. для меня без вариантов... или VHDL 2008 без графического дизайна либо VHDL 1993? Вариантов больше нет?

-

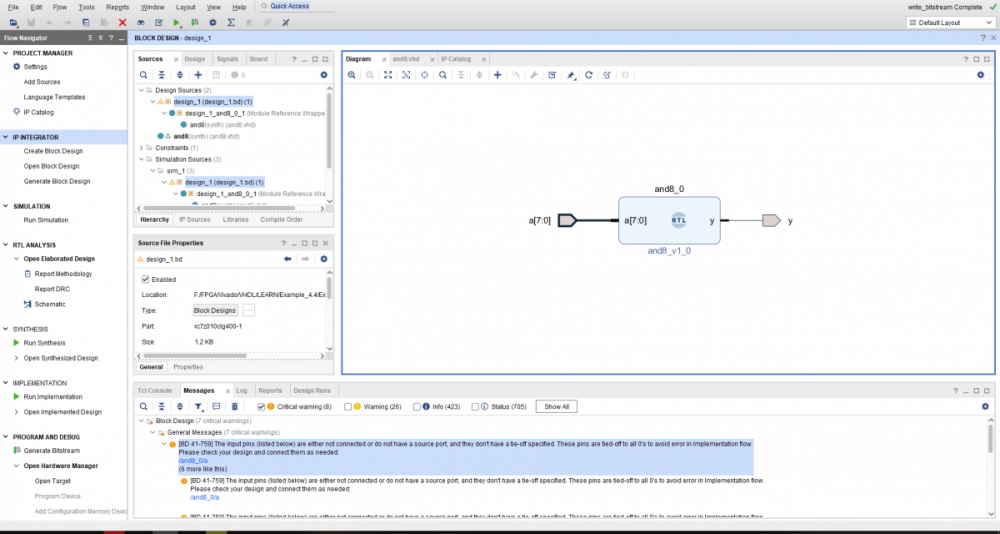

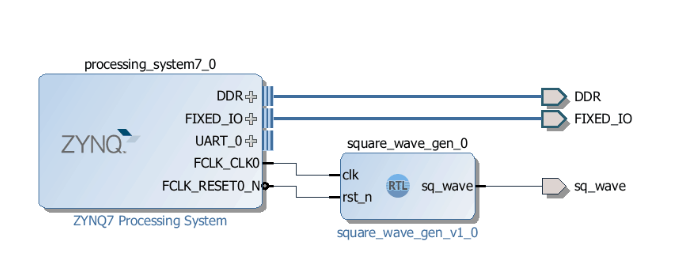

Если честно может и не нужен. Я только осваиваю ПЛИС. У меня плата Z-turn board с м/с Zynq-7000. В примерах которые я нашел в интернете описается единственный способ заактировать ПЛИС (PL часть) от внутреннего ARM процессора (PS). Что бы это сделать нужно в графическом дизаейнере добавить IP блок - Zynq7 Process System туда же добавить мой модуль (and8) уже от PS получать clk. Это выглядит примерно как на картинке ниже. Да и наглядно и более ясно это делать в графическом виде.

-

-

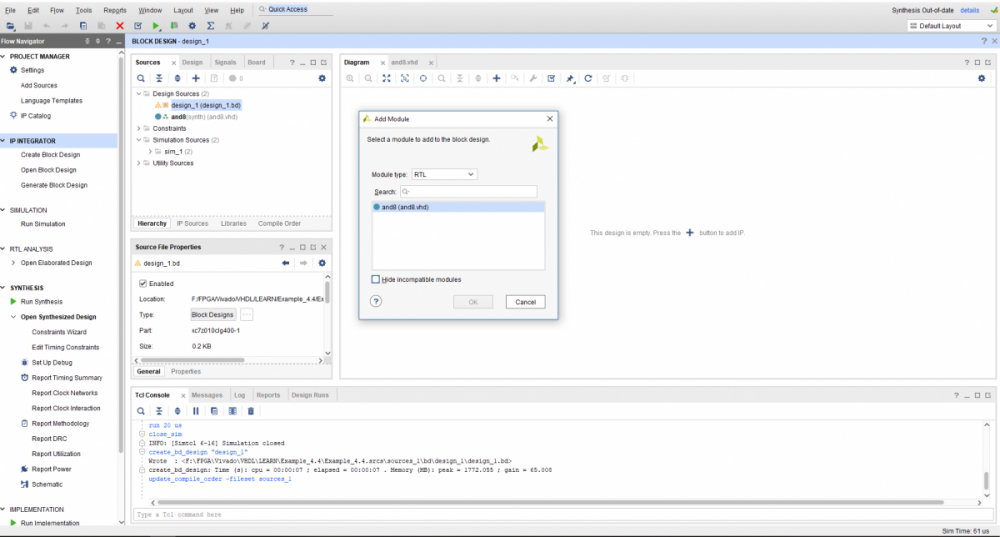

Поддержка VHDL 2008 включена в файле and8.vhd (на второй картинке видно Type: VHDL 2008). Проблема в том, что я не могу файл and8.vhd (с указанным в настройках VHDL 2008) добавить в окно графического дизайнера...

-

Vivado поддержка VHDL 2008

[email protected] опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день, всем! Недавно начал осваивать ПЛИС. В качестве HDL выбрал VHDL. ПЛИС ф. Xilinx, среда разработки Vivado 2018.3 Столкнулся со сложностью: при описании в Vivado модуля на VHDL 2008 невозможно добавить этот моль в IP integrator (окно Diagram см. рисунок во вложении) т.к. кнопка OK не активна. При использовании VHDL (не 2008) проблем не возникает. Из информации в интернете не совсем понятно, что делать. Кто-то пишет, что невозможно добавить модуль описанный на VHDL 2008 в IP integrator. В документации же написано что есть поддержка VHDL 2008. Знающие подскажите что делать?В данном же примере VHDL 2008 необходим для описания 8-и входового И (y <= ana a).