Alex_vod

Свой-

Постов

121 -

Зарегистрирован

-

Посещение

Весь контент Alex_vod

-

fdatool в MATLab

Alex_vod ответил KolyanV тема в Вопросы системного уровня проектирования

Спасибо !! Да вы правы , всё дело как раз в блоке , который будет расчитывать коэффициенты. Думал всё будет проще с адаптивной фильтрацией. Буду копать дальше. -

fdatool в MATLab

Alex_vod ответил KolyanV тема в Вопросы системного уровня проектирования

Понятно , жалко что нельзя Подскажите, пожалуйста есть ли возможность в матлабе сгенирить на автомате VHDL код, без использования FDATool. Скажем если я воспользуюсь функцией equalize, можно ли получить фаил фильтра на VHDL? -

fdatool в MATLab

Alex_vod ответил KolyanV тема в Вопросы системного уровня проектирования

Подскажите, можно ли в Матлабе (FDATool) собрать фильтр выполняющий адаптивное выравнивание сигнала. Если можно , то какой тип фильтра нужно использовать. -

Адаптивное выравнивание

Alex_vod ответил Alex_vod тема в Математика и Физика

Да , но как эти фукции использовать в FDATool , что бы сгенирить на автомате VHDL код -

Адаптивное выравнивание

Alex_vod опубликовал тема в Математика и Физика

Подскажите, можно ли в Матлабе (FDATool) собрать фильтр выполняющий адаптивное выравнивание сигнала. Если можно , то какой тип фильтра нужно использовать. -

констрейны в Квартусе

Alex_vod ответил rv3dll тема в Среды разработки - обсуждаем САПРы

Quartus II Version 7.0 Handbook . правда не на русском. Посмотрите I/O Register Packing страница 110 (это набор правил, как лучше) , мне помогло , поэтому дальше копать не стал. Ещё можно посмотреть Signal Integrity Analysis with Third-Party Tools, но там всё серьёзно, стр 1753 -

Спасибо Boris_TS за схемку Конечно же Вы правы, кажый может делать схемы по своему, так и делаем. Интересны ИДЕИ !!!! А уж применять их или нет , дело каждого. Я так думаю

-

А нарисовать можно, то о чём вы спорите. У меня как раз 10 битовая АЦП на 32 мегагерца и плисс Cyclone II. Второй день экспериментирую с приёмом данных с АЦП. Если будет рисунок"схемма" ваших идей , я смогу сразу протестить её на своей плате.

-

Я пока пишу в AHDL и только собираюсь переходить на Verilog, а с VHDL не знаком вовсе.А то что то сложно за Вашими мыслями угнаться. Думаю не я один такой. Вы бы не могли рисунками показывать свои идеи, ведь схемы не сложные, да и наглядней получается. Простота ведь она сестра таланта и понятно всем станет........ и интересно.

-

Если все тактируемые схемы ведут себя странно - то дело скорее всего в разводке рлаты... Есть такой термин - Signal Integrity. Обратите на него пристальное внимание - для клоков он особенно критичен. спасибо , сейчас бегло просмотрел в quartusii_handbook, штука интересная. Раньше об этом не знал. Вечерком попробую разобраться что к чему.

-

Да действительно , не конкретный вопрос я задал ... Плисс у меня Cyclone II. Я знаю у этих микросхемм есть специальные выводы тактовых частот наружу. Называются они в документации PLL<#>_OUT, привязываются они к специальным ногам плисы. Но при разводке платы я это не учел. Если просто подавать Global Clock на выход плис,то получается криво... мы имею не только плохую частоту на выходе плисс, но и все схемы тактируемые этим Global Clock ведут себя странно. Наверное лучше спросить по другому . Можно ли сигналы Global Clock выводить наружу плис без специальных выводов. Если можно то как?

-

Раз уж тема о проблеммах синхронизации, хотелось бы узнать ваше мнение по поводу использования глобальных частот. Думаю эти вопросы возникают у многих. Как вы считаете можно ли глобальную тактовую частоту подавать на ногу ввода вывода? Например в РLL частота умножается да 60 мегагерц. Могу ли я эту частоту подать на выход ПЛИС??

-

Я согласен с Вашими замечаниями... В этом вопросе так глубоко не копал (распределение вероятности, экспонента,метастабильность.... сложные вопросы) Приведённая мной схема очень проста , но в большенстве случаев работает. Тогда может вы подскажите другое решение. Что лучше использовать при приёме данных? Какую схему используете вы?

-

"то не синхронизация, а rise detection. При приходе асинхронного сигнала бесполезна." тогда как же поступают при приходе асинхронного сигнала, что бы вписать его в синхронную систему???

-

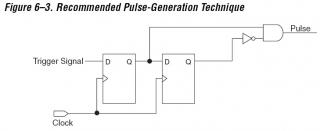

В своё время многие проблеммы с синхронизацией решила вот такая простенькая схемма. Нашёл её в quartusii_handbook Все триггеры в проекте тактируются глобальной тактовой. А на вход разрешения триггера(ENA) подается с выхода этой схеммы. Т е это просто схемма укорочения импульса, синхронная!!!

-

Подскажите , корректно ли с выхода PLL глобальную тактовую выводить на ножки I/O, для того что бы тактировать соседнию с FPGA микросхему. Никто не сталкивался с проблеммами в этом случае?

-

А..теперь понятно для чего это нужно Сам использую только FPGA Altera. Поэтому пока заморачиваться со стороним синтезом не буду. Спасиб , что объяснили.

-

"Основные тормоза это фиттер с глыбокими физическим ресинтезом, ретаймингом, репликацией и прочей оптимизацией. А синтезатор вполне шустрый, особенно если инкрементальная компиляция ему разрешена." Полностью с Вами согласен. Время синтеза в несколько раз меньше времени затраченного на фиттер. Прочитал тему, но так и не понял для чего использовать модули синтеза сторонних разрабочиков????? А если так важно время компиляции, то может стоит именно это обсуждать, например настойки проэкта на разных этапах разработки. Как Вы думаете?

-

fir_compiler-v3.3.0

Alex_vod ответил shpilya тема в Среды разработки - обсуждаем САПРы

В соседней теме на форуме встретил "строки в лицензию", но почему то fir_compiler работать не захотел. Ни как не получается заставить fir_compiler работать. На ФТР доступа у меня нет. Очень нужно поэксперементировать с параметрами фильтра. Если не затруднит, вышлите исходники на мыло. [email protected] Заранее Спасибо !! -

xDSL

Alex_vod ответил Alex_vod тема в ISDN/G.703/E1

"Вообще-то непонятно, зачем сегодня возвращаться к коду 2b1q" 2b1q это самое простое начало, частный случай технологии PAM, а проблемма понижения частоты до сих пор актуальна. Проблемма которую я описал в начале темы , практически решена. Спасибо ВСЕМ кто откликнулся и что то посоветовал. В итоге оказалось что достаточно поставить цифровой фильтр на приёме, который подавляет низкие частоты. Теперь отфильтрованный сигнал легко детектировать. Но возникла другая трудность, с синхронизацией и подавлениенм джитера. -

Постоянная состовляющая

Alex_vod ответил Alex_vod тема в Математика и Физика

но если априори не создавать этих ситуаций с постоянкой. Вы имеете в виду изменять последовательность?" в скремблере и дескремблере согласно рекомендациям МСЭ-Т предусматриваются специальные дополнительные схемы контроля, которые выявляют наличие периодичности элементов на входе и нарушают ее." Пробывал , только очень сложно всё получается. Да и в стандарте это не прописанно. -

xDSL

Alex_vod ответил Alex_vod тема в ISDN/G.703/E1

Нет, не ПСП, на вход подаётся просто Е1 сигнал, в котором есть только синхрогруппа(0 канальный интервал, другие КИ не задействованы) Пробывал разные последовательности передавать : и все единицы и все нули и ПСП, результат тот же. "Второй недостаток СС скремблера связан с возможностью появления на его выходе при определенных условиях так называемых критических ситуаций, когда выходная последовательность приобретает периодический характер с периодом, меньшим длины ПСП. Чтобы предотвратить это, в скремблере и дескремблере согласно рекомендациям МСЭ-Т предусматриваются специальные дополнительные схемы контроля, которые выявляют наличие периодичности элементов на входе и нарушают ее." Тоже пробывал. Но в стандарте это не прописанно. Очень сильно усложняет схему, трудно реализовать. -

Постоянная состовляющая

Alex_vod ответил Alex_vod тема в Математика и Физика

"Тестеры каналов передачи данных ( BER-тестеры)", если вы это имеете в виду. Не пробывал мерить приборами, потому как распознаётся сигнал с ошибками, которые множаться при дескремблировании -

Постоянная состовляющая

Alex_vod ответил Alex_vod тема в Математика и Физика

Вероятность пояаления такой комбинации 2^23 Эта последовательность изменяет постоянную составляющию, "уводя" сигнал то ыыерх , то вниз. -

Постоянная состовляющая

Alex_vod ответил Alex_vod тема в Математика и Физика

" скремблер и дескремблер воткнуть нельзя по соображениям ТЗ?" скремблер и дескремблер давно стоят , какие рекомендует стандавт G0991. А то что на картинки , это фрагмент случайной последовательности