Alex_vod

Свой-

Постов

121 -

Зарегистрирован

-

Посещение

Весь контент Alex_vod

-

Нужно посмотреть на нововведения, любопытно. Есть мысли про HLS (High Level Synthesis)? Полетит или не полетит? Заменит Verilog или будет как дополнение к разработке? Вообще стоит обращать внимание на HLS?

-

Quartus & SignalTap

Alex_vod ответил nice_vladi тема в Среды разработки - обсуждаем САПРы

можно создать тестовые регистры(на глобальной тактовой) и на них завести нужные вам сигналы, а тестовые регистры вывести в Signal Tap -

Да , точно, если исполняемый код, это только чтение просто не силён в процессорах и терминологии, присматриваюсь пока

-

Флешь всегда имела ограниченное число циклов записи, например 100 000 циклов, дальше выходит из строя. Исполняя код во флешки вы её по идеи сломать должны, не сразу а со временем. Может что то изменилось сейчас?

-

Рекурсивный цифровой фильтр

Alex_vod ответил student58 тема в Алгоритмы ЦОС (DSP)

Привет "Подскажите, пожалуйста, для чего рекурсивному филтьру запоминать предидущие значения?" Хранить предыдущие значения необходимо для того что бы вычислить текущее значение. "Или может на пальцах объяснить как работает рекурсивный фильтр." Если на пальцах, то на картинке это правая область. Вы храните, работаете уже с вычисленными значениями. Получается бесконечный цикл. "Я преподователю говорю, что фильтр проходит по каждой точке, умножает её на некоторый коэфициент и суммирует с предидущеми уже вычислинными точками (умноженные на другой коэфициент)" Почти правильно, только не фильтр проходит , а сигнал не некоторый , а заданный, рассчитанный суммирует с предидущеми уже вычислинными точками вот их вам и надо сохранить. "Но зачем всё это - я не понимаю" Эти фильтры имеют хорошие характеристики и малые вычислительные затраты, поэтому их и используют. Единственный недостаток БИХ фильтров это нелинейность фазы. "Пожалуйста объясните." Это не простая тема, сильно не огорчайтесь. Попробуйте подать на фильтр единичный импульс и расписать все состояния, шаг за шагом, можно использовать табличный редактор типа Excel. Я когда разбирался так и делал. Так же поможет программа для расчёта БИХ фильтров и построения импульсной характеристики, что бы сравнивать вычисленные значения сигнала. ____________dfilt1.pdf -

Задержка в КИХ фильтре

Alex_vod ответил NikSave тема в Алгоритмы ЦОС (DSP)

Как посчитать задержку вносимую фильтром Реакция Ких фильтра 1-2 такта частоты дискретизации при изменении положения центрального отвода у вас измениться характеристики фильтра, полоса пропускания и т д, так делать нельзя. Посмотреть реакцию Ких фильтра можно подав на него синус нужной вам частоты и посмотрев на его реакцию, сравнив со входом можно ещё поиграть в Matlab FDA Tool там есть методы расчёта КИХ фильтров с минимальной фазой (minimum-phase filter), например Constrained Least Squares но у этих фильтров характеристики похуже и требуют больших ресурсов для обработки, коэффициенты у них не симметричны -

Я бы попробовал запустить вначале Арию, затем Макс, и только потом связку Ария+Макс. Второй разъём JTAGа можно навесным монтажом времено прилепить, что бы дорожки и плату не портить.

-

Будет жаль если Intel окончательно испортит Альтеру а потом забросит этот проект. С активным "продавливанием" OpenCL шаги в этом направлении ведутся уже давно. А вообще странно что Альтера не купила себе Intel, думаю они тоже могли бы себе это позволить, FPGA сегодня завоёвывает активно рынки микросхем и у них большое будущие и без Intel. В общем похоже что это начало конца Альтеры.

-

Spectra-Q вообще зверь какой то новый C or C++ based—The Spectra-Q engine supports Altera’s new A++ Compiler for high-level synthesis to create IP cores from C or C++, which significantly boosts productivity through faster simulation and IP generation. вот зря Altera убрала поддержку старых семейств(2-3 циклонов), "потрогать" новый Q15 по настоящему не получается.

-

А для чего вы используете BluePrint и чем он так хорошо? если не секрет, интересно Я пока так и не нашёл применения "раннего планирования" в разработках

-

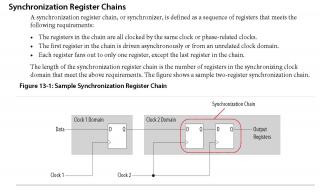

Если входные сигналы принадлежат другому клоку , может возникнуть метастабильность, поэтому лучше удалить логику между 1 и 2 триггером quartusii_handbook 14.1 стр 810 А еще лучше "привести" сигналы к единой тактовой , и только затем добавлять логику Если входные сигналы уже были "регистрированы" вашей clk и схема работает на clk , тогда всё должно быть нормально (конечно если тайминг анализ не ругается)

-

А в чём падение производительности, где подвох? Я думал М10 это С4 урезанный. (да понимаю тема про Q14 и сообщение немного не по теме)

-

Интересовало просто мнение, это перспектива, дальнейшие развитие или маркетинговый ход, а может просто технологию пытаются «притянуть за уши» к FPGA. Старую лицензию попробую на выходных, а вот новую(более полную) не встречал пока. Если у кого есть поделитесь плиз.

-

А есть какие нибудь мнения по поводу OpenCL?

-

Я не гуру, но близкой темой занимался, самому интерестно мнение знающих , умеющих. 1 фильтры типа RRC(приподнятый косинус) приемный и передающий являютя согласоваными, работают в паре, их цель сформировать "особенный" спектр сигнала который меньще подвержен искажениям, в общем согласование линии. " Я так понимаю в такой схеме отпадает необходимость в приемном канальном фильтре в ПЛИС, т.к. сигнал уже профильтрован во внешнем DDC. Так ли это?" нет не отпадает т к оба фильтра работают в паре. 2 ФНЧ фильтр обычно для подавления шумов в канале. Полоса пропускания его должна быть больше полосы RRC фильтров. а вот какой лучше всего выбрать для меня самого вопрос открытый. Inverse Sinc у меня показал лучший результат, позже хочу заменить на адаптивный. В общем этот фильтр тоже нужен. на вашем месте я бы все оставил как есть

-

Да, спасибо за подсказку, я так и сделал. только все равно непонятно, для чего в PADS Layout есть настройки принтера

-

Добрый день Подскажите пожалуйста, как можно в PADS Layout выводить pcb, или часть pcb на печать Например в P-CAD есть возможность выбрать нужную часть платы, задать необходимые слои и вывести на печать (например что бы монтажникам было лучше видно что и как переделать) Есть ли такая возможность в PADS Layout?

-

"Может у вас win32?" да у меня win32 стоит спасибо за подсказку теперь попробую перейти на win64 правда в официальном "quartusii_handbook" нет ни слова про "setenv"

-

"addpath(genpath('C:\altera\11.1\quartus\bin64')); alt_signaltap_run" не работало потому что MATLAB win64, с win32 должно работать если не секрет как вы нашли команду "setenv"? спрашиваю потому что у меня не получалось запустить signaltap + MATLAB win64

-

если у вас Altera и Quartus то запустите в программе Quartus PowerPlay Power Analyzer, этот анализатор сгенирит отчет в котором все видно. Я для интереса мерил тестером токи потребления у плисс , PowerPlay Power Analyzer все правильно оценил.

-

посмотрите документ wp279 Digitally Removing a DC Offset: DSP Without Mathematics Google ищет в лёт Лучше и проще способа я не видел

-

Интересно, почему Altera на свой FTP сервер Quartus v11.1 не выкладывает?

-

Появился Quartus 10.0

Alex_vod ответил _AM_ тема в Среды разработки - обсуждаем САПРы

теперь понятно спасибо -

Появился Quartus 10.0

Alex_vod ответил _AM_ тема в Среды разработки - обсуждаем САПРы

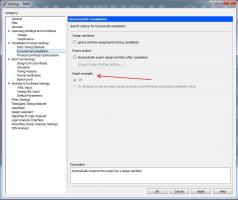

у меня полная версия, правильная"dll" и лицензия, а rapid recompile работать не хочет я так понимаю что rapid recompile повышает скорость компиляции проекта пробовал и 32 и 64 бита, все равно закрыто у кого нибудь работает rapid recompile ? -

Появился Quartus 10.0

Alex_vod ответил _AM_ тема в Среды разработки - обсуждаем САПРы

кто нибудь пробовал запустить или включить rapid recompile у меня не получается, может это тоже с лицензией связано?