-

Постов

484 -

Зарегистрирован

-

Посещение

Весь контент MaratZuev

-

Всем спасибо, пошёл душиться )

-

Эквивалентны ли два модуля?

MaratZuev опубликовал тема в Языки проектирования на ПЛИС (FPGA)

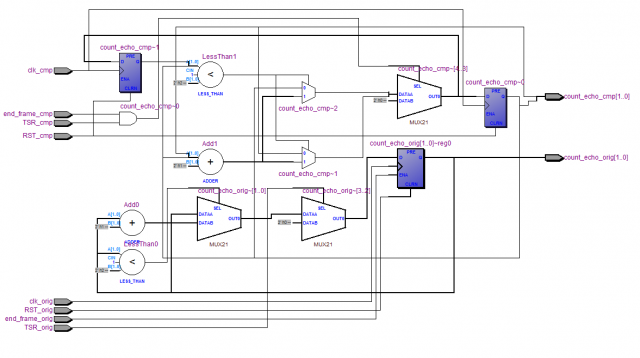

Доброго всем. Прошу простить за кому-то очевидный вопрос, но мне хотел бы прояснить... Я переписал доставшийся мне по наследству кусок кода always_ff @(posedge clk_orig or posedge RST_orig) if (RST_orig) count_echo_orig <= 2'h0; else if (end_frame_orig) if (TSR_orig) count_echo_orig <= 2'h0; else if (count_echo_orig <= 2'd2) count_echo_orig <= count_echo_orig + 2'd1; В таком виде: always @(posedge clk_cmp or posedge RST_cmp) count_echo_cmp <= RST_cmp ? 2'h0 : end_frame_cmp && TSR_cmp ? 2'h0 : count_echo_cmp <= 2'd2 ? count_echo_cmp + 2'd1 : count_echo_cmp; Но гложут сомнения, что не всё чисто. Попробовал спросить Quartus RTL-Viewer отобразить всё сразу: module cmp ( input logic clk_orig, clk_cmp, input logic RST_orig, RST_cmp, input logic end_frame_orig, end_frame_cmp, input logic TSR_orig, TSR_cmp, output logic [1:0] count_echo_orig, count_echo_cmp ); always_ff @(posedge clk_orig or posedge RST_orig) if (RST_orig) count_echo_orig <= 2'h0; else if (end_frame_orig) if (TSR_orig) count_echo_orig <= 2'h0; else if (count_echo_orig <= 2'd2) count_echo_orig <= count_echo_orig + 2'd1; always @(posedge clk_cmp or posedge RST_cmp) count_echo_cmp <= RST_cmp ? 2'h0 : end_frame_cmp && TSR_cmp ? 2'h0 : count_echo_cmp <= 2'd2 ? count_echo_cmp + 2'd1 : count_echo_cmp; endmodule : cmp Но то, что я увидел сразу понять не могу: то это или не то. Посему прошу помощи зала .. -

Внимание вопрос: help читать не пробовали?

-

Спасибо, конечно, но что мне даст изучение ещё одного инструмента, когда я и с помощью имеющегося у меня успешно достигну той же цели? Просьба рассматривать сей вопрос не как риторический, но как практический.

-

Простой вопрос про инкремент

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Всем добра. Столкнулся с непонятной мне вещью: logic reset; logic [5:0] cnt; always_ff @(posedge clk) begin cnt <= reset ? '0 : cnt + 1; end Работает, но always_ff @(posedge clk) begin cnt <= reset ? '0 : cnt++; end нет. Отсылка к стандарту или куда-либо ещё приветствуется. -

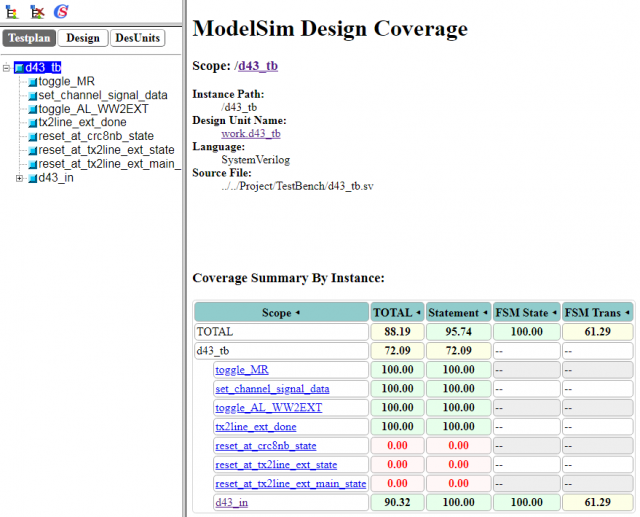

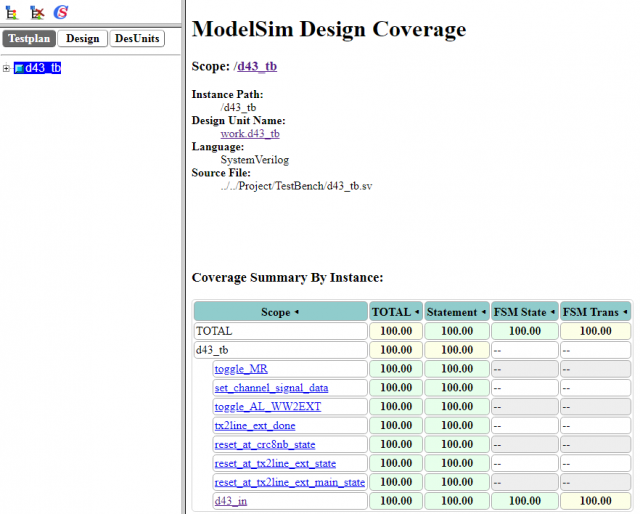

Да, к сожалению, задача ставится именно так: цейтнот + непонятно какие требования со стороны проверяющих, ибо мы в своей отрасли, afaik, являемся первопроходцами, которых жестоко подгоняют со всех сторон. Я понимаю, что торить дорогу, да и просто идти надо правильно, чтобы и сам и идущие следом не спотыкались, но.. Как говорит тесть "Будем работать!". https://opencores.org/projects/ethmac ? Да, есть желание быть и тем и тем, посему спасибо вам за развёрнутый ответ. Фраза, хорошо известная всем согражданам: "В КАКОЙ стране живём?!" Легко. Вот отчёт неполного покрытия: А вот - полного:

-

Если их не может быть в принципе, то почему верификатор об этом не знает? Да, спасибо. Пошёл читать..

-

Да, как говорит мой коллега с прошлой работы: "Интересная картина: голой женщины портрет!" Спасибо!

-

Спасибо! Этот болт мне нравится больше всего. Странно только, что на такой же болт но с меньшим количеством витков dut.state.last() + dut.state.first() ModelSim ругается: # ** Error (suppressible): (vsim-8386) dut_tb.sv(37): Illegal assignment to type 'dut_tb.dut.enum int ' from type 'bit signed[31:0]': An enum variable may only be assigned the same enum typed variable or one of its values. С чего бы это?

-

Я уже не знаю, кому отвечать! Но до сих пор не могу взять в толк, в чём моя проблема? dut.sv typedef enum {ST_IDLE = 0, ST_INIT = 1, ST_ADDR = 2, ST_DATA = 3, ST_CRC8 = 4, ST_PULS = 5} state_t; state_t state; Вариант 1 dut_tv.sv 34 initial begin 35 force dut.state = dut.state'(6); 36 #10ns release dut.state; 37 end ModelSim # ** Error: (vsim-8220) dut_tb.sv(35): This or another usage of 'dut.state' inconsistent with 'register' object. # Time: 0 ps Iteration: 0 Instance: /dut_tb File: dut_tb.sv # ** Error: (vsim-3044) dut_tb.sv(35): Usage of 'dut.state' inconsistent with 'register' object. # Time: 0 ps Iteration: 0 Instance: /dut_tb File: dut_tb.sv Вариант 2 dut_tv.sv 34 initial begin 35 force dut.state = dut.state_t'(6); 36 #10ns release dut.state; 37 end ModelSim # ** Error: (vsim-8220) dut_tb.sv(35): This or another usage of 'dut.state_t' inconsistent with 'typedef' object. # Time: 0 ps Iteration: 0 Instance: /dut_tb File: dut_tb.sv # ** Error: (vsim-3044) dut_tb.sv(35): Usage of 'dut.state_t' inconsistent with 'typedef' object. # Time: 0 ps Iteration: 0 Instance: /dut_tb File: dut_tb.sv # ** Error (suppressible): (vsim-8386) dut_tb.sv(35): Illegal assignment to type 'dut_tb.dut.enum int ' from type 'bit signed[-1:0]': An enum variable may only be assigned the same enum typed variable or one of its values. # Time: 0 ps Iteration: 0 Instance: /dut_tb File: dut_tb.sv Готов признать себя тупым, только подскажите ЧЯДНТ?!

-

Всем добра. Продолжаю заниматься покрытием кода для разных своих и не только проектов, и вот возник философский вопрос. До сих пор моё покрытие вычислялось так: я брал testbench, наращивал его потихоньку, чтобы покрыть всё, что мне нужно, и в конечном итого получал большой testbench, в котором инстанциирован главный модуль проекта, состоящий, в свою очередь, из подмодулей. Так вот вопрос: а могу ли я "обработать" другим testbench-ем не весь проект, а подмодули, чтобы в конечном итоге получить полное покрытие? Бред говорю?

-

Боюсь показаться тупым, но как это будет выглядеть для enum {ST_IDLE, ST_INIT, ST_ADDR, ST_DATA, ST_CRC8, ST_PULS} state; ? Увы и ах: dut.sv: 9 enum {ST_IDLE = 0, ST_INIT = 1, ST_ADDR = 2, ST_DATA = 3, ST_CRC8 = 4, ST_PULS = 5} state; dut_tb.sv: 34 int state; 35 36 initial begin 37 state = 6; 38 force dut.state = state; 39 #10ns release dut.state; 40 end ModelSim: # ** Error (suppressible): (vsim-8386) ../../Project/dut_tb.sv(38): Illegal assignment to type 'dut_tb.dut.enum int ' from type 'int': An enum variable may only be assigned the same enum typed variable or one of its values. # Time: 0 ps Iteration: 0 Instance: /dut_tb File: ../../Project/dut_tb.sv # Error loading design # Error: Error loading design Разве есть не является подтасовкой результатов? Ведь так я могу и весь код исключить, чтобы лишней, как по мне, работой не заниматься!

-

34 initial begin 35 force dut_main.dut_module1.state = default; 36 force dut_main.dut_module2.state = default; 37 #10ns release dut_main.dut_module1.state; 38 release dut_main.dut_module2.state; 39 end Даёт: # ** Error: (vlog-13069) ../../Project/dut_tb.sv(35): near "default": syntax error, unexpected default. # ** Error: (vlog-13069) ../../Project/dut_tb.sv(36): near "default": syntax error, unexpected default. Могу я как-то смоделировать это?

-

FSM или как попасть в default

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

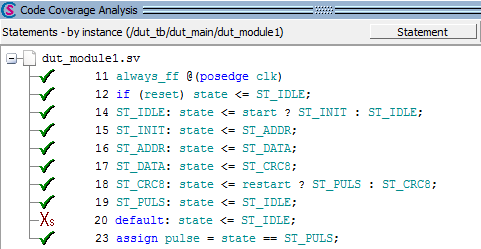

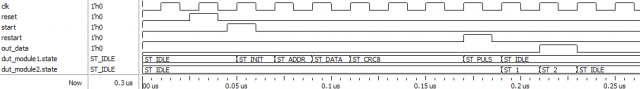

Всем много добра! Занимаюсь разборками с покрытием кода. Интересует покрытие операторов (и не только, но об этом пока речь не идёт). ModelSim показывает, что покрыто всё, за исключением машин состояний, а именно состояний default, куда я, по его мнению, никогда не попадаю. По временной диаграмме, в принципе, я тоже не вижу, что я когда-либо нахожусь в этом непонятном мне состоянии: Вопрос: что же делать, чтобы обеспечить 100% покрытие, как того требует стандарт: выкинуть default из проекта, но что-то подсказывает, что это не есть комильфо, или умудриться всё-таки войти в него, но как?! -

Всем спасибо: сохраню тред, как обычно, на добрую память.

-

ModelSim, и вам большое спасибо.

-

Всем добра! Хочу, чтобы $display отобразил число, например, 1 в виде 001. Ну надо мне так. `timescale 1ns / 100ps module dut; integer d; initial begin d = 1; $display("=%3d=", d); d = 11; $display("=%3d=", d); d = 001; $display("=%3d=", d); d = 011; $display("=%3d=", d); d = 1; $display("=%03d=", d); d = 11; $display("=%03d=", d); d = 001; $display("=%03d=", d); d = 011; $display("=%03d=", d); $stop; end endmodule : dut Даёт # = 1= # = 11= # = 1= # = 11= # = 1= # = 11= # = 1= # = 11= А я бы хотел # = 001= # = 011= # = 001= # = 011= # = 001= # = 011= # = 001= # = 011= Что-то можно сделать?

-

Правильно я понимаю, что вы советуете FW как универсальный источник знаний?

-

И тестбенч и исходники, о котором идёт речь в этом контексте, - дело рук вашего покорного слуги. Именно это и надо доказать. У меня (пока) такой привычки нет, и я, по-вашему, где-то могу сильно пострадать из-за отсутствия оной? Если я не расцвечиваю задачи и функции, кто они по-умолчанию, и чем мне это грозит? До сих пор не задумывался.

-

Огромное спасибо! It works!

-

Display enum ModelSim vs Active-HDL

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Всем добра всевозможного! Продолжаю сражаться на ниве квалификации инструментов, по следам предыдущего своего топика, пути решения которого подсказал уважаемый dess00. И вот на этом уже, подсказанном им пути, столкнулся с очередной проблемой, выражающейся в том, что сопоставляемые мною инструменты по-разному интерпретируют один и тот же оператор вывода строки, применённый к enum. Так, для модуля `timescale 1ns / 100ps `define TICK_TIME 10 module fsm; logic clk; enum {ST_IDLE, ST_INIT, ST_ADDR, ST_DATA, ST_CRC8} state; initial begin state = ST_IDLE; @(posedge clk) state = ST_INIT; @(posedge clk) state = ST_ADDR; @(posedge clk) state = ST_DATA; @(posedge clk) state = ST_CRC8; @(posedge clk) $stop; end initial begin clk = 0; forever #`TICK_TIME clk = ~clk; end initial begin $display("At time state"); $monitor("At %3t %s", $stime, state); end endmodule : fsm Вывод ModelSim будет такой: # At time state # At 0 ST_IDLE # At 100 ST_INIT # At 300 ST_ADDR # At 500 ST_DATA # At 700 ST_CRC8 что мне очень нравится, а вот для Active-HDL вывод будет такой: # KERNEL: At time state # KERNEL: At 0 # KERNEL: At 100 # KERNEL: At 300 # KERNEL: At 500 # KERNEL: At 700 что мне совсем не нравится. Вопрос: ЧЯДНТ или как мне победить Active-HDL? -

Спасибо, но, не уверен, что это то, что мне нужно. Reference model в моём случае будет один и тот же test bench, обработанный двумя разными инструментами. А вот то, что вы предложили - логирование в файл - представляется самым логичным и правильным вариантом и вывода и сравнения работы двух инструментов. А вот этот automatic тут зачем? Оставлю здесь свой "прилизанный" и смоделированный вариант вашего примера (за который большое спасибо) Пытаюсь доказать руководству, что это - единственный правильный вариант сравнения двух инструментов ) Да, выше мы к этому уже и пришли

-

Нет, пока ещё не использовал (в этом проекте), но задумка есть, но ранее столкнулся с несоответствием одного другому и уже спрашивал на форуме, но мне никто не ответил. Чем эта модель отличается от того, что я напишу с помощью $fdisplay/$fmonitor? Прошу пояснить, ибо раньше с понятием эталонной модели не сталкивался. Спасибо. Нашёл. Можно простейший пример?

-

Всё просто: надо показать, что результаты моделирования с помощью одного инструмента совпадают с результатами второго. В том-то и дело, что на одном и том же простейшем тесте данные не совпадают! @Модератор: как тут искать по форуму свои посты (я уже задавал этот вопрос ранее, хочу вставить ссылку на тот пост, но не найду его!)? Боюсь, что у уважаемого des00 и других забот достаточно: спасибо, что на форуме отвечает.

-

Не совсем то: квалификация может основываться на независимой оценке выходных данных инструмента (это самый простой способ квалификации). Из стандарта: "Независимая оценка проверяет правильность выходных данных инструмента, используя независимые средства. Если выходные данные инструмента оценены независимо, то оценки инструмента не требуется." И там же часть примечания: "Независимая оценка выходных данных инструмента верификации может включать рассмотрение вручную выходных данных инструмента или может включать сравнение выходных данных другого средства, способного выполнять то же самое мероприятие верификации, что и оцениваемое средство. Заявитель может также предлагать другие методы независимой оценки." Правильно я понимаю, что мне достаточно сравнить vcd обработки этими инструментами моего проекта для подтверждения их идентичности и для квалификации одного из них в конечном итоге? Если так, то дело в том, что ранее я уже поднимал вопрос о нетождественности этих vcd даже для простейшего проекта. Как быть: снова посмотреть в сторону квесты и риверы? Ткните, пожалуйста, носом в такие виды отладки применимо к нашей области: гугление ничего похожего не дало..