-

Постов

484 -

Зарегистрирован

-

Посещение

Весь контент MaratZuev

-

Да, и если вы, one_eight_seven, захотите что-то сказать насчёт двух аккаунтов, то, прошу, воздержитесь. Их у меня, действительно, не один, но, полагаю, что этим я ничего не нарушаю. И снова прошу: давайте по-существу.

-

Ну, например, читать состояние полезно, если нужно сбросить машину. А так, да, обошелся тем, что заложено.

-

После долгих разборок установлено, что ModelSim считает покрытыми только переходы, совершённые "естественным" путём, т.е. такие, которые произошли по фронту исходной тактовой частоты, а состояния, переходы между которыми "засчитываются" также должны быть "насильно не установлены". Итого: играть (устанавливать (force/release)) можно только сигналами разрешения перехода между состояниями и сигналом сброса машины, состояния же самой машины и её тактирование трогать нельзя. `timescale 1ns / 1ns `define T1ns 1 // with respect to timebase (1ns) `define T1us 1000*`T1ns module fsm_tb; logic reset; logic clk; logic a; logic we; logic [2:0] mode; logic w; logic fsm_state_stop; logic fsm_state_op1; logic fsm_state_op2; logic fsm_state_op3; logic fsm_state_finish; integer file_stop_time; integer curr_time, us, ns; fsm_dut fsm_dut(.*); initial begin clk = '0; forever #10ns clk = ~clk; end initial begin reset = '0; #5ns reset = '1; #1ns reset = '0; end initial $monitor("@%2tns fsm.state = %s", $stime, fsm_dut.fsm.name()); initial begin a = '1; we = '0; mode = '0; w = '0; #25ns @(posedge fsm_dut.clk) // stop -> op1 force fsm_dut.we = '1; force fsm_dut.mode = 3'd4; @(posedge fsm_dut.clk) // op1 -> op2 @(posedge fsm_dut.clk) // op2 -> op3 @(posedge fsm_dut.clk) // op3 -> finish force fsm_dut.w = '0; force fsm_dut.a = '1; @(posedge fsm_dut.clk) // finish -> op1 force fsm_dut.mode = 3'd0; @(posedge fsm_dut.clk) // op1 -> finish #10ns force fsm_dut.reset = '1; // finish -> stop #1ns release fsm_dut.reset; force fsm_dut.a = '0; @(posedge fsm_dut.clk) // stop -> finish force fsm_dut.a = '1; @(posedge fsm_dut.clk) // finish -> op1 #10ns force fsm_dut.reset = '1; // op1 -> stop #1ns release fsm_dut.reset; @(posedge fsm_dut.clk) // stop -> op1 force fsm_dut.we = '1; force fsm_dut.mode = 3'd4; @(posedge fsm_dut.clk) // op1 -> op2 #10ns force fsm_dut.reset = '1; // op2 -> stop #1ns release fsm_dut.reset; @(posedge fsm_dut.clk) // stop -> op1 force fsm_dut.we = '1; force fsm_dut.mode = 3'd4; @(posedge fsm_dut.clk) // op1 -> op2 @(posedge fsm_dut.clk) // op2 -> op3 #10ns force fsm_dut.reset = '1; // op3 -> stop #1ns release fsm_dut.reset; end endmodule : fsm_tb # @ 0ns fsm.state = # @ 5ns fsm.state = stop # @10ns fsm.state = op1 # @50ns fsm.state = op2 # @70ns fsm.state = op3 # @90ns fsm.state = finish # @110ns fsm.state = op1 # @130ns fsm.state = finish # @140ns fsm.state = stop # @150ns fsm.state = finish # @170ns fsm.state = op1 # @180ns fsm.state = stop # @190ns fsm.state = op1 # @210ns fsm.state = op2 # @220ns fsm.state = stop # @230ns fsm.state = op1 # @250ns fsm.state = op2 # @270ns fsm.state = op3 # @280ns fsm.state = stop # @290ns fsm.state = op1

-

Active-HDL 10.5

MaratZuev ответил Kostochkin тема в Среды разработки - обсуждаем САПРы

Как вариант при вашем количестве постов стать своим и решить этот и многие другие вопросы. А напрямую: https://www.aldec.com/en/support/resources/documentation/faq/1746 The Active-HDL Lattice Edition license is distributed and controlled by Lattice Semiconductor. Active-HDL Lattice Edition is part of the Lattice ispLEVER or Lattice Diamond installation and it requires Lattice software to be installed in order for it to work properly. -

Всем добра! Есть код module fsm_dut( input logic reset, input logic clk, input logic a, input logic we, input logic [2:0] mode, input logic w, output logic fsm_state_stop, output logic fsm_state_op1, output logic fsm_state_op2, output logic fsm_state_op3, output logic fsm_state_finish ); enum logic [2:0] {stop, op1, op2, op3, finish} fsm; always @(posedge reset or posedge clk) if (reset) fsm <= stop; else case (fsm) stop : if (a) fsm <= op1; else fsm <= finish; op1 : if (~we) fsm <= op1; else if (mode == 3'd4) fsm <= op2; else fsm <= finish; op2 : fsm <= op3; op3 : fsm <= finish; finish : if (w | ~a) fsm <= finish; else fsm <= op1; endcase assign fsm_state_stop = fsm == stop; assign fsm_state_op1 = fsm == op1; assign fsm_state_op2 = fsm == op2; assign fsm_state_op3 = fsm == op3; assign fsm_state_finish = fsm == finish; endmodule : fsm_dut И есть testbench `timescale 1ns / 10ps module fsm_tb; logic reset; logic clk; logic a; logic we; logic [2:0] mode; logic w; logic fsm_state_stop; logic fsm_state_op1; logic fsm_state_op2; logic fsm_state_op3; logic fsm_state_finish; fsm_dut fsm_dut(.*); initial begin clk = '0; forever #10ns clk = ~clk; end initial begin reset = '0; #5ns reset = '1; #10ns reset = '0; end initial begin a = '0; we = '0; mode = '0; w = '0; #25ns force fsm_dut.fsm = fsm_dut.op2; release fsm_dut.fsm; #1ns force fsm_dut.clk = '1; #1ns force fsm_dut.clk = '0; #20ns $stop; end endmodule : fsm_tb главная цель которого установить машину fsm модуля fsm_dut в состояние op2 и дёрнуть clk, по которому, судя по описанию машины в модуле fsm_dut эта машина перейдёт в состояние op3. Если вывожу временную диаграмму, то машина в заданный момент времени переходит, как положено (показано в максимальном приближении): Но если глянуть покрытие кода, то переход остаётся недетектированным. Почему?

-

Всё, всем спасибо, под вечер уже биты убегают...

-

По названию и сути это - адрес процессора

-

`timescale 1ns / 1ns module cmp; reg [25:0] a_cpu; reg cs_cpu; reg ena; always @(negedge cs_cpu) if (a_cpu[21:0] >= 22'h0) ena <= 1'b1; else ena <= 1'b0; initial begin cs_cpu = 1'b0; forever #10 cs_cpu = ~cs_cpu; end initial begin #5 a_cpu = 25'h0000000; #20 a_cpu = 25'h3ffffff; #20 a_cpu = 25'hzzzzzzz; #20 a_cpu = 25'hxxxxxxx; end initial #100 $stop; initial $monitor("Time = %2t, a_cpu = 0x%7h, ena = b%0b", $stime, a_cpu, ena); endmodule Даёт # Time = 0, a_cpu = 0xxxxxxxx, ena = b0 # Time = 5, a_cpu = 0x0000000, ena = b0 # Time = 20, a_cpu = 0x0000000, ena = b1 # Time = 25, a_cpu = 0x1ffffff, ena = b1 # Time = 45, a_cpu = 0xZzzzzzz, ena = b1 # Time = 60, a_cpu = 0xZzzzzzz, ena = b0 # Time = 65, a_cpu = 0xXxxxxxx, ena = b0 И Да, действительно, нижняя ветвь имеет место быть хотя бы в симуляторе. Всем спасибо. Единственный вопрос: почему в строке # Time = 25, a_cpu = 0x1ffffff, ena = b1 a_cpu равен 0x1ffffff, а не 0x3ffffff, как задано?

-

В чём смысл такого сравнения?

MaratZuev опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Всем добра. Продолжаю разбирать чужое добро и наткнулся на такой кусок кода: input [25:0] a_cpu; input cs_cpu; reg ena; always @(negedge cs_cpu) if (a_cpu[21:0] >= 22'h0) ena <= 1'b1; else ena <= 1'b0; Не понятно, а что: возможны варианты, когда if отработает по ветви a_cpu[21:0] < 22'h0 ? -

Спасибо, ушёл читать. Не мною заложены. Я, лишь, провожу разбор полётов.

-

Да, на семинаре от LRDA я как-то присутствовал: показал нашим, но они интереса не проявили. У нас есть КТ-254, плохо переведённый с DO-254 и РМ-254, чуть шире помогающий понять, что же имели в виду переводчики КТ. Но, вот, где бы было написано: бери так и делай - вот этого нет. Либо я очень плохо искал. Кстати, сам стандарт говорит, ЕМНИП, что он говорит ЧТО надо, а КАК надо - не говорит.

-

Последние четыре предложения звучат непоследовательно: "Не нужен. Является. Нужно. Не стоит." Как, всё-таки, правильно?

-

Спасибо, про 4-х битовое представление совсем забыл. Про шашечки: я бы с радостью поехал, если бы было бы время. Шашечки-то нарисовать не успеваем. А за неоднократное напоминание вам спасибо. Буду ещё раз премного благодарен, если в очередной раз ткнёте носом в (желательно небольшой) талмуд, который бы осветил для вашего покорного слуги покрытие комильфо.

-

1 Используйте блоки кода - как видите, цитирование плывёт 2 count_echo_cmp < 3'd2 - здесь, наверное, не 3 как размерность, а 2? 3 Где закрывающий else для if (ce)?

-

Зачем последний else?

MaratZuev опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Может, я чего не понимаю, но зачем автор так пишет?: always @(posedge clk or posedge rst) if (rst) takt <= 0; else if (a[1:0]==2'b00) takt <= 1; else if (a[1:0]==2'b01) takt <= 2; else if (a[1:0]==2'b10) takt <= 3; else if (a[1:0]==2'b11) takt <= 4; else takt <= 1; Я всё про покрытие кода или про то, как мне покрыть последнюю строку? Только ли исключить её из рассмотрения соответствующими прагмами? -

Для памяти, объявленной as usual, ничего добавлять не надо - он её показывает

-

Главные слова. Но где их брать? Просьба ткнуть носом того, что, как думает, всё облазил, но, наверное, что-то мог проглядеть.

-

Рискую навлечь справедливое возмущение по поводу якобы размножающихся тем, проистекающих, вроде бы, из одного корня, но не хотелось бы сваливать в одну кучу, тем более, что всё-таки темы разные, и для этой я решения нигде не нашёл (возможно плохо искал). Моделирую всё ту же altufm, которую проинициализировал своим mif. Читаю и радуюсь считанному. Но вспоминаю, что ModelSim умеет показывать содержимое памяти: открываю соответствующую вкладку, а там - пусто. Вопрос: а где же данные? Всё, вроде бы, облазил..

-

Да, в этом собака могла порыться. Попробую реализовать. Спасибо. В исходном посте решил не приводить хидер, как (думал) несущественный, ан нет: потребовался. Вот он: `ifndef _main_vh_ // prevent many inclusions `define _main_vh_ `define ADDR_FLASH_DIM 9 `define ADDR_FLASH_RNG [`ADDR_FLASH_DIM-1:0] `define DATA_FLASH_DIM 16 `define DATA_FLASH_RNG [`DATA_FLASH_DIM-1:0] `endif // `ifndef _main_vh_ Все адреса покрываются...

-

Что под вариациями подразумевается? Я и так читаю все адреса. Или их надо не только читать, но и обрывать чтение, не дожидаясь установки готовности? Какие ещё варианты? Они - выходы, я над ними не властен.

-

Altufm или как покрыть чёрный ящик

MaratZuev опубликовал тема в Среды разработки - обсуждаем САПРы

Всем добра! Хотел я, было, отделаться малой кровью и исключить из рассмотрения проприетарную часть кода, но руководство решило, что крыть - так крыть. Ну, хозяин - барин, подумал я, и бросился на амбразуру, решив, что мегафункция, которую предстояло покрыть, не семи пядей во лбу, а довольно-таки скромная. Речь, как упомянуто в топике, про altufm в её параллельной реинкарнации. Итого: берём простой модуль (в хедере описания констант), который инстанциирует эту мегафункцию: `include "main.vh" module main ( input logic `ADDR_FLASH_RNG addr_flash, input logic nread_flash, output logic data_valid_flash, output logic `DATA_FLASH_RNG dataout_flash, output logic nbusy_flash, output logic osc_flash ); flash flash_inst ( .addr ( addr_flash ), .nread ( nread_flash ), .data_valid ( data_valid_flash ), .dataout ( dataout_flash ), .nbusy ( nbusy_flash ), .osc ( osc_flash ) ); endmodule : main И тестбенч: `include "main.vh" `timescale 1ns / 1ps `define T1ns 1 // with respect to timebase (1ns) `define T1us 1000*`T1ns module main_tb; logic `ADDR_FLASH_RNG addr_flash; logic nread_flash; wire data_valid_flash; wire `DATA_FLASH_RNG dataout_flash; wire nbusy_flash; wire osc_flash; main main(.*); initial begin addr_flash = 0; nread_flash = 1'b1; end initial begin forever begin nread_flash = 1'b0; @ (negedge nbusy_flash); // wait for nbusy_flash falls @ (posedge nbusy_flash); // wait for flash ready nread_flash = 1'b1; addr_flash++; if (addr_flash == '0) begin // all flash is read $stop; end end end endmodule : main_tb Работаем в соответствии с документом User Flash Memory in MAX V Devices-Max V Devices Handbook, Section II, Chapter 7 Тетсбенч перебирает (читает) все адреса и на этом заканчивает свою работу. Но ModelSim не доволен: Вопрос: ЧЯДНТ и что делать? -

Да, я знаю такую конструкцию, но спасибо за напоминание.

-

Доброго всем. Столкнулся с таким вопросом: в проекте для maxII есть ip umf. Т.к. вещь сия представляется чёрным ящиком, покрывать оную на все 100% кажется (по кр. мере на первый взгляд) неразумным, и хочется её убрать из рассмотрения. Как это правильно сделать? Прагмы //coverage off и //coverage on по непонятным мне причинам не работают. Нашёл команду coverage exclude, но вот что имею: Хидер main.vh `ifndef _main_vh_ // prevent many inclusions `define _main_vh_ `define LED_CNT_DIM 24 `define LED_CNT_RNG [`LED_CNT_DIM-1:0] `define ADDR_FLASH_DIM 9 `define ADDR_FLASH_RNG [`ADDR_FLASH_DIM-1:0] `define DATA_FLASH_DIM 16 `define DATA_FLASH_RNG [`DATA_FLASH_DIM-1:0] `endif // `ifndef _main_vh_ Главный и единственный модуль main.sv `include "main.vh" module main ( input logic res, input logic clk, output logic led, // flash inst input logic `ADDR_FLASH_RNG addr_flash, input logic nread_flash, output logic data_valid_flash, output logic `DATA_FLASH_RNG dataout_flash, output logic nbusy_flash ); logic `LED_CNT_RNG led_counter; always_ff @(posedge clk) if ( res ) led_counter <= '0; else led_counter <= led_counter + 1'b1; assign led = led_counter[`LED_CNT_DIM - 1]; // coverage off flash flash_inst ( .addr ( addr_flash ), .nread ( nread_flash ), .data_valid ( data_valid_flash ), .dataout ( dataout_flash ), .nbusy ( nbusy_flash ) ); // coverage on endmodule : main И тестбенч main_tb.sv `include "main.vh" `timescale 1ns / 1ps module main_tb; logic res; logic clk; logic led; // flash inst logic `ADDR_FLASH_RNG addr_flash; logic nread_flash; wire data_valid_flash; wire `DATA_FLASH_RNG dataout_flash; wire nbusy_flash; main main(.*); initial begin res = 1'b0; #10ns res = 1'b1; #25ns res = 1'b0; end initial begin clk = 1'b0; forever #25ns clk = ~clk; end initial begin addr_flash = 0; nread_flash = 1'b1; end endmodule : main_tb Компилю c:\MentorGraphics\modelsim64_10.6d\win64\modelsim.exe -do coverage.tcl где сам coverage.tcl выглядит так variable test_bench main_tb if {!([vsimAuth] == "ALTERA")} { # https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=122907 # main window at full screen wm state . zoomed } # clear transript window of ModelSim or QuestaSim .main clear # create library if [file exists work] { vdel -all } vlib work variable FilesCompiled 0 variable ProjectDir ../../Project/Project variable TestBenchDir ../../Project/TestBench variable QuartusSimLibDir ../../Project/QuartusSimLibs # compile all source files # https://stackoverflow.com/questions/51409347/how-to-copy-or-move-multiple-files-with-same-extension variable FilesInProjectDir [glob -nocomplain $ProjectDir/*.v $ProjectDir/*.sv] if {[llength $FilesInProjectDir]} { vlog +acc $ProjectDir/*.v $ProjectDir/*.sv variable FilesCompiled 1 } # compile testbench vlog +acc +incdir+$ProjectDir $TestBenchDir/$test_bench.sv if {$FilesCompiled == 1} { variable top_module_opt $test_bench variable coverage_letters_string "sf" # optimize design append top_module_opt "_opt" vopt -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L maxii_ver +cover=$coverage_letters_string $test_bench -o $top_module_opt vsim -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L maxii_ver -L work\ -cvgperinstance -cvgzwnocollect 1 -c -coverage work.$top_module_opt source simulation_run.tcl simulation_run 1us coverage report -html $top_module_opt.ucdb -code $coverage_letters_string view instance source ColumnConfig_instance.tcl } else { puts "No files to compile found!" } После компиляции ModelSim показывает мне вот что: Т.е. подцепились непонятно откуда библиотеки 220model.v и maxii_atoms.v, причём не из закромов ModelSima, куда я транслировал все библиотеки для maxII и других, используемых мною семейств, а из внутренностей Quartus-a: и ладно бы, но я нигде не могу найти концов, откуда они подцепились?! Далее, попытка исключить из покрытия файл flash.v путём vsim -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L maxii_ver -L work\ -cvgperinstance -cvgzwnocollect 1 -c -coverage work.$top_module_opt coverage exclude -src $ProjectDir/flash.v source simulation_run.tcl simulation_run 1us вполне успешна, а вот повторение того же для упомянутых выше библиотек vsim -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L maxii_ver -L work\ -cvgperinstance -cvgzwnocollect 1 -c -coverage work.$top_module_opt coverage exclude -src $QuartusSimLibDir/maxii_atoms.v coverage exclude -src $QuartusSimLibDir/220model.v coverage exclude -src $ProjectDir/flash.v source simulation_run.tcl simulation_run 1u приводят ModelSim в непонятное состояние: Просьба высказаться..

-

Правильный вопрос. Посыпаю голову. Недописал. Да мне уже сейчас пришло, судя по выше"скорректированному"мною коду и комментарию вашему и вопросу andrew_b )

-

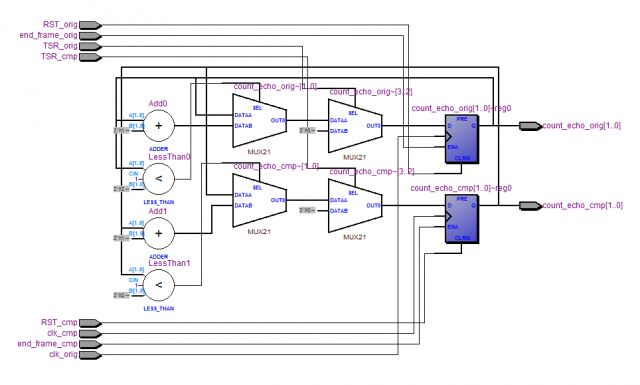

"Причесал" исходный код насколько возможно согласно воззрениям большинства: always_ff @(posedge clk_cmp or posedge RST_cmp) if (RST_cmp) count_echo_cmp <= 2'h0; else if (end_frame_cmp) if (TSR_cmp) count_echo_cmp <= 2'h0; else if (count_echo_cmp <= 2'd2) count_echo_cmp <= count_echo_cmp + 2'd1; else count_echo_cmp <= count_echo_cmp; И RTL-Viewer показал то, что требовалось: Но вот вопрос: если у меня не код, а два чёрных ящика: как мне понять, эквивалентны ли они или нет?