-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

Полевик со встроенным стабилитроном?

ViKo ответил тема в В помощь начинающему

Тоже нормально. На резисторах в базе можно сэкономить, наверное. А тип полевика не подскажете? Наверное, можно измерить следующим образом. Включить последовательно с катушкой маленький резистор, ом 10, чтобы он не оказывал влияния на процессы в катушке. Смотреть осциллографом напряжение на нем в момент включения. Оно будет пропорционально току в цепи. При включении ток через катушку начинает плавно нарастать. Если бы не было сопротивления катушки, ток нарастал бы линейно, а в нашем случае - нарастает по затухающей экспоненте, приближаясь к постоянному току, определяемому сопротивлением катушки. Интересует именно наклон этой экспоненты в начальный момент. ∆I/∆t. А напряжение - считаем, что все приложено к катушке - то, от чего запитано. L = U / (∆I/∆t). -

Полевик со встроенным стабилитроном?

ViKo ответил тема в В помощь начинающему

В вашем случае я обошелся бы биполярным транзистором в корпусе SOT23 и диодом параллельно реле в маленьком корпусе SOD80. -

Полевик со встроенным стабилитроном?

ViKo ответил тема в В помощь начинающему

Да, ток будет тем же, 30 mA. Напряжение в момент пробоя 600 V. Итого, мощность 18 W, приложенная к полевику (точнее, его диоду), блоку питания (с малым сопротивлением) и катушке. Ясно, что эта энергия быстро спадет, но что она успеет сделать при этом... -

Полевик со встроенным стабилитроном?

ViKo ответил тема в В помощь начинающему

Засомневался в своих словах. Когда напряжение подскочит до 600 V, и пробьется стабилитрон, ток будет определяться сопротивлением катушки и малым сопротивлением блока питания. Т.е., ток будет большой. Похоже, rezident прав. Правда, сколько тока выдает блок питания, не важно... -

Полевик со встроенным стабилитроном?

ViKo ответил тема в В помощь начинающему

Ток через катушку (тот самый, 30 mA) определяется ее омическим сопротивлением. Когда транзистор отключится, ток будет тот же. А вот напряжение из-за ЭДС самоиндукции подскочит. Диод (паразитный или специально созданный в этом полевике, точно не скажу, но все же, кажется, что специально) пробьется и током (тем же, 30 mA в начале) "погасит" это напряжение. Можно обойтись без дополнительного диода. Но с ним как-то спокойнее. :) -

Пять уроков Verilog

ViKo ответил nckkm тема в Языки проектирования на ПЛИС (FPGA)

автору темы: У вас в коде на стр. 22 (кстати, неплохо бы пронумеровать), есть строка for(i=7; i>=0; i=i+1). Исправьте, пожалуйста. И по поводу "знакомых" конструкций. Если имеется в виду слово "reset" и т.п., то это не так. Эти слова ничего не значат для синтезатора. Синтезатор создает устройство, соответствующее заданному коду, используя существующие элементы ПЛИС. -

Пять уроков Verilog

ViKo ответил nckkm тема в Языки проектирования на ПЛИС (FPGA)

Урок 1. Wire я перевел бы как цепь. Проводник? А провод - это что-то круглое, висящее в воздухе. Запутывает - то ли есть такая программа Verilog, то ли "программа" для Verilog. Написали бы как оно переводится, HDL, и использовали "описание устройства". Запятую после "провода". Мне очень не нравится, когда говорят о битах, байтах как об объектах женского рода. Почти везде! Мне кажется, правильно говорить "битов", "байтов", "омов" (еще в "Искусстве схемотехники" 25 лет назад так писалось) и др. Код заключен в "рамочку". Лучше бы делать без нее, просто, как во всех книжках, с отступом для абзаца кода (ну и шрифт моноширинный, как у вас и сделано). Фон у вас есть, будет заметно и без рамки. И внутри модулей про форматирование отступами не забывайте. Не обязательно RAM. А как же ROM, SDRAM, DDRAM, FIFO. Напишите просто "память" без RAM, если очень хотите. от которого останется только 4 младших бита Урок 2. По-русски пишется с одним "ф". На языках программирования это называется тип. Урок 4. Нужно заменить на "Процедурные", как уже говорилось. В стандарте на SV называются параллельные и последовательные блоки операторов. Это - лишнее. Так, как написано, так и будет. :) И это лишнее... Блокирующее присваивание блокирует выполнение следующих операторов, пока не выполнится само. Неплохо бы добавить для понимания термина. (дальше у вас нашел..., но лучше бы сразу описать) Неблокирующее присваивание совсем не обязательно будет синтезировано триггерами. Это - большое распространенное заблуждение! Эту строку лучше разбить на две и правильно сформатировать отступами пишется "ненулевой", "независимо" Не потому..., а потому, что reset имеет приоритет, перед остальными сигналами. Согласно приоритетности сигналов и задается их порядок. Это нужно посмотреть в помощи по Quartus, например. И немного не по теме. На картинке макетной платы (схему не смотрел) многие выводы ПЛИС соединены вместе. Это ограничивает ее возможности. Спасибо! Скучно не было :) -

В Handbook на Quartus есть раздел ”Register Power-Up Values in Altera Devices”, в котором написано: Вот откуда берется начальный ноль на выходе триггера. (дам еще один повод sazh упрекнуть меня в неточности, но истина мне дороже)

-

Проблемы нет. Просто еще пара триггеров к "минимальной синтезируемой конструкции". :) Ну а это вы сказали зря. Трогать святое святых - тактовый сигнал?! 2 igormihmih @(posedge clk) синтезируется. У Полякова я не видел, чтобы было сказано обратное. Однако книгу эту всерьез воспринимать не рекомендую. Лучше накачайте книг по ссылкам в "шапке" данного раздела форума.

-

Имелось в виду "в начале симуляции". Могу и картинку Квартуса показать. А в реальном кристалле после включения триггеры сбрасываются? Отнюдь нет. Это как повезет. А вот здесь уже я вас не понимаю... Вы имеете в виду Verilog vs. SystemVerilog? Я к этому не стремился. Упростил приведенный masics первым пример. В Интернете есть документ "Actel HDL Coding Style Guide", где просто и со вкусом показаны различные конструкции на VHDL и Verilog. Так вот в нем нет ни одного неблокирующего присваивания! Рекомендую. Upd. Кстати, если делать сброс, то нужно еще и синхронизатор к нему. Иначе, если сброс закончится в момент фронта тактового импульса, возможно метастабильное состояние триггера. А вы говорите, тема исчерпана :)

-

Reset в данной конструкции, конечно, не повредит. Но, поскольку вопрос был задан о минимальной синтезируемой конструкции, то приведенные мной три строчки кода и есть решение.

-

В Quartus работает. В других программах, думаю, тоже будет. По-умолчанию неопределенное состояние воспринимается, как 0. Я мог бы спросить "почему это?" Но лучше направлю почитать вот эту дискуссию. Можете начать с самого начала. http://electronix.ru/forum/index.php?showt...st&p=732818

-

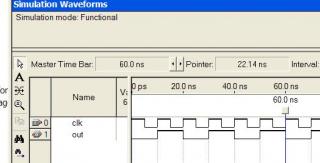

Если уж делать минимальную конструкцию, то и сброс не нужен. module div (input clk, output reg out); always @(posedge clk) out = !out; endmodule

-

тип wor в Quartus

ViKo ответил des00 тема в Языки проектирования на ПЛИС (FPGA)

Вот такой код у меня (Quartus 9.0 без SP) работает: module Test2_wor (input logic [6:0] in, output wor out); generate genvar i; for (i = 0; i <= 6; i++) begin : wor_gen assign out = in[i]; end : wor_gen endgenerate endmodule Фактически - SUB_FIRST из первого поста. ?? -

вопрос по AHDL

ViKo ответил S_Hawk тема в Языки проектирования на ПЛИС (FPGA)

The LE delay is 1.3 ns; the cascade chain delay is 0.6 ns. Задержка примерно раза в 2 меньше. Кроме того, не используются цепи межсоединений. Так что выгода была бы. Да что теперь говорить. "Няма таго, што раньш было!" -

В вашем случае нужно было иначе разделить устройства по платам, чтобы не передавать между платами множество ВЧ сигналов. Можно передать через разъем, чередуя сигнал, земля, сигнал, земля... Т.е. помня, что мало довести сигнал от передатчика к приемнику, нужно обеспечить возвратный путь сигналу по земле. И желательно, чтобы эти пути были рядом. И по платам прямой и возвратный пути должны идти близко. Остаются вопросы экранировки от внешних помех (это общим экраном решается) и устранение взаимных наводок (разнести сигналы как можно дальше). И еще - волновое сопротивление цепей. У печатных дорожек оно одно, у разъемов другое. Появятся отражения, форма сигнала исказится. На приемном конце должен быть резистор (или делитель). Длина цепей тоже важна. Каждые 20 см - задержка в 1 нс.

-

тип wor в Quartus

ViKo ответил des00 тема в Языки проектирования на ПЛИС (FPGA)

Разве я говорил про неоднозначность? Я говорю о невозможности физически реализовать wor|wand внутри ПЛИС. Это не философское рассуждение, а констатация факта. И то что в ПЛИС они заменяются обычными or|and с использованием логических элементов, меня не удивляет, скорее, радует. Также, как то, что элементы с z-состоянием заменяются мультиплексорами. И то, что это невозможно сделать на выводах, меня не беспокоит. Чего и вам желаю :) Жаль, что не получили. Хотя мне кажется, что с быстродействием таких элементов не так хорошо, как у обычных. Т.е. "к...ы" они, что не написали этого в документации? Ну что ж - "к...ы"! :) Верно. Я потом заметил, но решил, что на суть вопроса это не влият. Upd. В Handbook на Quartus 9.1 из 2454 страниц wired in/or, wor/wand не упоминаются вообще. В Help Quartus 9.0 написано только: Wired Nets (wor, wand,trior, and triand Nets) Supported Все остальное - наши с вами фантазии. Не вижу предмета для спора. -

Чтобы ходить по ассемблерным командам, нужно сделать активным окно Disassembly. Если хотите пройтись по стартапу, нужно, чтобы в Опциях/Дебаг не стояла птичка Run to main(). У меня были проблемы с ULink ME, потом прошли. Возможно, оттого, что перешел на Keil 4.12. Процессор, правда, у меня STM32F103.

-

Если делать по-хорошему, то передавать сигнал коаксиальным кабелем. И разъем соотвествующий использовать. Конкретный тип не назову. Можно поискать, например, у "Бурого Медведя". Между приборами используются 50-омные коаксиальные кабели, разъемы называются BNC. Если делать без заморочек, можно передавать любым проводом и любым разъемом из тех, что нравятся.

-

тип wor в Quartus

ViKo ответил des00 тема в Языки проектирования на ПЛИС (FPGA)

Посмотрите на картинку, где я показал результат работы. Написано WideOr. А не wired or. Мягко говоря, Altera подтасовала понятия. Это не одно и то же, хотя функцию выполняют одну. Wired Or на стандартных логических микросхемах можно было собрать, используя логику с открытым коллектором (стоком), прицепив их несколько на один провод, и присобачив туда же подтягивающий резистор. (Не помню, правда, реального примера за свою практику, обходился обычными логическими микросхемами. Как и большинство других разработчиков, я думаю.) Внутри имеющихся ПЛИС это невозможно, там нет ни wor, ни trior. А стандарт - он же универсальный, предусмотрел такую возможность. Если появится ПЛИС, в которой будут элементы с тремя состояниями, там все будет реализовано по-честному. Вот тогда-то шины будет просто делать! Эх! -

вопрос по AHDL

ViKo ответил S_Hawk тема в Языки проектирования на ПЛИС (FPGA)

А 32 в 1 - это пять слоев! А по-проще - никак? А если каждый N объединить с входным сигналом, а потом всех их объединить по И с применением цепей каскадирования (а в Циклоне их, кажется, уже нет :( ) - то будет 2 (два) слоя. -

тип wor в Quartus

ViKo ответил des00 тема в Языки проектирования на ПЛИС (FPGA)

Проблема в том, что внутри ПЛИС, как вы понимаете, нет подтягивающих резисторов, выходов с тремя состояниями, выходов с открытым коллектором. А без этого wor/wand/tri не сделать. Это все заменяется логическими схемами, мультиплексорами. Вот так оно и supported. А в выходном пине ни логики, ни мультиплексора не сделаешь. Вот и нет проводной логики в портах. Разве что снаружи объединить выводы :-) Так что меня этот "глюк" не удивляет. -

Получил предупреждение этим летом. Считаю - в целях профилактики. "Подливал масла в огонь" при "разборках". Поначалу был недоволен, даже писал администраторам. Потом смирился, принял, как должное. Тем более, что другим, как я понимаю, предупреждения не видны. Если можно снять по причине "амнистии" - хорошо. Если нет, потерплю до следующего года.

-

ADG3304 - нечеткие уровни

ViKo ответил slanted тема в В помощь начинающему

Вот так сразу - гори в аду!? Вариантов, что не работало, может быть несколько. Первый, распространенный - при пайке две соседние ножки сцепились между собой. А после перепайки - расцепились :-) Во-вторых, на выходе у микросхемы стоит 6 кОм, значит, вместе с подтягивающим резистором в микроконтроллере образуется делитель. В-третьих, чтобы принимались входные сигналы, они не должны отличаться от питаний (и земли) более, чем на 0,3 В. Уверен, что дело не в ADG3304, а в неумелом применении. А схема ускорения - так она много где есть. Начиная с 8051 микроЭВМ (как тогда называлась). -

Думаю, прочитав это http://electronix.ru/forum/index.php?showt...st&p=739040 у вас все получится