-

Постов

12 216 -

Зарегистрирован

Весь контент ViKo

-

На задержках в логических элементах вычислить период частоты. :) Приблизительно.

-

Как разрулить AGND и DGND на моей платке.

ViKo ответил uriy тема в Работаем с трассировкой

:bb-offtopic: Я скромненько предпочел бы такое, мегагерц на 500 :) http://www.tek.com/products/oscilloscopes/...?app=simulation -

На регистре из трех триггеров. Чтобы когда ловится один фронт, было мало, а когда три - много.

-

Как разрулить AGND и DGND на моей платке.

ViKo ответил uriy тема в Работаем с трассировкой

Возвратные токи для питания и возвратные токи для сигналов требуют разных решений, фактически, взаимоисключающих. И я не вижу ничего, лучше сплошного слоя земли. Только под инвертирующими выводами ОУ и т.п. ее быть не должно, иначе ОУ может возбудиться. По картинке. Цифровые и аналоговые питания и земли нигде не связаны, кроме как под микросхемами? Это значит, что для каждого такого питания должна быть своя обмотка трансформатора, свой регулятор. -

Вы же написали, что нельзя. ;) Задержать на логике, объединить по xor, получим импульс на каждое изменение сигнала... Его можно и в триггер защелкнуть, собой же, задержанным. Только триггер тот кто-то сбрасывать должен. :(

-

Подзаряжать конденсатор, прицепленный снаружи на ножку, импульсами от интересующей частоты. А разряжать медленно, по другой цепи (диодами развязать). Другой ногой ПЛИС проверять уровень (0 или 1). Приблизительно.

-

Лучше поставить сдвиговый регистр из двух триггеров, и тактом интересующей частоты задвигать единичку. Сделать таймер на счетчике на время, равное двум периодам интересующей частоты. По переполнению таймера читать выход сдвигового регистра, и очищать его. Если была единица, значит, два фронта частоты пришли. Значит, имеется сигнал с частотой, не менее, чем нужная. Если делать на одном триггере, то при частоте, ниже требуемой, будет то 0, то 1.

-

Как разрулить AGND и DGND на моей платке.

ViKo ответил uriy тема в Работаем с трассировкой

Приз - в студию! А, может, возьмете деньги? :) Ну, приз, так приз! :) По-правде сказать, это не те примеры, которые нас интересуют. Там, где нужна гальваническая развязка, естественно, все ноги развязаны. 3GW_24992_0_LR_2010.01.12.16.00.19_16581_EN.pdf -

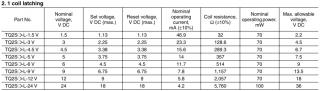

Я для себя выбрал реле TQ2SL-4.5V. Должно укладываться во все расчеты. И экспериментально проверено. А делают их десяток фирм, только названия разные. http://pewa.panasonic.com/components/relays/signal-relays/ Кстати, матрица 2х2 - это то же кольцо. У которого два диагональных угла - ряды, а два других - колонки. Кольцо имеет преимущество перед несимметричной матрицей в том, что в нем все выходы работают в одинаковых условиях, деградируют от тока все равномерно. А не так, что в матрице 1х10, один выход работает за десятерых.

-

Вы подаете в симуляторе на двунаправленный вывод bidirx всегда активный сигнал, 0 или 1. Нужно на время, когда этот вывод должен выдавать изнутри наружу, внешний сигнал задавать высокоимпедансным, z.

-

Как разрулить AGND и DGND на моей платке.

ViKo ответил uriy тема в Работаем с трассировкой

Кто найдет микросхему, у которой земляные ноги не прозваниваются между собой, тому - приз! :) -

А вы в редакторе MAX+plus II нажмите правую кнопку мышки и выберите Insert Template. А там в шаблонах можете найти интересующий пример. Можно и через меню Edit сделать то же самое. Только кричать так громко не стоит. И код надо обрамлять тэгами ...

-

Для 8-ми реле - их можно соединить в кольцо. 8 отводов, один порт. Лишний паразитный ток, идущий по 7-ми последовательно соединенным реле, при управлении восьмым - в 7 раз меньше. Итого 25 * (1 + 0.143) = 28,6 mA. Для 10-ти реле - уже не так красиво в программировании.

-

А "диспетчеры" (администрация наша) куда смотрят? Надо бы пробудить "летчиков" (тамошнюю администрацию) ото сна. Как-то так. Мы же, вроде, жалуемся, обращаем внимание, а не просто констатируем факт? Иначе, зачем?

-

TimeQuest для чайников

ViKo ответил des00 тема в Среды разработки - обсуждаем САПРы

Да, вы правы. ПЛИС не успевает защелкнуть приходящие данные с АЦП по инвертированному такту. Мы указываем защелкивать следующим тактом. И Quartus должен был бы добавить задержки по данным, чтобы к моменту регистрации вторым тактом они уже установились (setup), а после предыдущего такта еще держались (hold). Но я не вижу изменения времени Data Arrival, и в случае однотактовом, и в двухтактовом оно одинаковое. Получается, для регистрации вторым тактом все времена подходят. В-принципе, почему бы и нет? Тут главное - чтобы изменение данных от АЦП попало в окно между hold и setup, а на каком такте, неважно. Можно перебрать несколько вариантов, пока не попадем. Только что латентность данных меняется. -

Quartus 11

ViKo ответил Mad_kvmg тема в Среды разработки - обсуждаем САПРы

назад? извиняюсь, не разобрался в вопросе -

Началось еще в выходные. В последние два дня не могу задать пароль для входа на ftp, not connected 2. Хотелось бы хоть пару слов услышать - "Знаем, работаем над улучшением ситуации".

-

Проверил, подтверждаю. Значит, нужно делать матрицу с бОльшим количеством линий, чтобы ток нигде не концентрировался на одном ненужном реле. Думаю, начиная с 3x3 уже будет нормально. Ну, и 2х2 тоже работает нормально.

-

TimeQuest для чайников

ViKo ответил des00 тема в Среды разработки - обсуждаем САПРы

в 13-м сообщении. :) -

Там уже, как бы не тек, будет мал для того, чтобы переключить реле.

-

TimeQuest для чайников

ViKo ответил des00 тема в Среды разработки - обсуждаем САПРы

Хочу ясности в одном вопросе. По pdf TimeQuest для чайников от des00. В части System-Synchronus Input с целью улучшения зазоров предлагается проинвертировать такт и ввести мультицикловую проверку (стр. 38). Вопрос - вправе ли мы так вольно распоряжаться тактами. Ведь данные с АЦП приходят с каждым тактом. Почему же мы защелкиваем их не по ближайшему? Вот если бы был какой-то промежуточный регистр или цепь задержки... да и это ничего бы не дало... -

у меня именно так и происходило. Но в матрице 2x2 не будет двух последовательно соединенных реле, запитанных от пары выводов. Будет только тройка, а она уже не включается. Да и в любой другой матрице из рядов и колонок, где в активное состояние включается только пара выводов. Вот если цеплять по реле между всеми ножками, тогда - да.

-

Для tay, для zzzzzzzz Спасибо, понятно.

-

Я думаю, это упрощенная картинка. В других datasheet (да и в этом дальше) и такой нет, одни треугольнички. Просто тогда непонятно, почему сопротивление в нуле равно 25 Ом, а ток при подключении выхода к питанию всего 58 мА.

-

Лучшим ответом была бы схема выходов PIC'а.