new123

Участник-

Постов

1 090 -

Зарегистрирован

-

Посещение

Весь контент new123

-

Можно расти дальше, делать поддержку VLAN в пакетах =)

-

Сам я не пробовал, я изначально рассадил чтение и запись по разным портам, но вот тут поднялся схожий вопрос и пользователь из интела ответил, что мол это нормально даже по умолчанию, и READ надо поднимать, даже если wait в 1, потом сидеть и ждать https://community.intel.com/t5/FPGA-Intellectual-Property/Avalon-Dual-Master-Bus-with-constant-waitrequest-on-connection/m-p/1192928#M21811

-

А на записывающем waitrequest при этом ноль приходит?

-

Как то очень давно мучался подстраивал фазы PLL, может после реконфига подстроить просто надо с помощью сигналов управляющих phasexxxx? Интересно, если после реконфига сделать резет pll, новые настройки сбросятся?

-

Это он вам сообщает, что синтезатор оптимизировал и выкинул из проект часть логики. В принципе это нормально, за исключением тех случаев, когда вы допустили ошибку (в коде или не все подключили) и у вашей логики нет выхода, тогда он ее тоже выбросит

-

Вопроса как такого в посте нет =), но судя по всему есть какая то проблема. Я в свое время, тоже начинал платы изучать с нажатия кнопок. Есть такое неприятное явление в кнопках, как дребезг контактов. Советую начать изучать с этого. Судя по коду (мельком глянул), еще не изучали

-

Вот мануал https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/xcvr_user_guide.pdf , пункт Analog Settings for Cyclone V Devices 2-26, присутствует XCVR_TX_VOD Сами значениея тут https://www.intel.com/content/www/us/en/programmable/documentation/mcn1422497163812.html#mcn1419933628979, пункт Typical TX VOD Setting for Cyclone V Transceiver Channels если я все правильно понял

-

Посмотрел ваш мануал, действительно, если выставить в assigment editors Programmable Differential Output Voltage (VOD), то поддерживает только LVDS подобные. Может еще какой то пункт есть, надо почитать Может попробовать напрямую прописать XCVR_TX_VOD в qsf? У меня циклона не было из пятерок, попробовать не могу. На стратиксе делал

-

мало вводных. Опишите больше, что там фиттер то пишет. Так то в мануале по всем пятым сериям написано, что все трансиверы работают по pcml, при этом Vod можно задрать до 1600. Вдруг вы в XCVR_TX_VOD прям номинал пишите, а там нужно значение от 0 до 63 Попробую ради интереса чуть позже у себя поменять, не помню, менял я его пару лет назад или нет

-

не дает прописывать? что за чип?

-

MATLAB HDL Coder + Quartus

new123 ответил nbjkm тема в Языки проектирования на ПЛИС (FPGA)

ramstyle к wire не применяется. Только к reg подобному. Потом в отчете квартуса можно глянуть, где он расположил в ram или нет, насколько помню в разделе Fitter, сейчас не с руки смотреть -

попробую еще раз вставить свои 5 копеек, вдруг это все таки то, что надо генерю список нужных путей, с параметром full_path report_timing -to_clock { .... } -setup -npaths 10 -detail full_path... Далее могу просматривать конкретно каждый путь, как он проходит и сколько времени занимает К примеру, как у меня идет сигнал от трансивера до нужной мне логики Буквально вчера, у меня тут стоял встроенный pileline от квартуса между трансивером и логикой и я его тоже видел. Ради интереса, сделал EDA Netlist Writer, проверил там пути, они точно такие же.

-

у загрузчика же есть конфиг (к примеру grub.cfg), в котором прописано от куда какой образ грузить. Или вопрос не про это?

-

вот я имелл ввиду то, что Rob выше описал. А задать правильно путь, это по началу целое искусство =) лучше конечно GUI для начала пользоваться, нагляднее.

-

TimeQuest пишет время пути. Как общее, так и подробнее по шагам.

-

Реализация фильтра

new123 ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Я если преобразовать не могу, и не хватает > 500ps на FAST и очень надо, то: 1) Пробую делать пред расчеты, если такое возможно в задаче, чтобы хоть как то облегчить расчет 2) Начинаю смотреть пути, которые не укладываются, что им мешает. -

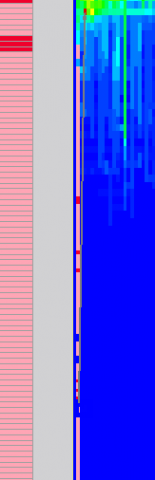

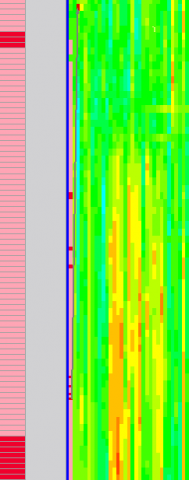

Посмотрел Route Utilization картину. Я так понял, участок в готовом проекте нагружен и он не может так же быстро проложить маршрут, как в проекте пустышке. Раньше Route Utilization не делал, не знал что у меня тут так заполнено. Может кто нибудь знает, как бы еще этот путь экспортнуть отдельно и прописать в готовом проекте? а дальше уже пусть раскладывает как хочет. Может какой констрейн есть, в котором я могу задать ограничение по времени на путь?

-

на ебее отличный вариант за 500 стратикс пятый есть, уже пару лет продается, у продавца нескончаемые запасы =)

-

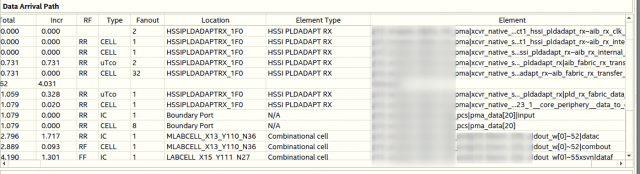

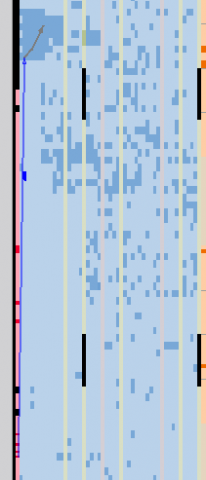

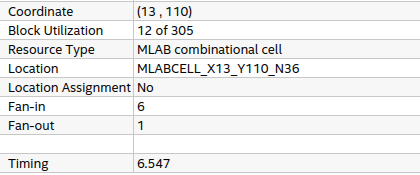

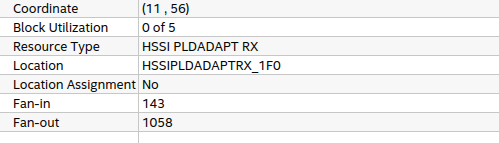

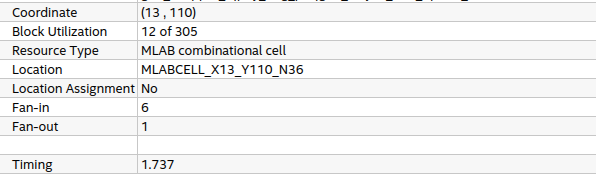

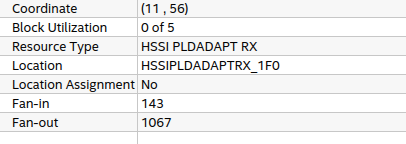

Форумчане привет. Решил откомпилить модуль в чистом проекте, упаковать его partition и перенести в другой большой проект. Некий финт ушами, думал, что я так без слаков легко перенесу готовый модуль. Что по факту получилось. Посмотрел видео курсы и видео по этой теме. Все практически прошло идеально, кроме нескольких путей. В проекте, который не пустышка и куда импортнул партишины, точно такой же путь занимает гигантский тайминг. Для начала привожу просто путь в готовом проекте и в пустом проекте с одним модулем. Они полностью идентичны, то есть партишин точно импортнулся нормально после финальной сборки. На всякий случай, инфа по этому пути, чтобы точно понять, что они ендентичны. Проект куда импортнул (источник, получатель): Проект с которого импортнул (источник, получатель): Как видим, путь практически идентичен, за исключением небольшого различия FAN, что думаю, не сильно должно просаживать. Но тайминг 6.5 против 1.7 как то совсем худо. Может кто знает, что за задержка такая дикая? Куда копать. Заранее спасибо. ps. Пока писал, подумал, а может клок так долго доходит?

-

Цена такая, наверное потому что БУ (не написано в товаре статуса). Для БУ ориганала AV норм ценник. КАк покупатель со стажем пишу. Правда покупал всегда на ebay из какого нибудь США. Было дело, заморачивался и с TAOBAO китайским. Там продавцы хоть сразу пишут, оригинал чип или копия (правда по фото всегда видно)

-

а да, это пашет без проблем. Оно там все умному автоматически определяет

-

я вот думал, что у меня баг на плате и не придавал значение, но на второй другой плате и чипе точно так же. Вдруг и у вас так же. Прошиваю версией x8, а определяется как x4, еще раз резетю компьютер, чтобы PCIE опросился и при втором резете x8 появляется. Происходит это только тогда, когда перед прошивкой сбросишь питание компьютера (получается и платы). А вот если по готовой прошивке поверх прошить следом, то при резете первом все норм, x8 можно попробовать подцепить от terasic дрова. Они юзают стандратную avmm корку + весьма модифицированный драйвер альтеры. Пример более менее качественный. Но к сожалению, половину драйвера упаковано в библиотеку, так что придется подстраиваться. Но возможно. либо брать драйвера альтеры и пробовать модифицировать, но мне кажется его писали студенты. вообще, я свою первую версию драйвера выкатил месяца через 3-4. Главное понять принципы. Надеюсь альтеровская версия вам подойдет. =) Кстати у альтеры есть качественный мануал, по шагам рассказывается, что нужно сделать, чтобы стартануть DMA движок у них. Если вкратце по памяти: 1) Создать различные буфера (для RX и TX) в драйвере 2) Создать таблицы дескрипторов в драйвере 3) Качественно проинициализировать со стороны драйвер в карте BAR0 нужными созданными адресами буферов и тд. И движок стартанет. Дальше только управляете через BAR0 посылками

-

да, для меня наверное уже месяцев 10 стоит жесткое правило - все должно быть синхронизировано правильно и по классике. И в этой задаче я тоже могу засинхронить правильно через тот же фифо например. Но тут у меня есть проблема с летенси и хочется решить по другому

-

да, я вот это и хотел уточнить, что только я сильно уверен. Все эти цепи у меня отдельно на бумажке выписаны и проверены. то есть мне надо поковырять тему констрейнов в сторону скважности? и изначально задать именно для того одного случая?

-

спасибо, буду знать как это называется =) а не подскажите, каким констрейном лучше это все описать?