masverter

Свой-

Постов

75 -

Зарегистрирован

-

Посещение

-

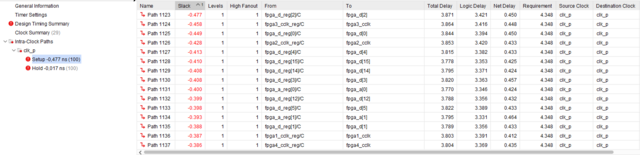

Сделал так: set output_ports {fpga_a[*] fpga_d[*] fpga*_cclk} set_output_delay -clock clk_p -2.5 [get_ports $output_ports] set_property IOB TRUE [get_ports $output_ports] Правильно сделал? 2.5 - число, при котором слак меньше всего получается. Это для clk_p (клок, которым защелкиваются триггеры CCLK* и D*) 230 МГц. Кажется, не сойдутся тайминги, и требования избыточные. CCLK 115 МГц в данном случае будет.

-

Доброго времени суток! Есть ПЛИС, которая программирует другие ПЛИС (режим - Slave SelectMap16). Количество программируемых ПЛИС - 4. Шина данных общая, линия CCLK у каждой ПЛИС своя. Я реализовал способ "Non-Continuous SelectMAP Data Loading with Controlled CCLK". Работает, но хотелось бы частоту поднять. Подскажите, пожалуйста, как описать временные соотношения между CCLK и D. Какой тактовый сигнал выбрать? Смущают нюансы: * должны выполняться соотношения между CCLK1 и D, CCLK2 и D, CCLK3 и D, CCLK4 и D; * CCLK1 и т.д. - выход триггера, подключенный к выходному порту. Может быть пример подходящий найдется?

-

Заклеил - теперь не пробуждается. Большое спасибо за помощь!!!

-

К сожалению, не помогло.

-

Напрямую с разъема на ПЛИС идет. В ПЛИС не подключена. Правильно ли понимаю, что согласно фразе "Only add-in cards that support the wake process connect to this pin" из PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 1.1 так и должно быть?

-

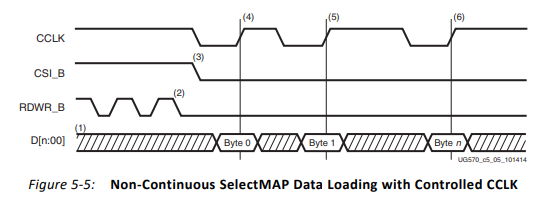

Здравствуйте. Есть PCIe плата с Kintex UltraScale. Заливал на нее пример от Xilinx по работе с DMA. Плата в системе (Win10) виделась как Xilinx DMA. Тестовыми программами туда-обратно гонялись данные. Все вроде бы хорошо, но при выключении из винды комп пытается выключиться, но после выключения включаетя снова. Подскажите, пожалуйста, с чем может быть связано? В биосе вроде бы "Power on..." отключены. Скрин настроек биоса прилагаю. Без платы выключается нормально.

-

Попробовал оба варианта в железе - работают нормально. Всем участникам большое спасибо за помощь!

-

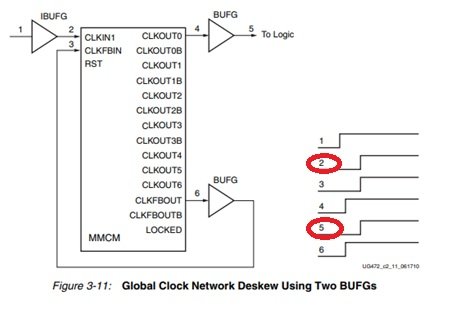

Клок подключен на вход PLL через IBUFDS. Писал про это, картинку перерисовывать не стал. Понимаю так - если и данные и клок проходят через IBUFDS, то задержку IBUFDS компенсировать не нужно.

-

UPD. Повернул фазу PLL на 90 градусов, за счет этого удалось сместить запасы по setup и hold на 1 ns (1.022, 2.136). На железке пока попробовать нет возможности.

-

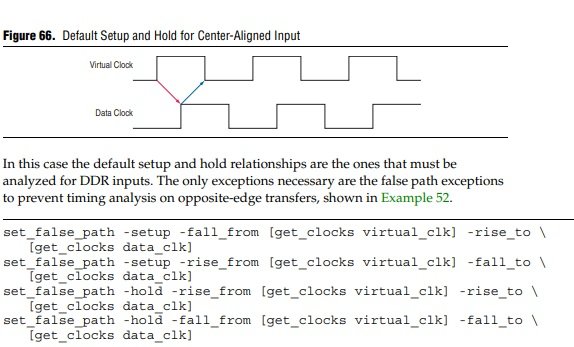

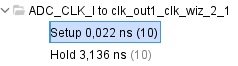

Спасибо за ответы! Поставил PLL и BUFG. В UG472 нашел картинку как это выглядит (в моем случае на входе IBUFDS). PLL используется для компенсации задержки распространения клока через BUFG. Получается, данные и клок будут приходить на IDDR с тем же относительным смещением, что и на входы ПЛИС, задерживаясь на одинаковую величину на IBUFDS. Далее добавил исключения на передачу данных между противоположными фронтами (AN 433: Constraining and Analyzing Source-Synchronous Interfaces) Теперь временные ограничения интерфейс проходит. Однако, положительный slack по setup 0.022ns, по hold – 3.136ns. Маловато. В этой ситуации двигать фазу PLL или по-другому решается?

-

Всем спасибо за ответы! Да, длины проводников выровнены. Не принципиально, можно и с PLL - главное, чтобы работало. В чем преимущество подхода с ФАПЧ? Вы на нем фазу клока под данные в ходе экспериментов подстраиваете, затем константой забиваете? Почему не констрейните? И какой буфер использовать на 7 серии? Подход с IDELAY понятен. Насколько понимаю, IDELAY можно и на клок поставить, чтобы компенсировать задержку BUFG, при условии, что на плате нет различия в задержках всех линий данных и клока. Но для этого нужно было плату соответствующим образом разводить.

-

-

500 много - а как понять сколько нормально без автоматической подстройки? Подскажите, а что даст ISERDES? Позволит паковать данные по n слов, тем самым можно понизить частоту последующей обработки данных? Сейчас на IDDR приходит тактовая 250 МГц, данные 500 МГц. На выходе по одному каналу получаю два слова двойной разрядности. В принципе, 250 для последующей обработки нормально. Провел эксперимент - задал в констрейнах частоту АЦП 125 МГц, в два раза увеличил время валидности данных - hold slack стал меньше примерно в два раза, но он все равно большой!

-

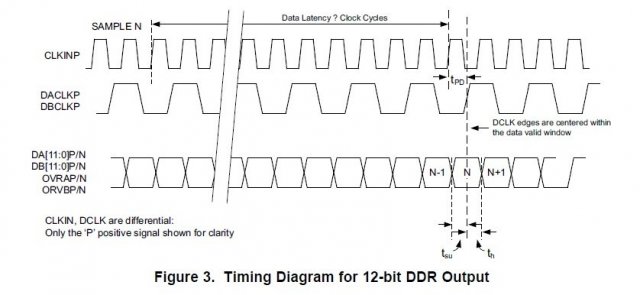

Получение данных от АЦП ADS5404

masverter опубликовал тема в Работаем с ПЛИС, области применения, выбор

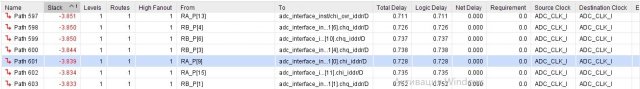

Здравствуйте! У меня есть АЦП ADS5404 и ПЛИС Kintex7 xc7k325tffg676-2. На данный момент получается принимать без искажений данные от АЦП со скоростью 400 Msps. Хочется 500. В ПЛИС тактовые входы поступают на IBUFGDS, входы данных - на IBUFDS, затем на IDDR, защелкиваются глобальными клоками с IBUFGDS. Пробовал защелкивать каждый канал своим клоком, затем перещелкивал на общий клок. Это приводило к тому, что данные задерживались на такт в одном из каналов относительно другого. В итоге пришел к тому, что сразу защелкиваю данные одним клоком. Во временном анализе большие hold slack’и. Ограничения на интерфейс описывал по шаблону (Center-Aligned Double Data Rate Source Synchronous Inputs) Подскажите, пожалуйста, что не так делаю? -

Спасибо!