masverter

Свой-

Постов

73 -

Зарегистрирован

-

Посещение

Весь контент masverter

-

Заклеил - теперь не пробуждается. Большое спасибо за помощь!!!

-

К сожалению, не помогло.

-

Напрямую с разъема на ПЛИС идет. В ПЛИС не подключена. Правильно ли понимаю, что согласно фразе "Only add-in cards that support the wake process connect to this pin" из PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 1.1 так и должно быть?

-

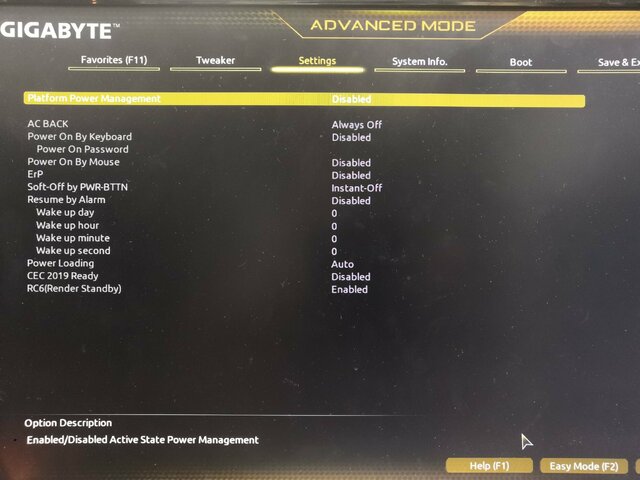

Здравствуйте. Есть PCIe плата с Kintex UltraScale. Заливал на нее пример от Xilinx по работе с DMA. Плата в системе (Win10) виделась как Xilinx DMA. Тестовыми программами туда-обратно гонялись данные. Все вроде бы хорошо, но при выключении из винды комп пытается выключиться, но после выключения включаетя снова. Подскажите, пожалуйста, с чем может быть связано? В биосе вроде бы "Power on..." отключены. Скрин настроек биоса прилагаю. Без платы выключается нормально.

-

Попробовал оба варианта в железе - работают нормально. Всем участникам большое спасибо за помощь!

-

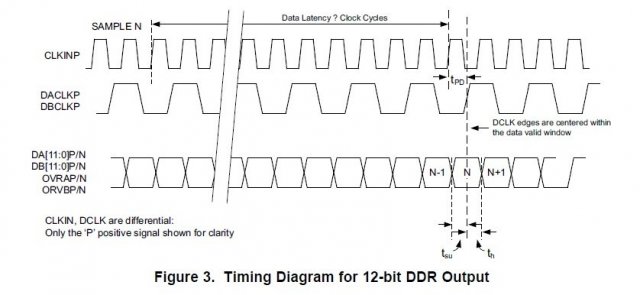

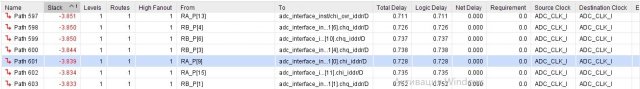

Клок подключен на вход PLL через IBUFDS. Писал про это, картинку перерисовывать не стал. Понимаю так - если и данные и клок проходят через IBUFDS, то задержку IBUFDS компенсировать не нужно.

-

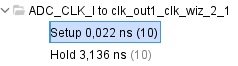

UPD. Повернул фазу PLL на 90 градусов, за счет этого удалось сместить запасы по setup и hold на 1 ns (1.022, 2.136). На железке пока попробовать нет возможности.

-

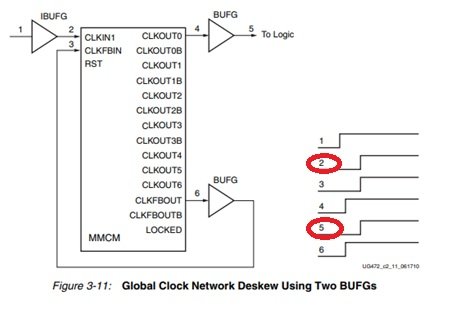

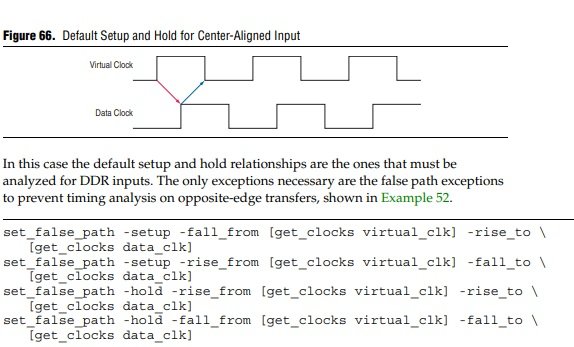

Спасибо за ответы! Поставил PLL и BUFG. В UG472 нашел картинку как это выглядит (в моем случае на входе IBUFDS). PLL используется для компенсации задержки распространения клока через BUFG. Получается, данные и клок будут приходить на IDDR с тем же относительным смещением, что и на входы ПЛИС, задерживаясь на одинаковую величину на IBUFDS. Далее добавил исключения на передачу данных между противоположными фронтами (AN 433: Constraining and Analyzing Source-Synchronous Interfaces) Теперь временные ограничения интерфейс проходит. Однако, положительный slack по setup 0.022ns, по hold – 3.136ns. Маловато. В этой ситуации двигать фазу PLL или по-другому решается?

-

Всем спасибо за ответы! Да, длины проводников выровнены. Не принципиально, можно и с PLL - главное, чтобы работало. В чем преимущество подхода с ФАПЧ? Вы на нем фазу клока под данные в ходе экспериментов подстраиваете, затем константой забиваете? Почему не констрейните? И какой буфер использовать на 7 серии? Подход с IDELAY понятен. Насколько понимаю, IDELAY можно и на клок поставить, чтобы компенсировать задержку BUFG, при условии, что на плате нет различия в задержках всех линий данных и клока. Но для этого нужно было плату соответствующим образом разводить.

-

-

500 много - а как понять сколько нормально без автоматической подстройки? Подскажите, а что даст ISERDES? Позволит паковать данные по n слов, тем самым можно понизить частоту последующей обработки данных? Сейчас на IDDR приходит тактовая 250 МГц, данные 500 МГц. На выходе по одному каналу получаю два слова двойной разрядности. В принципе, 250 для последующей обработки нормально. Провел эксперимент - задал в констрейнах частоту АЦП 125 МГц, в два раза увеличил время валидности данных - hold slack стал меньше примерно в два раза, но он все равно большой!

-

Получение данных от АЦП ADS5404

masverter опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте! У меня есть АЦП ADS5404 и ПЛИС Kintex7 xc7k325tffg676-2. На данный момент получается принимать без искажений данные от АЦП со скоростью 400 Msps. Хочется 500. В ПЛИС тактовые входы поступают на IBUFGDS, входы данных - на IBUFDS, затем на IDDR, защелкиваются глобальными клоками с IBUFGDS. Пробовал защелкивать каждый канал своим клоком, затем перещелкивал на общий клок. Это приводило к тому, что данные задерживались на такт в одном из каналов относительно другого. В итоге пришел к тому, что сразу защелкиваю данные одним клоком. Во временном анализе большие hold slack’и. Ограничения на интерфейс описывал по шаблону (Center-Aligned Double Data Rate Source Synchronous Inputs) Подскажите, пожалуйста, что не так делаю? -

Спасибо!

-

Сделал эквалайзер с обучением по известной последовательности - разницы не заметил. Не могли бы прокомментировать? Модельку прикладываю. equalizer_known_symbols.slx

-

Всем спасибо за ответы! С устройством понятно. Жаль что так, реклама многообещающая была. Для себя вот этот момент хотел прояснить: Что Вы имеете ввиду под демодулируется "в слепую" и как это применимо к рассматриваемому методу?

-

Ясно. Подчёркивается, что требуется только символьная скорость и центральная частота. Видимо, модуляция и кодирование определяются на устройстве.

-

Устранение сигнала помехи. Как работает?

masverter опубликовал тема в Алгоритмы ЦОС (DSP)

Доброго времени суток! Недавно занимался вопросом разделения суммы двух сигналов. Во время изучения литературы и существующих решений наткнулся на устройства от IDirect: GS380X, GS380S/1000x2. Они предназначены для удаления сигнала помехи из принимаемого сигнала. GS380S/1000x2 позволяет также выделять сигнал помехи. Для настройки устройства оператору требуется указать только центральную частоту принимаемого сигнала и символьную скорость. Знание о помехе не требуется. Помехой может быть модулированный сигнал, непрерывный сигнал(ы), сумма модулированного и непрерывного сигнала. Нет вариантов как это может работать. Может быть кто-нибудь подскажет в каком направлении двигаться и что читать? CSIR WhitePaper 7.9.20.pdf -

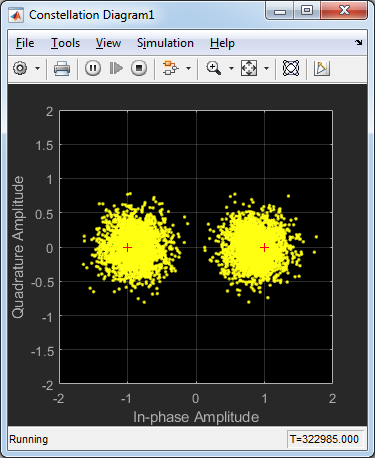

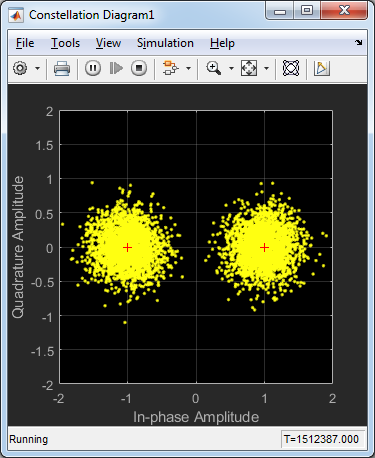

Спасибо. В нашем приложении красивая картинка играет не последнюю роль. Выводим отношение сигнал+шум/шум и получается, что с выключенным эквалайзером оно ощутимо выше, чем с включенным. Да, MSE становится меньше, о чем Вы писали, но ОСШ при таком стягивании падает.

-

Стягивание сигнального созвездия адаптивным эквалайзером

masverter опубликовал тема в Алгоритмы ЦОС (DSP)

Здравствуйте! Наблюдаю такой эффект: при уменьшении ОСШ, начиная с определенного значения, адаптивный эквалайзер начинает "стягивать" созвездие. Для примера - модуляция BPSK, DD Linear LMS Equalizer, канал без искажений с АБГШ (модель прилагаю). Созвездие на входе эквалайзера и на выходе привожу ниже. Видно, что выходное созвездие стянуто к центру координатной плоскости. Хотелось бы понять почему так происходит (ошибки в принятии решения так влияют?) и что с этим делать: использовать другие алгоритмы при падении ОСШ, "растянуть" уровень сигнала после эквалайзера с помощью АРУ, что-нибудь еще? Попробовал разные виды эквалайзеров из Simulink. CMA, Normalized LMS, Normalized LMS DFE, Sign-LMS примерно также стягивают созвездие, Sign Regressor LMS и Sign Sign LMS - нет. equalizers.slx -

Прием DVB Carrier ID

masverter ответил masverter тема в Алгоритмы ЦОС (DSP)

Большое спасибо за помощь! -

Прием DVB Carrier ID

masverter ответил masverter тема в Алгоритмы ЦОС (DSP)

Сам порой себя не понимаю. В первом посте неверно выразился - имел ввиду то, о чем Вы писали - демодуляцию и повторную модуляцию основного сигнала. Модулируем, затем вычитанием - правильно? Получаем шум + CID. Приводя эту фразу, я хотел обратить внимание, что основной сигнал (host carrier) может быть около уровня шума (is ... near the noise floor itself). Тогда с демодуляцией и повторной модуляцией основного сигнала могут быть проблемы, значит, вроде бы, можно обойтись и без этого. -

Прием DVB Carrier ID

masverter ответил masverter тема в Алгоритмы ЦОС (DSP)

сейчас все больше склоняюсь к мнению, что да. Вот здесь пишут, что сигнал с расширенным спектром позволяет идентифицировать несущую хоста, даже когда несущая хоста находится значительно ниже другой несущей или около уровня шума (The spread spectrum signal reportedly enables the host carrier to be identified even when the host carrier is well below another carrier or near the noise floor itself). В таком случае успешно демодулировать и повторно модулировать основной сигнал вряд ли возможно. Но хотелось бы все-таки уточнить. -

Прием DVB Carrier ID

masverter опубликовал тема в Алгоритмы ЦОС (DSP)

Здравствуйте! Подскажите, как должен работать приемник сигнала DVB CID. Точнее интересует - нужно ли перед собственно демодуляцией DSSS сигнала вычитать из суммы сигналов (хост + CID) сигнал хоста? -

LMS7002M

masverter ответил masverter тема в RF & Microwave Design

По сравнению подсказать не могу, т.к. анализом занимался другой человек. Понравился частотный диапазон, полоса пропускания + вот эта плата. Сейчас с ней пытаемся работать. -

LMS7002M

masverter ответил masverter тема в RF & Microwave Design

Не понял, как SISO режим организован. Задействован только один приемный канал, второй не используется? Если так, то хотелось бы понять, чем обусловлена разница по полосе в SISO и MIMO режимах. Предполагаю, что быстродействием цифровой части чипа.