Поиск

Показаны результаты для тегов 'xilinx'.

-

Xilinx Versal AI Edge Series

МакроГрупп опубликовал тема в Объявления пользователей

Versal AI Edge Series – самая масштабируемую и адаптируемая платформа для оконечных и встроенных систем от Xilinx Подробнее -

Макро Групп – официальный дистрибьютор HiTech Global, производителя плат на ПЛИС Xilinx и Intel FPGA (Altera) Подробнее

-

- плис

- fpga xilinx

-

(и ещё 4 )

C тегом:

-

Доброго времени суток! Разбираюсь с GTP трансиверами и не могу добиться нормальной симуляции example design, генерируемого из Wizard. Пошарил по форуму xilinx, почитал про их косяки при симуляции, но вроде все уже должно было быть исправлено. Суть в том, что в симуляции приемник не отрабатывает сброс и вообще не шевелится. RXOUTCLK, RXUSRCLK, RXUSRCLK2 не выдают клок, а RXRESETDONE остается в 0. При этом передатчик процедуру сброса проходит, PLL лочится. Пошарил форум xilinx и например один пользователь пишет, что симулируют аж 10 мс и не наблюдают RXRESETDONE - ссылка, на что ему рекомендуют добавить 2 строчки кода в tb для ускорения симуляции. У меня же симуляция принудительно останавливается на 3,5 мс из-за некоторого сгенерированного условия в tb. Во внутренний сгенерированный код залезал, разбирался, вроде понял, что проблема в модуле RX RESET FSM (ожидает в автомате состояний фронта сигнала, который уже давно прошел). Но править сгенерированный код вендора не хочется и не правильно это. На форуме xilinx написал и тут параллельно. Может быть, кто-нибудь сталкивался с подобными проблемами? Думаю, многие devs с форума заводили эти трансиверы.

-

Не прошивается ПЛИС Xilinx

Skryppy опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. У меня есть несколько приборов с Artix. Все приборы прошиты и работают. Когда понадобилось обновить прошивку, то выявил одну проблему - в одном приборе не обновляется прошивка. В Vivado прошивка начинает заливаться, но проходит буквально 2 секунды и окно прошивки закрывается, при этом сообщений об ошибке нет, но в ПЛИС осталась старая прошивка. Лог когда все ОК: Лог когда нет результата: Если прошивать флешку, то в этом приборе ошибка: [Labtools 27-3347] Flash Programming Unsuccessful: Failure to set flash parameters. Самое интересное, что если запустить Impact, то он прошивает и ПЛИС и флешку нормально в этом приборе. Может кто сталкивался с такой проблемой? P.S. Разъёмы переподключал, компьютер перезагружал, программатор менял - не помогло. -

Этот курс включает в себя лекции, лабораторные занятия и демонстрации, которые помогут вам оптимизировать энергетические и тепловые решения с помощью Versal ACAP. Подробнее

-

Инженеров-разработчиков и сотрудников ИТ-отделов приглашаем принять участие в техническом семинаре, посвящённом новейшим продуктам компании Xilinx. Семинар пройдёт в городе Минск 24 мая Подробнее

-

Адаптивные SoM-модули Kria от Xilinx

МакроГрупп опубликовал тема в Объявления пользователей

Компания Xilinx анонсировала выпуск собственных адаптивных SoM-модулей (Система-на-Модуле) серии Kria. SoM модули Kria – это новый способ быстрого развёртывания производительных решений Xilinx в сфере Искусственного интеллекта (ИИ) на конечных устройствах. Подробности-

- som

- xilinx ise

- (и ещё 5 )

-

В данном вебинаре будут рассмотрены основные достоинства и недостатки использования SoM-модулей, как они могут ускорить проектирование и производство готовых устройств и как изменится процесс разработки ПО, если вы будете использовать модули в своих проектах. Также представитель компании «Рифтек» расскажет об одном из реальных проектов, в котором использовались SoM-модули компании Trenz Electronic. Подробнее

-

вебинар Вебинар Xilinx по Artix Ultrascale+

МакроГрупп опубликовал тема в Объявления пользователей

Регистрируйтесь на бесплатный вебинар Xilinx, на котором будет рассказано о недавно анонсированном расширении линейки Ultrascale+ для бюджетного сегмента широкого спектра интеллектуальных периферийных решений. Подробности -

Всем привет. Мы проводим стримы по FPGA/ПЛИС тематике на твиче по адресу twitch.tv/fpgasystems Обычно, это среда и суббота в 20:00. Записи прошедших стримов лежат на youtube: youtube.com/c/fpgasystems Ждём Вас на стриме. Анонсы предстоящих эфиров в группе в телеграм @fpgasystems (https://t.me/fpgasystems) и VK и FB

-

Компания Xilinx объявила о существенном расширении линейки своих 16 нм устройств UltraScale+ - Artix UltraScale+. Подробнее...

-

Приглашаем на информационно практический вебинар «Решения Xilinx для интеллектуального управления электроприводом». На вебинаре будут рассмотрены решения Xilinx на базе систем на кристалле (SoC) для экосистем, в которые входят различные электроприводы. Эти решения обеспечивают не только оптимальное управление одним или несколькими моторами/электроприводами, но также осуществляют управление через Интернет, сбор и обработку аналитики в облаке, обнаружение неисправностей и даже предсказание времени их наступления. Зарегистрироваться

-

Ищу сотрудника. СПБ.

PLISovik опубликовал тема в Предлагаю работу

На полную занятость ищем сотрудника. Санкт-Петербург. Требуемый опыт работы: 3–6 лет Полная занятость, полный день Обязанности: Определение требований к проекту ПЛИС; Определение методик и принципов разработки; Разработка архитектуры проекта ПЛИС, функциональных и структурных моделей; Разработка проектов ПЛИС; Кодирование на языке описания аппаратуры; Создание симуляционных моделей; Участие в процессе верификации разработанных проектов; Участие в испытаниях целевого оборудования; Сопровождение изготовления образцов изделия; Участие в проведении испытаний; Участие в проведении работ по сертификации. Требования: Высшее профессиональное (техническое) образование; Опыт работы с ПЛИС фирм XILINX, Altera (Intel); Знание принципов цифровой схемотехники; Знание САПР: Quartus; Vivado Design Suite; Знание System Verilog/Verilog или VHDL; Опыт работы с высокоскоростными интерфейсами; Опыт моделирования, верификации и отладки проекта; Опыт написания testbench; Практические навыки использования Git/SVN. Знание английского языка в объеме, необходимом для чтения и понимания технической литературы по направлению деятельности. Плюсом является: Опыт разработки на ПЛИС семейства Altera: Arria10, Cyclone10 и ПЛИС Xilinx: Zynq-7000, Virtex-7, Kintex-7; Знание современных сетевых технологий Ethernet, STM, SDH, OTN, DWDM; Опыт работы с интерфейсами DDR2/DDR3/DDR4, PCI Express, 1G/10G/100G Ethernet; Знание криптографических алгоритмов и протоколов; Опыт программирования на C. Условия: Оформление в соответствии с ТК РФ, социальные гарантии (больничный, ежегодный оплачиваемый отпуск). З/п по результатам собеседования. От 100 тыс. руб Контакты: [email protected]- 1 ответ

-

- fpga ddr3/ddr4 pcie usb

- fpga

-

(и ещё 2 )

C тегом:

-

Компания Xilinx приглашает вас присоединиться к бесплатному двухдневному онлайн-тренингу, организованному совместно Xilinx Customer Training и авторизованными поставщиками обучения Xilinx. Онлайн-тренинг поможет вам быстро изучить Versal™ ACAP и приступить к проектированию устройств на его основе. Подробнее

-

Xilinx T1 — новый ускоритель для архитектуры O‑RAN

МакроГрупп опубликовал тема в Объявления пользователей

Переход к новой технологии никогда не бывает простым и связан с множеством технических и политических проблем. Одной из таких проблем, как ни странно, является то, что производители предлагают законченные, вертикально интегрированные решения. Этот подход облегчает развертывание и эксплуатацию систем, но приводит к монополизму, поскольку привязывает оператора сети к конкретному поставщику, затрудняет модернизацию сети и препятствует выходу на рынок новых производителей. Подробнее... -

Компания Xilinx приглашает присоединиться к вебинару, чтобы узнать, как применять передовые сверхбыстрые методы обработки изображений Synthetic Aperture (SA) и Plane Wave (PW) в ваших устройствах. Используемая для этого платформа Xilinx Versal™ Adaptive Compute Acceleration Platform (ACAP) с гибкой и эффективной архитектурой программируемой памяти поможет решить ваши проблемы, обеспечивая высокую производительность при низком энергопотреблении. Дата и время: 24 февраля 2021 г. | 18:00 Мск Зарегистрироваться

-

Вебинар от компании PLC2 даст вам представление об основных структурах ПЛИС компании Xilinx, основываясь на реальных задачах машинного зрения и ИИ. Зарегистрироваться

-

Компания Xilinx выпустила две серийные отладочные платы на платформе Versal – VMK180 и VCK190 (до этого были доступны только платы на инженерных образцах). По всем характеристикам, кроме характеристик чипа Versal, платы идентичны. Узнать больше...

-

Компания Xilinx добавила продукт в свой портфель модулей программирования, отладки и трассировки модуль SmartLynq+. Это высокоскоростной модуль отладки и трассировки, в первую очередь ориентированный на проекты, использующие платформу Versal, который значительно улучшает процесс конфигурации и скорость трассировки. Модуль SmartLynq+ обеспечивает до 28 раз более быстрое время загрузки Linux через высокоскоростной порт отладки (HSDP), чем через кабель передачи данных SmartLynq. Для захвата трассировки модуль SmartLynq+ поддерживает скорость до 10 Гбит/с через интерфейс HSDP. Это в 100 раз быстрее, чем стандартный JTAG. Более быстрые итерации и повторяющиеся загрузки повышают продуктивность разработки и сокращают цикл проектирования. Это означает снижение времени, затраченного на отладку, вместо которой вы можете сосредоточиться на запуске своих решений на основе Versal. Узнать больше

-

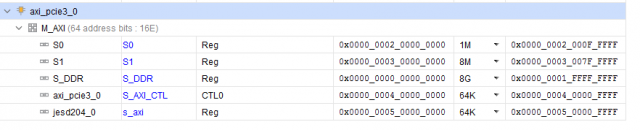

Продолжаю осваивать Vivado на Xilinx (пока с огромной натяжкой). Есть некая система: мастер PCIe -> AXI interconnect -> 5 слейвов (регистры, память, Jesd и прочее). У каждого слейва свой адрес на шине AXI (выровнял адреса до старших бит, для более простой дешифрации) Ну далее всё просто, беру в настройках корки, каждому бару присваиваю базовый адрес какого либо из слейвов, назначаю размер и всё норм. Через программу верхнего уровня спокойно читаю/пишу по каждому бару связанный с ним слейв. Проблема в том, что я ограничен 6-ю барами (в дальнейшем нужно будет больше слейвов). Решил попробовать простое решение, расширить один из баров в два раза и просто обращаться через него к последовательно стоящим друг за другом слейвам. Ну по логике, думаю, когда кончится адресное пространство первого, интерконнект должен перескочить на второй и работать уже с ним. Но не так-то всё просто, IP ядро PCIE почему то заворачивает адресное пространство на начало первого слейва и снова работает с ним, только сначала. К такому финту я не был готов.. Читал, искал инфу пока ничего не нашёл. Почему ядро так делает и как от этого можно избавиться? Сталкивался кто нибудь с такой проблемой? Буду очень благодарен разъяснениям =)

- 19 ответов

-

- interconnect

- xilinx

-

(и ещё 2 )

C тегом:

-

Временные ограничения (timing constraints) используются для задания временных характеристик дизайна. Временные ограничения влияют на все внутренние временные взаимосвязи, задержки в комбинаторной логике (LUT) и между триггерами, регистрами или ОЗУ. Временные ограничения могут быть глобальными или зависящими от пути. Для достижения требуемых временных характеристик проекта, разработчику необходимо задать набор ограничений для этапов синтеза и физической реализации, которые представляют собой требования, предъявляемые к заданным путям или цепям. Ими могут быть период, частота, перекос на шинах, максимальная задержка между конечными точками или максимальная чистая задержка. После синтеза или реализации достигнутые характеристики анализируются с помощью инструментов статического временного анализа Vivado. Статический анализ тайминга – это метод определения соответствия схемы временным ограничениям без необходимости моделирования, поэтому он намного быстрее, чем симуляция с учетом временных задержек. Инструменты Vivado STA проверяют настройки, временные характеристики (setup and hold time), ограничения синхронизации, максимальную частоту и многие другие правила проектирования. Статический анализ тайминга в качестве исходных данных принимает синтезированный список соединений либо физический список соединений проекта. На основе этих списков, алгоритмы Xilinx рассчитывают временные задержки и их соответствие задаваемым разработчиком требованиям. Запись вебинара:

-

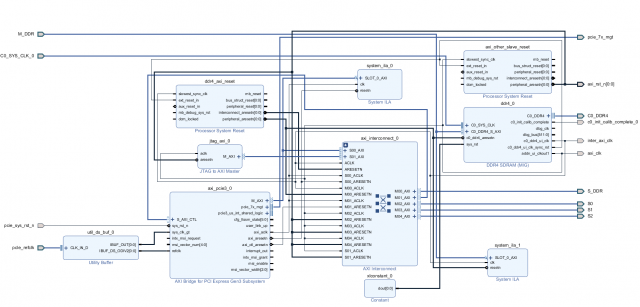

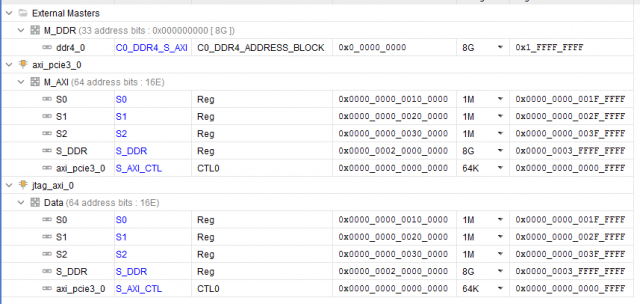

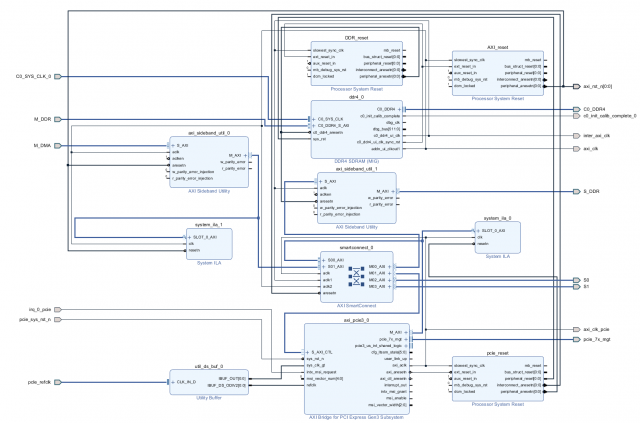

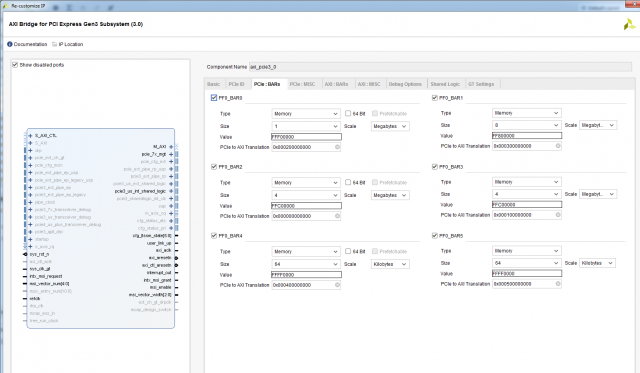

Добрый день. Долго работал с Intel (Altera) бед не знал в среде Quartus и вот пришлось перейти (к глубокому сожалению) на работу с Xilinx... Сразу был разочарован, многое из того, что доведено до автоматизма у Intel тут нужно делать самому, вникая в низкоуровневые тонкости. Очень большие ограничения на использования ip-ядер (плюс скудный набор изменяемых параметров) и плохие тайминги заводят меня в тупик. Так вот, какова суть проблемы. Работаю с Kintex Ultrascale. Понадобилось собрать систему из ядра PCIe -> interconnect ->DDR4. Прочитал кучу мануалов (PG194 v3.0, PG059 и тд.., Ответы с форумов, Видео пример настройки, Вивадовские примеры). В общем собрал систему похожую на систему из примеров. Рис. 1 Тут добавил ещё Jtag консоль для удобства отладки (в дальнейшем необходимо заменить её на свой блок ДМА), вывел интерфейсы для своих слейвов наружу. ДДР тоже вывел наружу (как S_DDR) на верхнем уровне закольцевал и вернул обратно (как M_DDR, опять же дикость связанная с XILINX пришлось решать одну из его проблем таким образом). Повесил ещё пару ИЛА для отладки и отображения шины АXI. Назначил адресные пространства. Рис. 2 Вроде всё задышало. Но с большими слеками на интерконнекте... То PCIe сама развестись не может, то на ядре ДДР какие то проблемы по таймингам. В общем всё плохо, но как то работает. По PCIe есть доступ и к DDR и к регистрам в слейвах, вроде всё корректно. Начинаю работать через Jtag консоль (в дальнейшем её нужно заменить своим блоком ДМА) и всё, ДДР не читается не пишется, комп умирает, интерконнект виснет. Проблема только при обращении к ДДР, при работе с моими слейвами регистровыми проблем нет, данные корректно пишутся и читаются. Залез по ИЛА и увидел что от ДДР не доходит сигнал BVALID и BID через интерконнект. Собственно из ДДР он вышел, но через интерконнект до второго мастера он не приходит, а для первого без проблем, всегда всё хорошо. Окей, меняю местами Jtag и PCIe та же шляпа. Jtag работает корректно, до PCIe не доходит BVALID и BID. Получается что второму мастеру по счёту просто не даётся доступ к ДДР. Листал форумы, читал советы, нашёл. Говорят что на Ultrascale и Ultrascale+ стандартный интерконнект не работает корректно, нужно ставить некий "SMARTCONNECT"... Ну окей.. читаю документацию, разбираюсь, вставляю смартконнект.. А у него оказывается выкидывает все ID(r/w/b) на шине AXI. Чтобы ID не выкидывались, ставьте "axi sideband" (говорит XILINX) до и после интерконнекта на каждой шине.. окей, поставил. Спустя все эти манипуляции я получил рабочую схему, которая может работать с двумя мастерами и без проблем читать и писать в ДДР. Рис. 3 Но эта штука разводится очень плохо. Сложность в том, что у AXI PCIe максимальная частота 250МГц, у ДДР в моём режиме (1200МГц частота памяти) AXI DDR 300МГц. Слейвы свои на такой частоте я не потяну, иначе вообще всё по таймингам умрёт... пришлось ставить в 2 раза меньше. Поставил 150МГц на слейвах. В итоге интерконнект городит очень сложную структуру из ядер клоковых конвертеров, конвертеров данных, протоколов и тд.. А потом при имплементации на эти же ядра и ругается Вивадо. Долго бьюсь над этой проблемой, не могу нормально побороть слеки. Пришлось понизить частоту ДДР до 1000МГц, соответственно AXI DDR стала 250Мгц, а частота моих слейвов 125 МГц. Слеки явно улучшились, работать можно, но проблема совсем не ушла. Как мне правильно настроить систему, чтобы не было конфликтов между ядер XILINX и всё нормально разводилось при требуемых параметрах?

- 17 ответов

-

- xilinx

- ultrascale

-

(и ещё 4 )

C тегом:

-

Здравствуйте, подскажите, как в проекте сделать так, чтобы тестбенч для верхнего уровня читал данные из файла в модуль нижнего уровня. Не делая выводы в модeле top? Либо можно как-то пометить выводы верхнего уровня, чтоб при имплементации не выдавало ошибок об отсутствии пинов для данных выводов?

-

10G Ethernet, как послать данные?

Drakonof опубликовал тема в Работаем с ПЛИС, области применения, выбор

Всем привет! Подскажите как организовать передачу данных в 10G изернете. Мне подсказали что нужен flow control module, это модуль самописный или его где-то можно взять? Я полагаю нужны разные как для сервера так и клиента. Подскажите пожалуйста куда дальше копать) Частота поднимается Zynq'ом, 156МГц, работает. Vivado 2018.4, zc706 Dev Kit (проект собран относительно ПЛИС xc7z045, а не платы). Спасибо! PL.pdf

.thumb.jpg.81a4945a234826d4eb04fb86119e9230.jpg)