GriXa

Свой-

Постов

54 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о GriXa

-

Звание

Участник

Информация

-

Город

Array

Посетители профиля

2 710 просмотров профиля

-

Да, проект под ПЛИС Вам придётся переделывать заново - у Lattice семейства ECP нет встроенного PCIE-контроллера. Есть только блок сериалайзера-десериалайзера, а само ядро PCIE выполнено с помощью логического IP-блока. Ещё рекомендую Вам узнать отдельно цену ядра, оно не бесплатное. Так же в зависимости от сложности остальной части проекта следует проверить его реализуемость под конкретно выбранную ПЛИС - ядро PCIE, в зависимости от конфигурации, может занимать от ~6K до ~14K ячеек.

-

А, да, извиняюсь, не посмотрели и неправильный скриншот отправил.

-

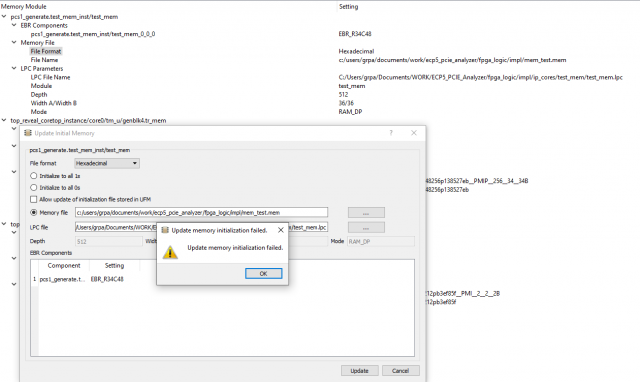

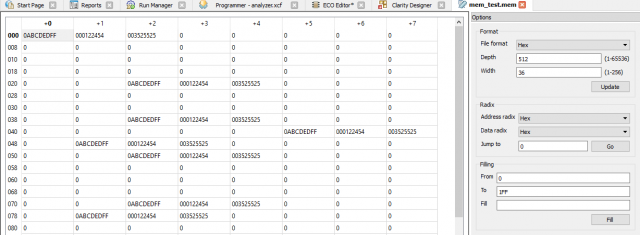

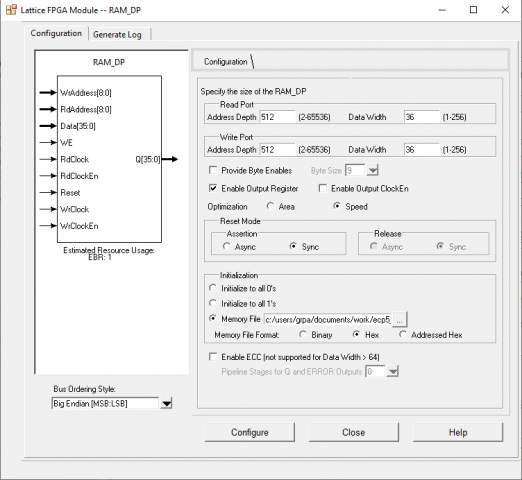

Проект, в котором я обновлял память процессора *.mem - файлом, к сожалению, восстановить сейчас не удастся. Но там я BRAM подключал не вручную, он автоматически генерировался при создании ядра mico-процессора. В top-файле я использовал лишь instance всего ядра. Сейчас я попробовал создать тестовую память в Clarity Designer с такими параметрами: Подгрузил к ней инициализирующий mem-файл: После компилляции в ECO-editor'е ещё раз попробовал подцепить этот файл, вроде всё получилось удачно: Я пишу на VHDL, кусок кода с BRAM-памятью выглядит у меня так: test_mem_inst : entity work.test_mem port map( WrAddress => (others => '0'), RdAddress => q_ra.read_addr(8 downto 0), Data => (others => '0'), WE => '0', RdClock => clk_100, RdClockEn => '1', Reset => rst, WrClock => rx_pclk_1, WrClockEn => '1', Q => mem_data_out );

-

Я использовал ECO-editor для обновления BRAM-блоков с программой для MICO32 soft-процессора. Elf-бинарник, создаваемый при компиляции сишного проекта, конвертировал в *.mem файл и обновлял с помощью ECO-editor'a. Diamond весьма капризный в плане подключения подобных файлов. Можно для начала попробовать поработать с mem-редактором. Создать новый Memory File (File -> New -> File... -> Others Files -> Memory Files) и поэксперементировать с разными форматами, размерностями и прочим.

-

Да, можно. Для этого есть ECO-Editor. Во вкладке Memory Initialization можно выбрать необходимый BRAM, добавить файл инициализации, сохранить и сгенерировать заново бинарник. В ECO-Editor'e можно изменять так же параметры многих других компонент ПЛИСины.

-

Трассировка печатной платы

GriXa ответил andrei0404 тема в Предлагаю работу

Добрый день! Озвучьте, пожалуйста, каой САПР планируется использовать? Судя по изображениям Altium? -

Это анализатор протокола Summit T24 от Teledyne. Софт - Teledyne LeCroy PCIe Protocol Suite

- 2 ответа

-

- pciexpress

- lattice

-

(и ещё 3 )

C тегом:

-

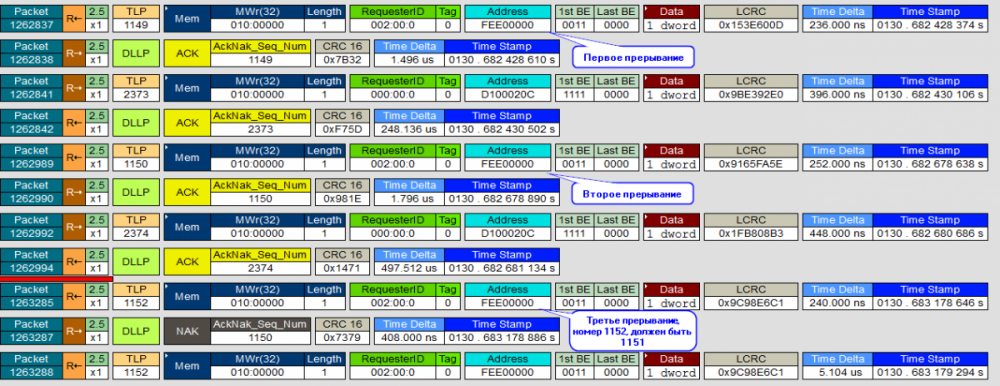

Добрый день! Возникла следующая проблема. ПЛИС Lattice ECP5UM, PCIExpress Core v6.5 подключен к COM-модулю. В ПЛИС работает таймер, который вызывает прерывание 0. После прерывания необходимо сбросить флаг состояния. Если писать в этот регистр напрямую через JTAG, всё работает нормально. Если это происходить при загрузке ОС, ПЛИС шлёт третее прерывание с неправильным номером пакета на Data Link уровне. Картинка с анализатора прикреплена ниже. После отправки пакета с неправильным номером, CPU отвечает NAK-пакетом. ПЛИС повторяет попытку еще два раза, затем уходит в LinkTraining, затем повторяет попытку с неправильным номером и так до бесконечности. Абсолютно не понятно, почему ядро в этом случае пропускает один номер. И всегда на третьем прерывании. Кто-нибудь сталкивался с подобным поведением?

- 2 ответа

-

- pciexpress

- lattice

-

(и ещё 3 )

C тегом:

-

Lattice Software

GriXa ответил StewartLittle тема в Среды разработки - обсуждаем САПРы

Да, именно так. С помощью этого скрипта так же автоматически увеличивается номер версии и дата компилляции. Удобно при чтении регистров узнавать какая именно версия загружена в ПЛИС. -

Lattice Software

GriXa ответил StewartLittle тема в Среды разработки - обсуждаем САПРы

Для таких случаев использую отдельный *_pkg.vhd файл, в котором указываю необходимые константы. Tcl-скрипт парсит этот файл, подставляет нужные значения, и, к примеру, запускает компилляцию. В проекте в качестве generic-значения присваиваю эту константу. Можно так же и в top-файле это делать, но на мой взгляд настраиваемые переменные удобнее держать в одном файле. -

tcl на FPGA

GriXa ответил Aleksei_Rostov тема в Работаем с ПЛИС, области применения, выбор

В своих проектах использую tcl скрипты для автоматического добавления номера версии и времени компиляции проекта. К примеру, в регистре сохраняется версия прошивки и дата-время компиляции. Для golden и working версии она может быть разная. Пример такого файла на vhdl Скрипт создает этот файл, потом запускает компиляцию. При каждой последующей компиляции увеличивает, к примеру, счетчик версий и изменяет время на текущее. После успешной компиляции - копирует текущую прошивку в отдельную папку с названием, соответствующим данной прошивке. Что-то типа name_working_v12.bit -

Прошу feedback по резюме

GriXa ответил Hexel тема в Ищу работу

Добрый день! Содержание документа не смотрел, но рассылать резюме было бы предпочтительнее в pdf-формате. -

Поделитесь, пожалуйста, какие именно баги в работе ПО анализатора Summit T28 Вы обнаружили?

-

Есть замечательная книга под названием "Advanced FPGA Design Architecture, Implementation, and Optimization" Steve Kilts. ISBN 978-0-470-05437-6 В книге показано на примерах, как структура дизайна влияет на скорость/пропускную способность/задержки в проекте. Мне показалось, что там подробно расписано, в каких случаях удобно использовать FSM, где лучше использовать тонну комбинаторной логики, а где кучу маленьких процессов. Если для описания используется VHDL, то Вам, возможно, было бы интересно обратить внимание еще на Two Process Method (Jiri Gaisler).

-

Использование type record в Sinplify

GriXa опубликовал тема в Среды разработки - обсуждаем САПРы

Добрый день! Использую ПЛИС от Lattice (MACHXO3). В верхнем модуле в качестве входов-выходов хочу использовать type record. Проблема в том, что если в Diamond установить в качестве синтезатора Sinplify, он не сохраняет название сети. К примеру, есть *_pkg.vhd, где у меня описан type: package pkg1 is type t_my_type is record test_input_1 : std_logic; test_input_2 : std_logic; test_input_3 : std_logic; end record end package pkg1; В *_top.vhd использую этот тип: entity test is port ( .... .... group1 : out t_my_type; .... ); end entity test; В итоге, после синтеза имею для этих выходов следующие имена цепей: group1[0] group1[1] group1[2] А хотелось бы, что бы сохранялось полное имя типа group1.test_input_1 group1.test_input_2 group1.test_input_3 Lattice LSE сохраняет имена как надо, но можно ли сделать подобное в Synplify?