Поиск

Показаны результаты для тегов 'lattice'.

-

Здравствуйте все! Помогите, пожалуйста, разобраться с конфигурацией ПЛИС CrossLink от Lattice. Я в первый раз сталкиваюсь с ПЛИС и САПР Lattice вообще и с CrossLink в частности. К сожалению, в документации Lattice нет готовой схемы подключения программатора, как у Intel, например. Или я не нашёл? В поддержке мне посоветовали воспроизвести схему из отладочной платы Master Link. Я попробовал, убрав оттуда всё, что касалось I2C, оставил только SPI, но логики работы всё равно не понимаю. Прикладываю схему, которая у меня получилась. Посмотрите, пожалуйста, кому не лень: она правильная? Возможно ли при помощи этой схемы делать следующее: - заливать прошивку в SPI Flash? - заливать прошивку в статическое конфигурационное ОЗУ ПЛИС? - работать с логическим анализатором? Насколько я понял, такая возможность есть. Вопросы: 1) Почему не конфликтуют цепи MISO ПЛИС и SPI Flash памяти? Программатор как-то отключает ПЛИС, когда заливает прошивку в SPI Flash? Или я неправильно нарисовал? 2) Можно ли как-то гарантировать, что я случайно не залью прошивку в конфигурационное ПЗУ ПЛИС? Может, кто-то поделится готовой схемой? Заранее признателен.

-

Здравствуйте все! У Lattice в семействе CrossLink есть две микросхемы в 80-выводных корпусах BGA: LIF-MD6000-6JMG80I в корпусе 80-ball ctfBGA и LIF-MD6000-6KMG80I в корпусе 80-ball ckfBGA. Цоколёвки у них одинаковые. Скажите, пожалуйста, кто знает: файлы прошивки для них получаются одинаковые? Будет ли программатор прошивать битстрим для второй микросхемы в первую? Или где-то в чипе есть идентификатор, и не прошьётся? Вопрос возник потому, что Diamond с той лицензией, которую автоматически получают все желающие, не поддерживает первую из упомянутых микросхем, и надо запрашивать у Lattice специальную лицензию. Получить её, конечно, можно, но если на производстве понадобится срочно перенести рабочее место на новый компьютер, то возникнут неудобства. Заранее признателен.

-

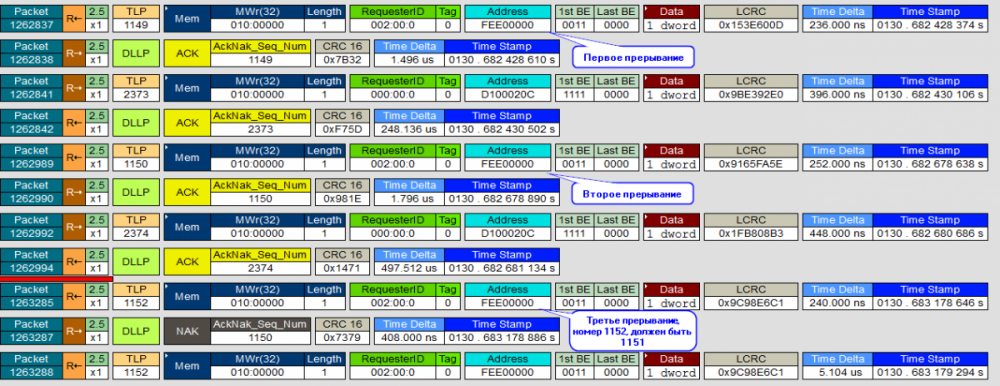

Добрый день! Возникла следующая проблема. ПЛИС Lattice ECP5UM, PCIExpress Core v6.5 подключен к COM-модулю. В ПЛИС работает таймер, который вызывает прерывание 0. После прерывания необходимо сбросить флаг состояния. Если писать в этот регистр напрямую через JTAG, всё работает нормально. Если это происходить при загрузке ОС, ПЛИС шлёт третее прерывание с неправильным номером пакета на Data Link уровне. Картинка с анализатора прикреплена ниже. После отправки пакета с неправильным номером, CPU отвечает NAK-пакетом. ПЛИС повторяет попытку еще два раза, затем уходит в LinkTraining, затем повторяет попытку с неправильным номером и так до бесконечности. Абсолютно не понятно, почему ядро в этом случае пропускает один номер. И всегда на третьем прерывании. Кто-нибудь сталкивался с подобным поведением?

- 2 ответа

-

- pciexpress

- lattice

-

(и ещё 3 )

C тегом: