vik0

-

Постов

381 -

Зарегистрирован

Сообщения, опубликованные vik0

-

-

Форумчане привет,

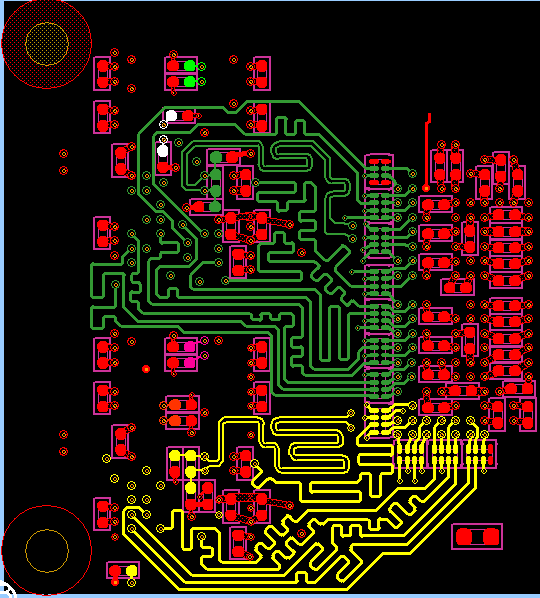

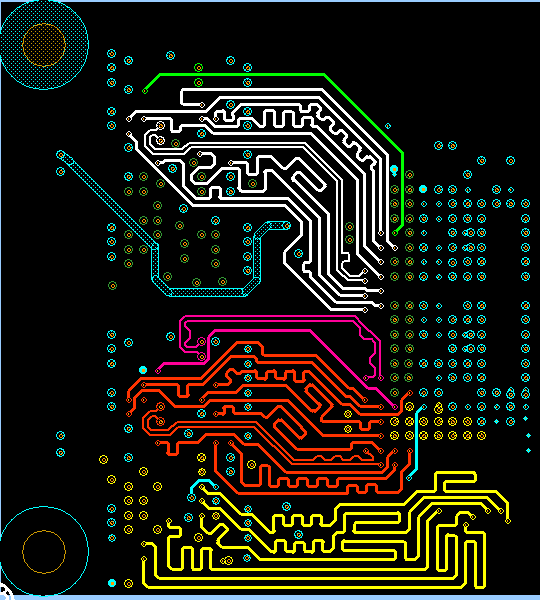

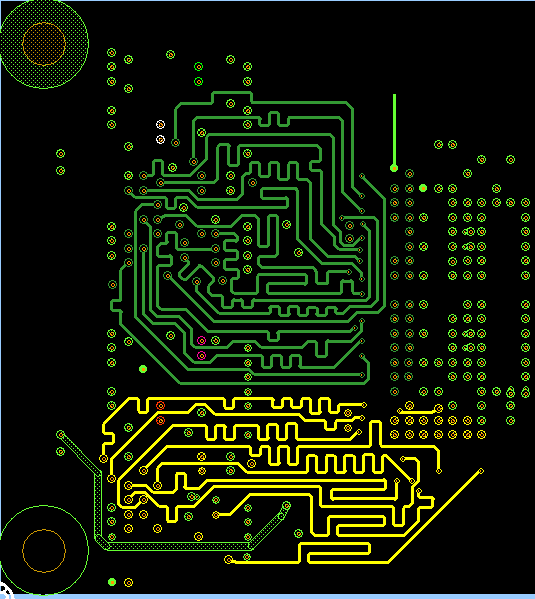

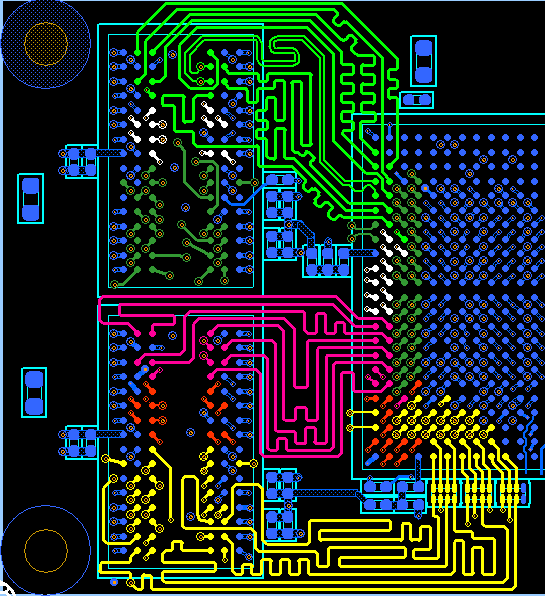

Прошу покритиковать трассировку DDR3. Вводная информация:

- SoC - ADSP-SC587 (Analog Devices)

- 2 независимых контроллера памяти, каждый поддерживает 16-bit single memory IC

-

У производителя несколько необычные рекомендации по терминированию:

- десятки Ом последовательно для control and address

- сотни Ом на землю/питание для pull-up/down для индивидуальных сигналов дифф пар

- подробнее тут - https://www.analog.com/media/en/technical-documentation/application-notes/ee387.pdf

- Во вложение скриншоты по слоям

-

Трассы выделены цветами:

-

Memory controller 0:

- Control/address/clock - желтый

- Lower byte lane - сиреневый (pink)

- Upper byte lane - красный

-

Memory controller 1:

- Control/address/clock - темно-зеленый

- Lower byte lane - белый

- Upper byte lane - светло зеленый

-

Memory controller 0:

-

Стек:

- везде импеданс 50 Ом, по рекомендации производителя

- 2-й слой: сплошная земля

- 5-й слой: +1.5В. Минимальное расстояние от трасс до края полигона - 1.5мм

Буду рад любой критике, спасибо.

-

Именно поэтому из 1G рулят марвелы (с украденным даташитом) и микрелы, а остальных жлобских пиндосов в топку.

Vitesse? Там и документация доступна. И покупка - на digikey-е

хоть поштучно бери. (речь, естественно, про однопортовые)

Сами использовали в паре проектов VSC8211 - все хорошо, проблем не было.

-

Буквально на днях было:

http://electronix.ru/forum/index.php?showt...t&p=1002770

Может и не актуально для ТС (т.к. не все контроллеры поддерживают данную feature),

но решил добавить для полноты картины.

-

Только мне кажется, что вы и uriy говорите о разных вещах. Если я правильно понял вам

необходимо дизассемблирование/декомпилирование, а uriy говорил о модификации загрузочного файла.

Поправьте, если я не прав.

ps. Не знаю какое у вас семейство, но, ЕМНИП, у 54x (и скорее всего у 50x, 51x и 52x) семейства

немного изменился формат ldr. Описание изменений - в hardware reference manual

-

Но потом мне сказали что данный тип процессора не поддерживает работу со строками.

Извините, но это полнейший бред.

Используйте atof (или sscanf) и не заморачивайтесь

-

Что мешает по ОЕ и I2С отключать/переключать?

То, что матрица ничего не знает о том, что ей надо по своему входу ОЕ игнорировать обмен по i2c.

Еще раз уточню, что под фразой ТС "выбор самой матрицы делать через порт OE" я подразумеваю что он

собирается использовать ОЕ вход матрицы чтобы отключать реакцию матрицы на обмен по i2c.

Если я не прав, пусть ТС меня поправит.

-

выбор самой матрицы делать через порт OE

OE - это output enable матрицы? Если да, то не получится, т.к. он применим только шине данных, но не к i2c.

Если адреса устройств разные!Да. А у MT9P031 они одинаковые и без возможности изменения.

-

Как правильно?

Правильно подключать к 548 блекфину DDR память

-

Если допустим взять I2C в LPC он порадует Вас своей аналогией как у атмела ,

:bb-offtopic:

Улыбнуло :) А ничего что родоначальником i2c является NXP (в те времена еще Philips)? И именно их реализация является стандартом де-факто :laughing:

-

-

-

-

Где-то так:

.... I0=0; R0=[P0++]; LSETUP (lp_begin, lp_end) LC0=P5; lp_begin: (R7,R6) = byteunpack r1:0; // r7.h=Y2; r7.l=cr1; r6.h=Y1; r6.l=cb1 R5 = pack (R7.h, R6.h) || W[I2++]=R7.L; [P1++]=R5; lp_end: MNOP || W[I3++]=R6.L || R0=[P0++]; ....

За правильность не ручаюсь - проверить нет возможности.

PS. Еще можно попробовать с помощью DMA...

-

А можно ли....

В DxD+Exp внутри одного проекта скопировать полностью один Design в другой вместе с платой, констрейнами и всем-всем-всем? Ну, например - развел я плату mydesign_usb, и хочу сделать теперь mydesign_ethernet, в котором оставить почти всю разводку и схему от прародителя, но заменить трансивер (одну микруху) и разъем. При этом все внутри одного проекта должно быть.

А вам нужно именно внутри одного проекта? Так, afaik, нельзя. А скопировать проект со схемой и разводкой можно через "Job management wizard".

-

Ну хотя бы подскажите, какой зазор долен быть между КП B1(или A1) разъема по отношению к ближайшему краю ПП разъема? А то с чертежа разъема в спецификации этого не понять.

А вы возьмите какой-либо reference design и измерьте...

Вот, например. Проверено, данная плата прекрасно входит в 1-х слот и работает :)

-

К сожалению, блэкфин не позволяет подключать к нему DDR.

54х серия позволяет

-

А посмотреть в product selection guide религия не позволяет?

XC3S1500 / XC6SLX45------------------------------------

Logic Cells: 29,952 / 43,661

CLB Flip-Flops: 26,624 / 54,576

Maximum Distributed RAM (Kbits): 208 / 401

Total Block RAM (Kbits): 576 / 2,088

Dedicated Multipliers / DSP48A1 Slices: 32 / 58

Memory Controller Blocks: 0 / 2

Configuration Memory (Mbits): 5.2 / 11.4

Packages: FG320 (19х19 мм), FG456 (23х23), FG676 (27х27) / CSG324 (15х15), CSG484 (19х19), FG484 (23х23), FG676 (27х27)

-

А эти регистры в AMD64 архитектуре - 128 разрядные. Они тоже были таковыми в х86?

Да, тоже. Другое дело, что в AMD64 их в два раза больше (16).

-

Режим загрузки на плате 0.

Режим 0 - это выполнение из флэш, без загрузки.

Вам нужен режим 1.

-

у блекфина, насколько я знаю, очень большие накладные расходы на переключение контекста.

Которые компенсируются большой тактовой частотой.

FreeFTOS это что? Где можно скачать?Я расматриваю комплекс VDK и блэкфин.IMHO, VDK - кака.

Помимо вышеназванной freertos, советую посмотреть на ucOS/II и scmRTOS.

-

Есть. Двухпортовое ОЗУ называется.

Например:

http://www.idt.com/?catID=58642&loc=col1

Только стоят они весьма серьезно.

-

1)

Transition (переключение между банками) - число тактов когда AMS[]=1 при каждом чтении/записи или когда к разным банкам обращаемся? или когда к SDRAM лезем?

Всегда ли оно есть или не вставляется?

There are two cases where contention can occur. The first case is a readfollowed by a write to the same memory space.

....

The second case is back-to-back reads from two different

memory spaces. In this case, the two memory devices addressed by the two

reads could potentially contend at the transition between the two read

operations

Выше под "memory space" подразумевается банк асинхронной памяти.

2)AMS[].

Допустим идёт запись данных в одну и туже ячейку памяти много раз подряд.

AMS[] будет дёргаться для каждого слова или опустится вниз на время всей передачи данных?

At the end of the hold period, AOE deasserts unless this bus cycle isfollowed by another asynchronous read to the same memory space.

Also AMSx deasserts unless the next cycle is to the same memory

bank.

-

ЭтоСтильПаскаль

вотЭтоКэмел

а_это_с_подчеркиваниями

-

Легко. Если в С выключить оптимизацию, включить дебаг и написать специально так, чтобы компилятор не понял, что от него хотят.

И это понятно. Но речь шла не про "C vs ASM" в общем случае, а про "C optimizer vs ASM".

...Вот примеры от TI...И от AD:

http://www.analog.com/static/imported-file...160113EE149.pdf

http://www.analog.com/static/imported-file..._transcript.pdf

http://www.analog.com/static/imported-file...kfin_slides.pdf

Подключение DDR3. Замена (swop) битов в байте

в Цифровые схемы, высокоскоростные ЦС

Опубликовано · Пожаловаться

Нет, не нужно.

PS. В DDR3 тоже не нужно, если нормальный контроллер (не i.Mx)