Самурай

Участник-

Постов

730 -

Зарегистрирован

-

Посещение

-

Победитель дней

4

Весь контент Самурай

-

-

Антиалайзинговый фильтр у Вас немного странный... Нормальный должен давить все, что выше 125кГц, и не начинать давить, как у Вас, а заканчивать! Т.е. эти самые 40дБ должны быть если и не на 125кГц, то хотя бы на 150кГц... Ну это если по честному нужно не менее 40дБ подавления всего не нужного в Вашей полосе 0...100кГц. Дальше, неоднородность АЧХ это конечно хорошо, но у фильтра есть еще и неоднородность групповой задержки... Особенно сильной в полосе 50...100кГц. Я не знаю Вашей задачи, может быть это и не важно, а может и нет... Еще чисто для уточнения: АЦП 4-х канальный, Вы используете только 1 канал? Если нет, то частоту дискретизации 250кГц надо делить на количество каналов...

-

Что мешает прочитать документ, на который Вы дали ссылку полностью? Там же чуть выше: B4096: 4096 Peak Ops (operations/per clock) B4096 (8x16x16): 53540 LUT, 105008 FF, 562 DSP Очевидно, что Ваши подозрения не имеют оснований...

-

DC LPF

Самурай ответил C2000 тема в Алгоритмы ЦОС (DSP)

Может быть и есть какой способ, но Вы сначала скажите, чем этот "всплеск" Вам мешает? Что у Вас за сигналы? Какая задача? И вообще, если Вас не устраивает просто скользящее среднее, то может подойдет скользящее среднее с децимацией (он же CIC), там буфер не нужен... -

DC LPF

Самурай ответил C2000 тема в Алгоритмы ЦОС (DSP)

:))))) Ладно, открою один секрет - ЛЮБОЙ фильтр дает всплеск на старте... -

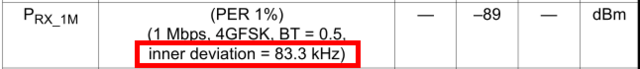

Ну, про полосу Вы же сами пишете, что она тоже увеличилась?:) За цифровой домен сомнений нет, все частоты должны пропорционально поменяться, включая и полосу (если не трогать настройки). Тогда согласно формуле: логично предположить, что и девиация должна быть больше на 20%. Ну это при условии, что все аналоговые и аналого-цифровые блоки трансивера такое повышения частоты вытерпят:)

-

Ну я же говорю, для 4GFSK полоса будет уже, чем для 4FSK, не в 83/58 раз конечно, но уже. Опять же Carson’s Rule по ссылке выше это для случая, когда в полосу попадает 98...99% мощности, что наверно перебор, т.е. полосу можно и сузить. Нормально.

-

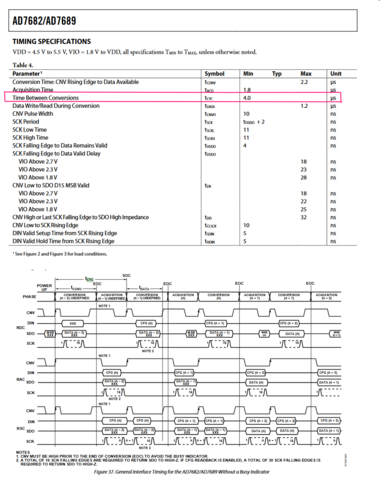

Пять минут гугления и мы находим ответ на родине трансивера. Тут и вовсе далеко ходить не надо. Даташит, стр.6: Да, цифры с первой ссылкой немного отличаются, но во-первых, слегка разные модуляции, а во-вторых, могут отличаться методики измерения мощности сигнала. Но для начала вполне достаточно и этого, потом подогнать по вкусу.

-

Да не будет он холодным, тем более на двух слоях. Это не говоря о том, что на двух слоях его не развести, а если развести, то велком "у меня источник не работает, па-ма-ги-те!". Сами Vishay на дев-борде делают минимум 4 слоя, а на 10А варианте и все 6. Еще из нюансов: даташит молчит как раба об лед о любых условиях измерения температуры! Видно сказывается менталитет, либо местный, либо наш родной... Есть только одинокий график температуры от тока (но где и как получен - хз), на котором уже холодом не очень то пахнет - 55С для 5А (но правда для 48В входного). Тепловое сопротивление кристалл-среда выглядит несколько фантастично (12C/W), при этом ни полслова, на чем измеряли, если как все нормальные люди на своих отладочных платах, то это 70мм х 50мм и 6 слоев с кучей переходных. Но вообще, добра этого много (доступ через впн), наверно и у Китая что-то похожее уже есть. И да, все, что касается тепловых характеристик, рекомендую смотреть у нормальных производителей, что бы потом сюрпризов не было... или повторять один в один дев-борду.

-

Графика в матлабе

Самурай ответил _sda тема в Вопросы системного уровня проектирования

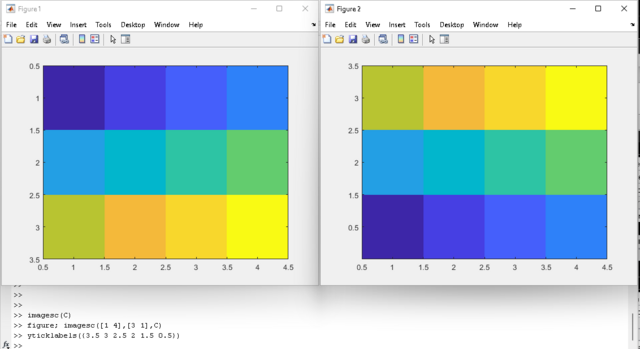

Так, а вариант от vervs? Он то проще будет... -

Графика в матлабе

Самурай ответил _sda тема в Вопросы системного уровня проектирования

Можно, см. ф-ю yticklabels -

Два триггера защелкивают SCL, первый по заднему фронту SDA, второй по переднему фронту SDA. Получаем два сигнала признака старта/стопа. Оба эти признака с автосбросом (синхронным), если, конечно по SDA не одни нули слать, что как-бы возможно, но очень маловероятно. Можно и асинхронный сброс придумать, дабы не зависеть от данных. Полностью от асинхронщины наверно не избавиться, но явной порнографии вроде нет:)

-

TPS628436: КПД под 80% обещают для 10мкА. Что там с другими параметрами не смотрел...

-

Странный какой-то у Вас фильтр... Смотрим передаточную функцию: \(H(z)=\frac{a0+a1*z^{-1}+a2*z^{-2}}{1+2*z^{-1}+z^{-2}}\) И видим двойной полюс на единичной окружности на частоте Fs/2. Из чего следует, что: 1. Данный фильтр имеет смысл только в одном случае, а именно когда на этой же частоте расположен и двойной ноль. Во всех остальных случаях фильтр будет неустойчив или на грани устойчивости, это не считая дико-кривой АЧХ:) 2. Числитель передаточной функции имеет всего лишь 2-й порядок, а это значит, что он задает расположение только 2-х нулей на z-плоскости. Но из предыдущего пункта следует, что эти нули должны быть а) двойные и б) лежать на частоте Fs/2. Т.е. совпадать с полюсами фильтра. Т.е. числитель и знаменатель сокращаются и остается... константа:))). Но, позвольте, а где же тогда фильтр???:) Где-то у Вас ошибка...:)

-

Да, ошиблись. Переходной процесс от фильтра будет всегда, нет переходного процесса - значит нет фильтра (точнее есть, но с одним коэффициентом:))) ). Очевидно, что в общем случае для произвольного сигнала уменьшить длительность переходного процесса можно только ослабив требования к фильтру, т.е. уменьшив его порядок. Вы не сказали, как сильно надо давить и какая переходная зона, может Вам КИХ 6...10-го порядка за глаза хватит, в том числе и по искажениям:)

-

Да. Нет. Надежды на что? В чем именно не помощник?

-

Переходной процесс. Он не успел закончиться...

-

Работа сайта и сервера

Самурай ответил admin тема в Новости и обсуждения сайта и форума

Спасибо, работает. -

Работа сайта и сервера

Самурай ответил admin тема в Новости и обсуждения сайта и форума

В темах Neoclassic и Classic 4.5 2 вот такая ошибка сейчас, когда заходишь на https://electronix.ru/forum/ : Браузер FF 99.0.1 и Edge 111.0.1661.51 -

Работа с GUI в Матлаб

Самурай ответил _sda тема в Вопросы системного уровня проектирования

Help Matlab-а? f = figure; f.Position(3:4) = [280 210]; figure(f); plot(x,y) -

Как предположение: У Вас сигнал BlockBytesLeft от 0 до 8, следовательно вот тут: с точки зрения синтезатора возможен и вот такой вариант: Block_ShReg <= S_AXIS_TDATA(8*8-1 downto 0) & Block_ShReg(63 downto 8*8); Что разумеется ему не понравилось... Дополнение: Насчет разумеется я возможно и погорячился, нужно смотреть, что на такое говорит стандарт:)

-

Что-то у Вас все перемешалось... Вообще непонятно, что тут может быть непонятного?:) Это обычный усилитель с ЦАП и I2S интерфейсом, то, что он D-класс как-бы вообще фиолетово, ну да, где-то внутри есть либо ШИМ, а скорее всего сигма-дельта модулятор (совмещенный с ЦАП), ну и что? Со стороны пользователя обычный классический I2S интерфейс (либо TDM режим, не принципиально). Подключайте к Вашему процессору напрямую и подавайте обычные PCM отсчеты, не надо ничего пересчитывать ни на каком сигма-дельта калькуляторе...

-

организация семплирования

Самурай ответил Maverick_ тема в Алгоритмы ЦОС (DSP)

Если все нарисованное Вам самим делать, то самое правильное, это выбрать такую частоту сэмплирования, которая а) будет Вам удобна и б) удовлетворять Котельникову:) А частота 5.714МГц (точнее 40/7 МГц) если погуглить, пошла от древнего (1997г.) комплекта м/с Zarlink GP2015/GP2021 для создания приемника GPS. В чем ее удобство, сходу понять не смог, возможно, просто особенности данных м/с...