RedHeadIvan

Свой-

Постов

136 -

Зарегистрирован

Весь контент RedHeadIvan

-

Синтезатор ЛЧМ

RedHeadIvan ответил RedHeadIvan тема в RF & Microwave Design

Элементарным поиском я владею) Нужная полоса у ГУНов от AD начинается слишком высоко по частоте -

Синтезатор ЛЧМ

RedHeadIvan ответил RedHeadIvan тема в RF & Microwave Design

Да, выглядит печально. Вероятно, так сделано большинство интегрированных ГУНов... А найти ГУН внешний с полосой хотя бы в гиг - сложно, однако. При чем не только в непосредственной близости в каком-нибудь ЧиДе/Терре, но и у тех же самых AD -

Синтезатор ЛЧМ

RedHeadIvan ответил RedHeadIvan тема в RF & Microwave Design

Потому такой вопрос и возник) Синтезатор - кусок НИР, и никаких четких входных данных, увы, нет. Думаю, что-то вроде 200-300 МГц за миллисекунду близко к желаемому -

Синтезатор ЛЧМ

RedHeadIvan ответил RedHeadIvan тема в RF & Microwave Design

А в чем проблема автокалибровки? Внешний VCO использовать не хочется, должно получиться максимально простое устройство -

Синтезатор ЛЧМ

RedHeadIvan опубликовал тема в RF & Microwave Design

Добрый день, коллеги! Есть задача разработать управляемый синтезатор ЛЧМ сигнала. На данный момент предполагается использовать какой-нибудь простой DDS, типа AD5932, который будет являться опорой для ФАПЧ (ориентировочно ADF4350). Это позволит сформировать необходимую полосу сигнала с нужной формой. Далее предполагается поставить смеситель и ГУН, выводящие сигнал на нужную несущую. Диапазон частот - до 8 ГГц. Никаких специфических требований к фазовым шумам не предъявляется, наличие DDS - обязательно, т.к. может возникнуть потребность в более сложных сигналах. Можно ли вообще таким образом формировать сигнал? Будет ли корректно работать фазовый детектор/ГУН внутри ФАПЧ? Возможно, есть еще какие-то узкие места, очевидные более опытным разработчикам? -

Моделирование СВЧ схемы

RedHeadIvan ответил bamgran тема в Предлагаю работу

ADS, например, не любит моделировать вертикальные КМПП, в том же SiPro. Сам недавно столкнулся с этим, в итоге пришлось пихать плату в CST и ждать... Зато я точно уверен в результате) -

Динамический keepout внутри place replicate

RedHeadIvan ответил RedHeadIvan тема в Cadence

Если цепь одна, то он не считается за island. К тому же, если я подвину статический шейп, то вырез островка так и останется дырой в динамическом шейпе -

Динамический keepout внутри place replicate

RedHeadIvan опубликовал тема в Cadence

Здравствуйте, коллеги! Внезапно столкнулся с проблемой небольшой. Есть кусок топологии, многократно повторяющийся и имеющий вырез в опорном слое. Импортируется в борду послойно из CST в виде статических шейпов. При залитии слоя динамическим шейпом той же цепи кусок динамики появляется внутри выреза в статике. Решил прикрутить в place replicate на нужном слое кусочек route keepout, но он почему-то туда добавляться не захотел. Можно, конечно, до присвоения динамическому шейпу цепи удалить все изолированные области, появляющиеся внутри статических шейпов, но это не самое удобное решение, потому что статические части есть необходимость двигать. Решал ли кто-нибудь подобную задачу? -

Горячая линия по САПР Cadence Allegro

RedHeadIvan ответил PCBtech тема в Cadence

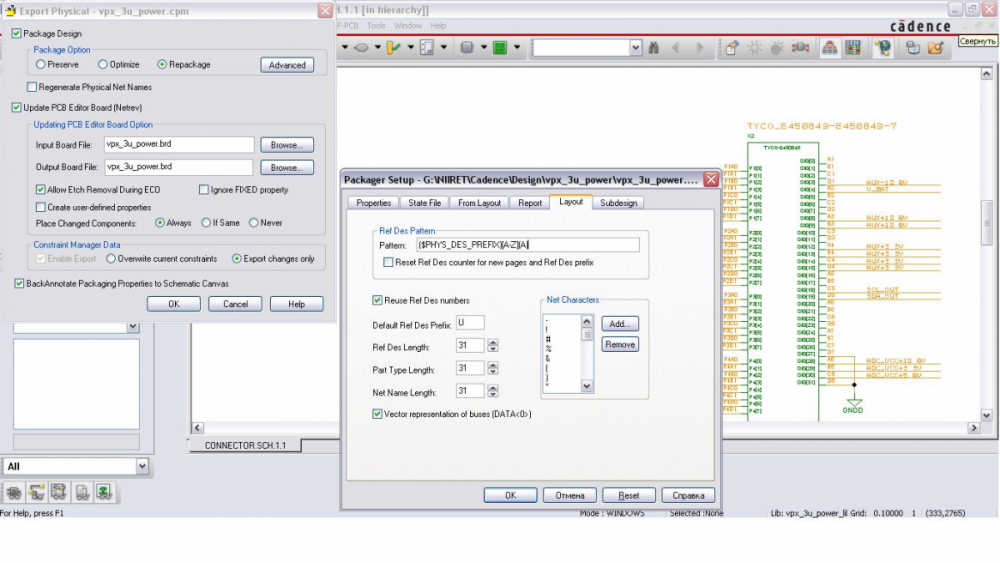

Не уверен, как это работает в Capture, но в DE-HDL делаю так: После добавления новых компонентов не делать полный ренамбер, паковать с опцией "Preserve". Это сохранит всю существующую нумерацию, назначив новым компонентам новые уникальные номера. Втянуть изменения в РСВ. Теперь упаковать схему с опцией Repackage и заданным Refdes_Pattern-ом вида "($PHYS_DES_PREFIX)[A-Z](A)", в котором задано использование букв, вместо цифр Поставить галочку «Reset Refdes counter…» Втянуть изменения в РСВ. Рефдезы должны стать вида RA,RB,RC...RABC и т.д. При такой нумерации ни один компонент не получит рефдеза, который существовал в предыдущей нумерации, в итоге все останется на своих местах. А теперь делаем еще раз Repackage, только с нормальным паттерном вида "($PHYS_DES_PREFIX)[0-9](1)". -

Горячая линия по САПР Cadence Allegro

RedHeadIvan ответил PCBtech тема в Cadence

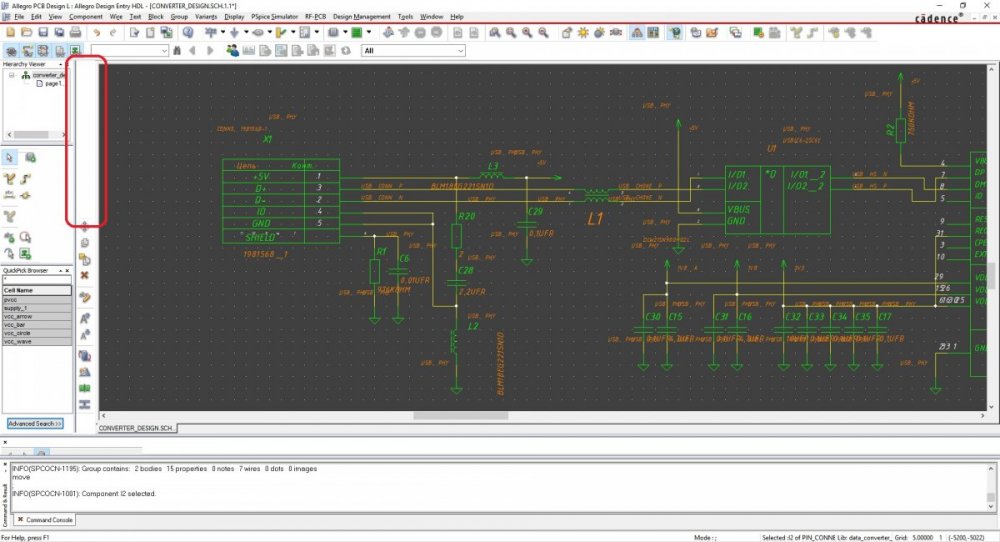

Есть ли какая-нибудь возможность вернуть дефолтное положение тулбаров в DE HDL? Случайно сдвинул тулбар Add с места, а обратно он не встает -

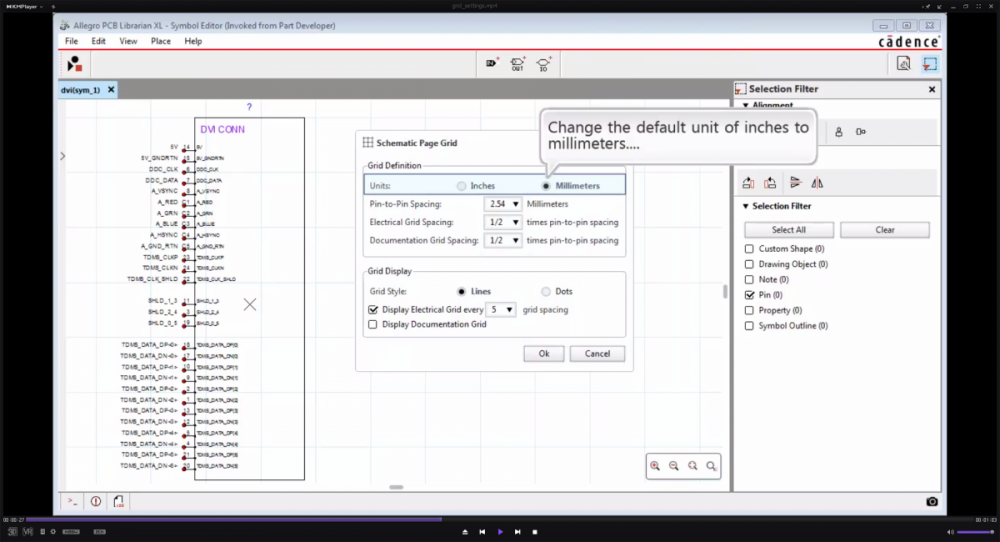

Сетка в новом Symbol Editor

RedHeadIvan ответил RedHeadIvan тема в Cadence

У меня после указанных манипуляций и установки 51 хотфикса ничего не изменилось, выглядит так же как было Никакого решения пока не нашлось альтернативного? Новый редактор вроде удобный, но из-за сетки работать невозможно, все равно с HDL сверяться надо на предмет промаха И можно cpm файл для примера? Вдруг какие-то другие настройки проекта расходятся -

Потоковая передача данных АЦП

RedHeadIvan ответил RedHeadIvan тема в ARM, 32bit

В силу другой направленности специальности DMA раньше не использовал, поэтому путаюсь. Получается, надо циклически заполнять через DMA и отправлять по USB некоторый массив? На FS же нет своего DMA Но ведь в этом случае все равно USB будет в роли догоняющего: DMA кладет данные, пока USB их отправляет. Возможны коллизии? Не совсем в голове складывается полная картина, буду очень признателен за небольшие разъяснения -

Потоковая передача данных АЦП

RedHeadIvan опубликовал тема в ARM, 32bit

Доброго времени суток, коллеги! Есть задача максимально близко к RealTime передавать данные, получаемые с АЦП с частотой до 100 кГц, в обработчик в компьютере. Взял FreeRTOS, сделал в прерывании АЦП по EOC передачу значения в очередь, которую разбирает FS USB Пока работал на малых выборках косяк не заметил, но когда увеличил время оцифровки увидел, что USB не успевает разобрать очередь и как только количество точек выходит за пределы очереди - все, начинается дичь Возможно, кто-нибудь может подсказать, как грамотно построить процесс передачи? Собственно, реализация треда передачи, где SendString, по сути, CDC_Transmit_FS void StartCommandHandler(void const * argument) { osEvent event; for(;;) { event = osMessageGet(DataQueueHandle, 0); if (event.status == osEventMessage) { uint16_t data = event.value.v; p = itoa(data,buffer,radix); SendString(p); } } } Буду благодарен за любую подсказку) -

Сетка в новом Symbol Editor

RedHeadIvan ответил RedHeadIvan тема в Cadence

пробовал, получается фигня. странность в том, что компоненты из 16.6, нарисованные в миллиметровой сетке, ложатся в местную "дюймовуйю", это сбивает с толку еще больше в Part Developer символ пропал, это правда. почему и куда - так и не понял -

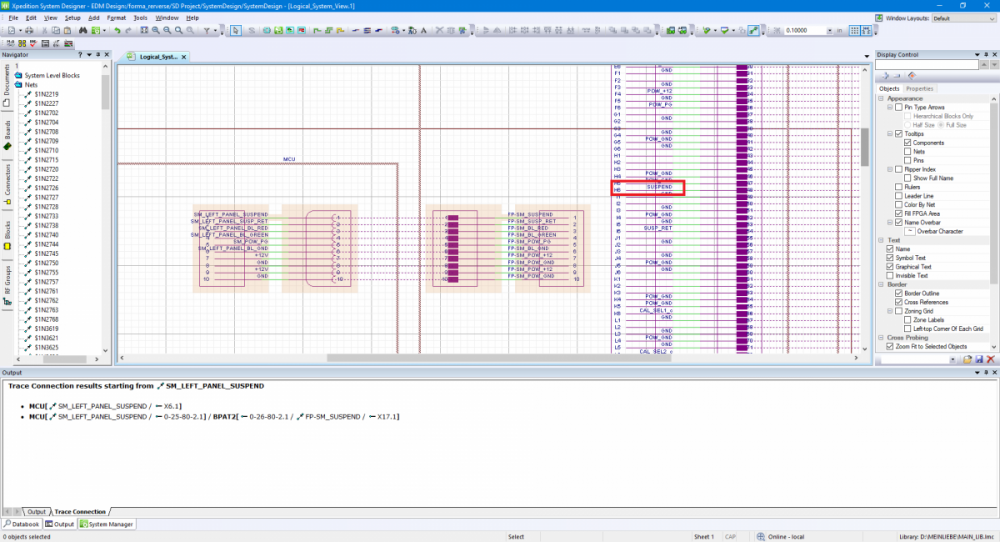

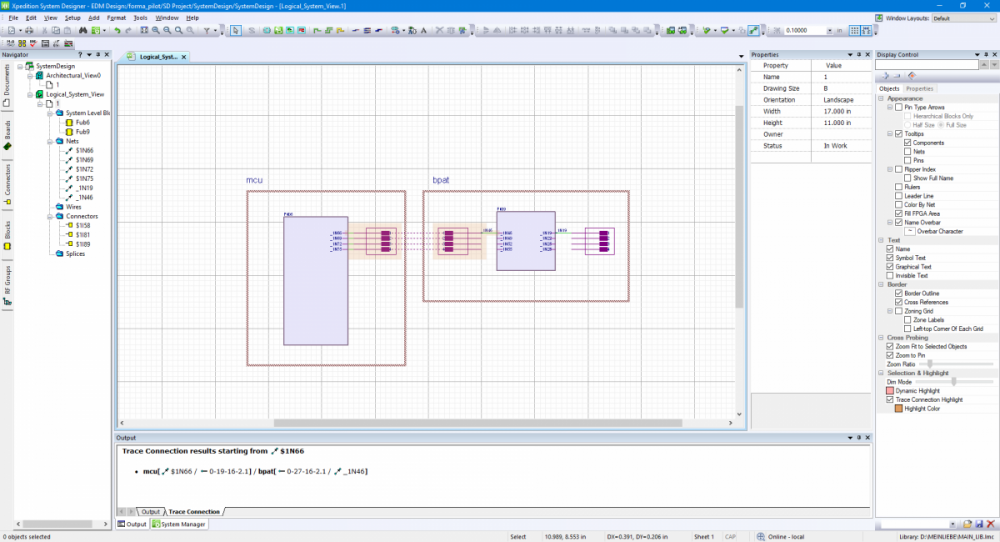

Для проверки я сделал два проекта. На первой картинке проект, собранный из имеющихся плат. В схематике сигнал SUSPEND и FP-SM_SUSPEND в одной цепи и там прекрасно кросспробятся, в SD нет. На второй картинке проект, созданный сразу в SD. В блоке на плате bpat просто закоротка, т.е. 1N46 напрямую связан с 1N19. Тут они так же не кросспробятся Правильно ли я понял, что данные схематика при кросспробинге в SD абсолютно не учитываются при любом методе построения проекта?

-

Кросспробинг между платами

RedHeadIvan опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Добрый день! Подскажите, как делается кросспробинг в Systen Designer через плату? Есть три платы, сигнал проходит насквозь через одну из них. Trace Connection в схематике платы ассоциирует пины входного и выходного разъема, как и должно быть. При импорте проекта в SD Trace Connection показывает только mate-разъемы, больше ничего. -

Сетка в новом Symbol Editor

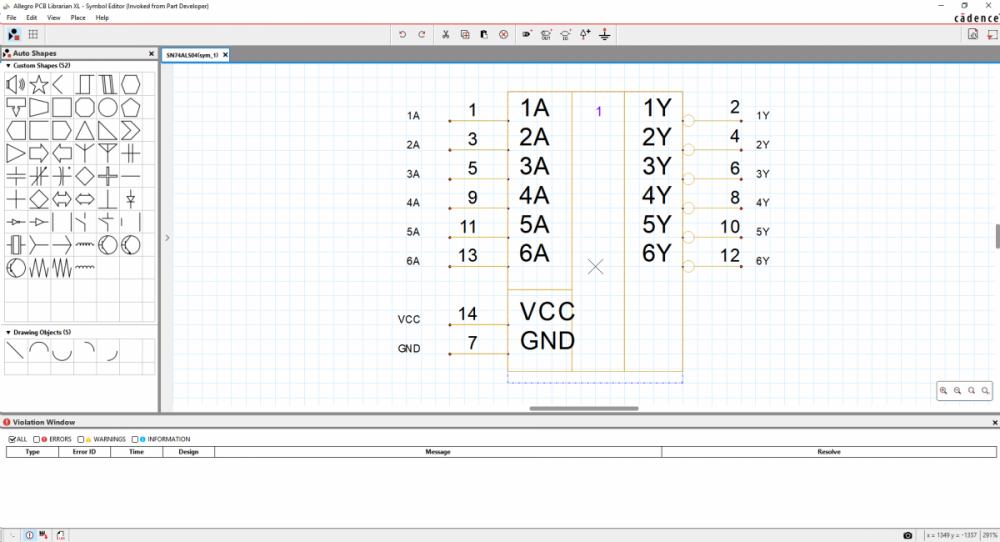

RedHeadIvan опубликовал тема в Cadence

Доброго времени суток, коллеги! Перешел на 17.2, поставил хотфикс 048 и обнаружил новый редактор символов. Выглядит неплохо, но....сетка дюймовая, в самом редакторе альтернатив не предлагается. Компоненты у меня все в 5мм, так что это порядочная трагедия. Пробовал менять System Unit в самом Part Developer, но после небольших раздумий все просто подвисает. Изменений никаких, естественно, не происходит. Может сталкивался кто с такой проблемой? Или знает, где лежит какой-нибудь файл конфигурации, чтоб его можно было руками поправить? Буду благодарен за любую подсказку UPD Grid Factor меняется нормально и в файле проекта новый рисуется. Узнать бы, как называется параметр, отвечающий за единицы измерения UPD_2 Вот так выглядит изменение сетки в их обучающем видео А так выглядит то же самое у меня Вообще творится какая-то дичь... Символ из дюймовой сетки ложится в 5мм в HDL... -

Вопросы по Agilent ADS

RedHeadIvan ответил Halo_Gen тема в RF & Microwave Design

А разарбатывал кто-нибудь Вилкинсона в ADS? Design Guide обещает мне достаточно хорошие параметры, а на деле, при контрольном моделировании в CST, получается не очень... Не совсем понимаю, как коррелирует моделирование в Schematic с топологией в Layout . Еще Design Guide все время впихивает в только что смоделированный делитель просто модели резисторов, без падов. учитывает ли он при проектировании размер падов, или Gap это уже вместе с падами и предполагается запаивать резисторы прям на хвосты моста? -

Соединения в System Designer

RedHeadIvan опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Доброго времени суток! Решили тут начать пользоваться SD, сразу возникли вопросы 1) (наиболее общий) Есть ли какое-то принципиальное отличие разъема, который ставится в Schematic от разъема, который ставится в SD? 2) Когда вытаскиваю разъем из Databook, УГО всегда по умолчанию generic, а не библиотечный символ. приходится делать RClk-Replace Part/Symbol с приоритетом схемы над либой. Можно ли как-то по умолчанию нормальное УГО ставить? 3) В EDM Librarian Cockpit сделал библиотечному Board Connector комплементарный Cable Connector, т.е. соответствующие свойства отображаются во вкладке Connector, Cable Connector без падстака, оба значатся друг у друга как Mate. В SD Mate не делается, говорит type mismatch. Как правильно делается соединение плат друг с другом? Может, мой подход изначально неверен? -

Схема соединений в MG Xpedition

RedHeadIvan ответил RedHeadIvan тема в Документация

Это ожидаемо, большинство зарубежных САПРов к ГОСТу не приучены. Но неужели настолько, что даже какое-то сопоставимое подобие Э4 сообразить нельзя? Ведь если System Designer разрабатывают, значит это кому нибудь нужно :) -

Схема соединений в MG Xpedition

RedHeadIvan опубликовал тема в Документация

Здравствуйте, комрады! Есть большой проект, сделанный в Менторе, который представляет из себя некоторое количество проектов плата-схема. На все это дело нужно оформить Э4, желательно максимально близко к ГОСТ, с возможностью дальнейшей реализации сквозного проектирования. Самое очевидное решение - попробовать собрать все в EDM (в версии 2.3, или xDM в более ранних версиях). Однако, как сделать это правильно, разобраться пока не удалось. Максимум, что получилось - собрать несколько плат в один проект, а как связать их на схеме - неизвестно. Занимался ли кто-нибудь чем-то подобным? Возможно ли вообще сделать в Менторе Э4? Информации крайне мало, а по обучающим видео самого Ментора кажется, что в итоге получается не совсем схема соединений, а просто удобная блочная иерархия проекта. Буду благодарен за любую информацию -

Пайка SMA

RedHeadIvan опубликовал тема в Пайка и монтаж

Здравствуйте, коллеги! Недавно пришла плата с кучей КМПП, на которые надо запаять SMA разъемы. Также был пробник, с помощью которого нужно было оценить качество переходов. При анализе выяснилось, что характеристики реального перехода сильно уступают модели. Методом научного тыка выяснили причину: диэлектрик в разъеме от нагрева корпуса при пайке ног немного вылез наружу и между разъемом и платой появился зазор, буквально 0,2 мм, который и портит характеристики. В связи с эти вопрос: сталкивался ли кто с такой проблемой? Может кто знает, как правильно запаять разъемы? -

На таких частотах FR-4 подойдет без проблем. Потери, по сравнению с тем же роджерсом, значительные, но при достаточно тонком слое потеряется меньше половины децибелла

-

Крепежные отверстия

RedHeadIvan ответил KAlexander тема в Cadence

У нас для крепежных отверстий, если только не заземляемся через корпус, используются механические символы с соответствующими outline и keepout. Вопросов никогда не возникает -

Горячая линия по САПР Cadence Allegro

RedHeadIvan ответил PCBtech тема в Cadence

С Capture пока отношения не сложились, рисуем в HDL и разводим в PCB Design