ZeratulSC007

Участник-

Постов

97 -

Зарегистрирован

-

Посещение

Весь контент ZeratulSC007

-

Поиск аналога

ZeratulSC007 ответил ZeratulSC007 тема в Компоненты

Спасибо за такой развернутый ответ. Я в той категории, которой нужно будет десять микросхем) С покупкой микросхемы: разве не получается, что именно наш российский дистрибьютор завышает цены? В любом случае от голословия мало пользы, спасибо за рекомендации к размышлению -

Поиск аналога

ZeratulSC007 ответил ZeratulSC007 тема в Компоненты

Нет, не обращался. Техподдержку Analog Device Insruments (слышал только об Analog Device) или компании Элтех? Нет, думал, что в силу того, что это российский дистрибьютор, будет цена завышена. -

Подключение среды разработки Xilinx ISE к AD16

ZeratulSC007 опубликовал тема в В помощь начинающему

Доброго времени суток! По работе с ПЛИС (Spartan XC3S1400AN, в составе кита от Альтиума) нужно к Альтиуму(16.1) привязать поддерживающуюся версию Xilinx ISE. Вдоль и поперек облазив форум, сайт и документацию к Альтиуму, не нашел поддерживаемую версию. Понятно, что можно взять на два поколения младше (сейчас 14.7, например, 12.х), однако в силу тормознутости интернета на работе качать придется 3-4 часа и хочется выбрать сразу подходящую версию. -

ЖК дисплей и ардуино

ZeratulSC007 ответил ZeratulSC007 тема в В помощь начинающему

Спасибо! Не был уверен в силу своей неопытности, что такой дисплей является обычным) -

Поиск аналога

ZeratulSC007 опубликовал тема в Компоненты

Доброго времени суток. Ищу аналог (адекватную замену) ацп AD9252 http://www.analog.com/media/en/technical-d...eets/AD9252.pdf. Вследствие неопытности не получается подобрать такую замену, что подходила бы и по скорости, и имела достаточную разрядность. Поделитесь ссылками на ресурсы, где можно поискать высокоскоростные ацп. А если кто-то работал с такими ацп, буду рад на них посмотреть) -

ЖК дисплей и ардуино

ZeratulSC007 опубликовал тема в В помощь начинающему

Доброго времени суток. Есть ардуино-Uno и ЖК DV-20400S1FBLY. Дисплей надо подключить к ардуинке. Желательно, начать с каким-нибудь примером, ибо не хочется по незнанию или малоопытности вывести из стоя что-нибудь. На сайте ардуино примеров под этот или аналогичный дисплей я не нашел. Поделитесь, пожалуйста, ссылкой или примером на подключение такого дисплея или аналога) Заранее спасибо -

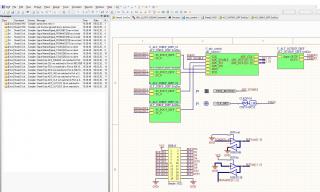

Предупреждения в Альтиум

ZeratulSC007 опубликовал тема в Altium Designer, DXP, Protel

Доброго времени суток. При компилировании проекта Альтиум показывает вот такие ошибки. Интересует вот этот варнинг Map WARNING:MapLib:793 - Bi-directional network HB2 is driven by a constant. В хелпе ничего ни нашел (мой косяк :01: ). В интернете вот такая интересная ссылка. Как я понял, проблема в неполном описании сигнала (нет всех вариантов его значений). Однако эта доработка (описание всех вариантов) не решила проблему. -

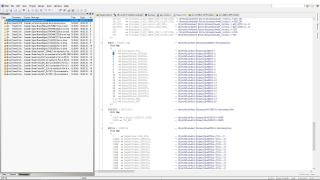

Вопрос по VHDL

ZeratulSC007 ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

Amurak, Tausinov, спасибо! -

Вопрос по VHDL

ZeratulSC007 ответил jenya7 тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте. Надеюсь, вопрос подходит теме топика. Пишу свой модуль обработки сигнала перед VGA, есть рабочий пример кода Library IEEE; use IEEE.STD_Logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; entity jet is port( en : in std_logic; Y : in std_logic_vector(13 downto 0); R, G, B : out std_logic_vector(9 downto 0); MODE_FPGA: in std_logic ); end entity; architecture jet_arch of jet is begin RGB : process(Y, en) variable tmp1: std_logic_vector(15 downto 0); variable tmp2: std_logic_vector(16 downto 0); begin if en = '1' then if MODE_FPGA='1' then case Y(13 downto 11) is when "000" => R <= (others => '0'); G <= (others => '0'); tmp1 := Y&"00"+"0010000000000000"; -- b = 4y + 0.5 B <= tmp1(13 downto 4); when "001"|"010" => R <= (others => '0'); tmp1 := Y&"00"-"0010000000000000"; -- g = 4y - 0.5 G <= tmp1(13 downto 4); B <= (others => '1'); when "011"|"100" => tmp1 := Y&"00"-"0110000000000000"; -- r = 4y - 1.5 R <= tmp1(13 downto 4); G <= (others => '1'); tmp2 := not ("0"&Y&"00") + "01010000000000000"; -- b = -4y + 2.5 B <= tmp2(13 downto 4); when "101"|"110" => R <= (others => '1'); tmp2 := not ("0"&Y&"00") + "01110000000000000"; -- g = -4y + 3.5 G <= tmp2(13 downto 4); B <= (others => '0'); when "111" => tmp2 := not ("0"&Y&"00") + "10010000000000000"; -- r = -4y + 4.5 R <= tmp2(13 downto 4); G <= (others => '0'); B <= (others => '0'); end case; else R <= Y(13 downto 4); G <= Y(13 downto 4); B <= Y(13 downto 4); end if; else R <= (others => '0'); G <= (others => '0'); B <= (others => '0'); end if; end process; end architecture; Интересует конструкция <= (others => '0'). Нашел, что это использование агрегации. Штудирование материала не дало понимания. Объясните глупому студенту) -

SPI

ZeratulSC007 ответил ZeratulSC007 тема в Интерфейсы

Извините за неточное формулирование вопроса. Наноборд - набор разработчика от Альтиума (http://techdocs.altium.com/display/HWARE/NanoBoard-NB1). У него очень широкая периферия, можно попробовать поработать с очень большим спектром задач. Пробую свои силы - делаю первые проекты, чтобы набраться опыта. Мое решение - в проекте в среде Альтиум добавить процессор, spi-контроллер, или же написать свой блок управления spi, завести выходы с блока управления spi на header'ы. Языки: Cи и Verilog Вопрос - куда писать функции управления spi? Есть ли более простая возможная реализация задуманной идеи (сделать spi, с обработкой полученных данных процессором)? -

Работа с САПРом

ZeratulSC007 ответил ZeratulSC007 тема в В помощь начинающему

Да, но по предмету работы нужен именно он. Плата, с которой я работаю, связывается по LPT. Квартус 7, 8 был в ходу, но ни один не смог исправить проблему. Спасибо за ответ! -

Работа с САПРом

ZeratulSC007 опубликовал тема в В помощь начинающему

Здравствуйте! По необходимости работаю с 8-м Альтиумом. Когда в проекте используется верилог, не получается его залить (unsupported version of altera quartus II, использую 8-ю или 11, обе web-edition). Если в настройках выставить ignore version of vendor tools, то возможность залить в ПЛИС предоставляется, но не проходит map design (ошибка 20005). Растолкуйте неопытному, что нужно сделать для того, чтобы проект получилось залить. P.S. С квартусом 7sp3 тоже не получается P.P.S. C версией 9sp2 тоже не получается (альтиум просто не видит эту версию) -

SPI

ZeratulSC007 опубликовал тема в Интерфейсы

Здравствуйте. Пробовую свои силы в проекте с нанобордом (NB-1). Решил сделать SPI и вывести его на одни из хедеров NB-1. Впечатляет функционал альтиума, однако решение представляю смутно. Пока что есть идея сделать проект с процессором, spi-контроллером (он, правда, для NB-2 сделан) и кодом, который будет всем этим управлять. Есть ли возможность более простой реализации? Если взять мое решение, то как и куда пишется код (понимаю, что нужен Embedded project)? Заранее спасибо! -

С лицензией все хорошо, она есть, квартус ничего не просит, когда запускается? У меня такая же проблема была, когда я без лицензии его использовал.

-

Altium designer

ZeratulSC007 опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте. Создаю проект для наноборд-1, в Альтиуме. При компилировании появляется несколько ошибок, которые не получается решить. P.S. Проблему с header'ами почти решил. По глупости не добавил сразу constraint-файл, потом вместо элемента HDR10 сделал 18 портов, назвал из HB.., заработали почти все. P.P.S. Не заработали, теперь выскакивает ошибка HB18 (17 и т.д., если убирать предыдущий) connected to multiply sources. -

Здравствуйте. Пользуюсь Альтиумом, работаю с нанобордом, я могу в этой теме задать вопрос по созданию проекта (не плата)?

-

megafunction

ZeratulSC007 ответил bva_rzn тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Подскажите, зачем megafunction wizard генерирует два вериложных файла, например: PLL_CLK и PLL_CLK_bb. Первый - готовый модуль, а второй? Чем они отличаются и можно ли использовать их в не Quartus'овских проектах? Спасибо -

Еще возник такой вопрос: в проекте Quartus'a использовались программные буферы ALT_INBUF_DIFF. Соответственно, его необходимо поставить и в проект Altium'a. Есть ли такой буфер? Или, поскольку сигнал дифференциальный, можно описать какой-нибудь простейший блок на верилоге и использовать его как буфер?

-

- это добавит сгенерированные файлы к проекту в Altium'e, но все равно надо будет собирать схему проекта? распиновку при этом также делать для Atlium'a, верно?

-

Перенос проекта

ZeratulSC007 опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Делал проект в Quartus 13.0.1, проект на ПЛИС компании Altera. Возникла необходимость перенести этот проект в Altium Designer. Есть ли у Altium'a какие-нибудь средства для быстрой адаптации проекта? Вариант пересборки вручную тоже рассматривается, но хочется сначала узнать о возможностях Altium'a. Спасибо -

Доброго времени суток. Работаю с NanoBoard 1, дочерней платой Altera Cyclone EP1C2Q240С7. В constraint files в иерархии проекта лежит NB1_6_EP1C2Q240.Constraint. Но добавить ее в разделе Devices/Hard Devices не могу, все время слетает с EP1C2Q240С7 на EP1C2Q240C6. Что нужно сделать или чего я не понимаю?)