Dimentius

Участник-

Постов

37 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Dimentius

-

Звание

Участник

Контакты

-

ICQ

Array

Посетители профиля

1 112 просмотра профиля

-

Спасибо!

-

Я первый раз с артиксом работаю, для меня это не очевидно. Вивада "тычет" в -1I

-

Я их тоже видел :), а вот -2 моделька на "минуса" считает? Уже лучше, надо только найти этому подтверждение. Вивада при выборе индастриал предлагает только -1I

-

С ds180, видимо, погорячился, в ds181 указано, что XA и XQ бывают -2I, и то 200ка только XQ Чип старый, наверное

-

Industrial Artix-7

Dimentius опубликовал тема в Работаем с ПЛИС, области применения, выбор

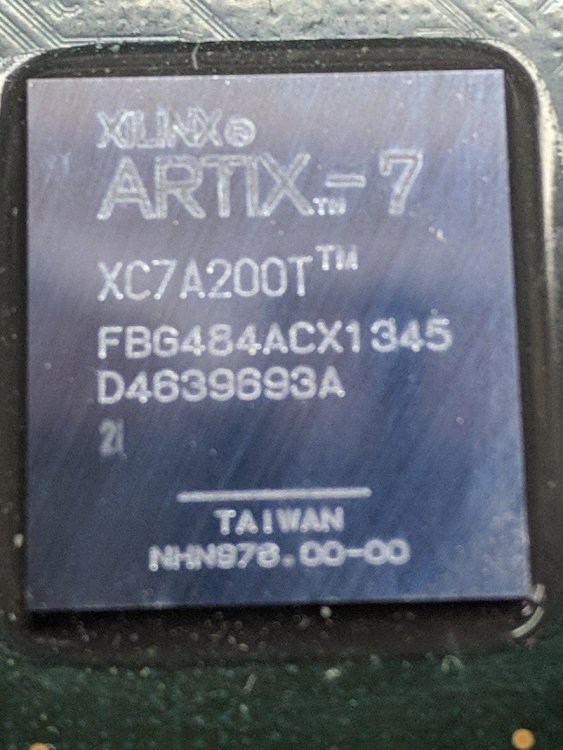

На работе собрали макет платы, на нем стоит плис XC7A200T-2FBG484I 1. Упоминание про микросхемы -2I есть только на сайте хилых, в документах ds180, ds181 про индастриал со скоростью -2 нет инфы 2. Вивада про -2I тоже не знает 3. Чип есть в продаже, например на "диджикей" www.digikey.com/product-detail/en/xilinx-inc/XC7A200T-2FBG484I/122-1866-ND/3925800 Т.е. чип есть, моделей под него нет, это норм или нет ? Спросил "макрогрупп", сделав фото чипа - ответили, что не их поставка, маркировка кривая, и вообще тайм-код не тот, но похоже больше на отписку. Знающие люди, подскажите, такие камни существуют или китайский фейк? Подстава №2: 2.5G Base-X (3.125Gb) на индастриал не поднять, в IP корке, в описании написано что -2 только коммерс и то, только после Вивады 2018.3 (библиотека 16.6, если не путаю) Смотреть в сторону индастриал Кинтекс? -

Ответ "Альтеры" (спасибо Роману Золотухо): In Quartus 9x, there was no limitation on the loop constant setting. However, this depth is being translated into a length and is part of a decision in the tool to determine if an infinite loop exists. Our magic number for loop iterations is not to exceeds the 5000 iteration, else it is interpretted as an infinite loop. Regret to inform you that, this issue had been reported to the software team and they do not plan to change the operation. --- значение VERILOG_CONSTANT_LOOP_LIMIT в "Ква QT" можно только уменьшить, максимальное значение 5000

-

set_global_assignment -name VERILOG_CONSTANT_LOOP_LIMIT ххх не работает ни через .qsf ни через "Assignment -> Settings -> Analysis&Synthesis -> More Settings ... -> Iteration limit for constant Verilog loops" у меня у одного такие проблемы или нет? На 9.1sp2 - задается и работает, проблема в том, что новый проект с чипом C4GX, а его 9ка не поддерживает Требуется подсчитать значение параметра(значение ПСП-28 с большим сдвигом), квартус стопорится с ошибкой: "Error (10106): Verilog HDL Loop error at mpsp.v(6): loop must terminate within 5000 iterations" function int mpsp(input int value, input int psp_type, input int times); bit [31:0] rpsp; begin rpsp = value; for (int i = 0; i < times; i = i + 1)//Error : Verilog HDL Loop error begin case (psp_type) 2: rpsp = {rpsp[30:0], rpsp[ 1]^rpsp[ 0]}; 3: rpsp = {rpsp[30:0], rpsp[ 2]^rpsp[ 0]}; 4: rpsp = {rpsp[30:0], rpsp[ 3]^rpsp[ 0]}; 5: rpsp = {rpsp[30:0], rpsp[ 4]^rpsp[ 1]}; 6: rpsp = {rpsp[30:0], rpsp[ 5]^rpsp[ 0]}; 7: rpsp = {rpsp[30:0], rpsp[ 6]^rpsp[ 2]}; 8: rpsp = {rpsp[30:0], rpsp[ 7]^rpsp[ 3]^rpsp[2]^rpsp[1]}; 9: rpsp = {rpsp[30:0], rpsp[ 8]^rpsp[ 3]}; 10: rpsp = {rpsp[30:0], rpsp[ 9]^rpsp[ 2]}; 11: rpsp = {rpsp[30:0], rpsp[10]^rpsp[ 1]}; 12: rpsp = {rpsp[30:0], rpsp[11]^rpsp[ 5]^rpsp[3]^rpsp[0]}; 13: rpsp = {rpsp[30:0], rpsp[12]^rpsp[ 3]^rpsp[2]^rpsp[0]}; 14: rpsp = {rpsp[30:0], rpsp[13]^rpsp[ 9]^rpsp[5]^rpsp[0]}; 15: rpsp = {rpsp[30:0], rpsp[14]^rpsp[ 0]}; 16: rpsp = {rpsp[30:0], rpsp[15]^rpsp[11]^rpsp[2]^rpsp[0]}; 17: rpsp = {rpsp[30:0], rpsp[16]^rpsp[ 2]}; 18: rpsp = {rpsp[30:0], rpsp[17]^rpsp[ 6]}; 19: rpsp = {rpsp[30:0], rpsp[18]^rpsp[ 4]^rpsp[1]^rpsp[0]}; 20: rpsp = {rpsp[30:0], rpsp[19]^rpsp[ 2]}; 21: rpsp = {rpsp[30:0], rpsp[20]^rpsp[ 1]}; 22: rpsp = {rpsp[30:0], rpsp[21]^rpsp[ 0]}; 23: rpsp = {rpsp[30:0], rpsp[22]^rpsp[ 4]}; 24: rpsp = {rpsp[30:0], rpsp[23]^rpsp[ 6]^rpsp[1]^rpsp[0]}; 25: rpsp = {rpsp[30:0], rpsp[24]^rpsp[ 2]}; 26: rpsp = {rpsp[30:0], rpsp[25]^rpsp[ 5]^rpsp[1]^rpsp[0]}; 27: rpsp = {rpsp[30:0], rpsp[26]^rpsp[ 4]^rpsp[1]^rpsp[0]}; 28: rpsp = {rpsp[30:0], rpsp[27]^rpsp[ 2]}; default : rpsp = 0; endcase end mpsp = rpsp; end endfunction

-

И вопрос "зачем?". Если только представить, что ПЛИС могла бы жить и трудиться лет 10 (могла бы и дольше, но железка устареет, хотя у меня есть примеры когда устройства с ACEX трудятся на благо Родины уже более 10 лет), а трансивер может сдохнуть через сотню часов работы(можно выжечь и за несколько секунд при желании). Как ремонтить устройство, заменой ПЛИС? Это приемлимо, простите, на чипах типа "ethernet свитч" со встроенными phy, когда они там подыхают, но там цена вопроса не более 20$, здесь же порядка на 3 больше.

-

счетчик не от клока

Dimentius ответил jkkj тема в Языки проектирования на ПЛИС (FPGA)

Вроде бы автор сказал, что асинхронный сигнал "серьёзно меньше частоты клока". В плане скважности или по длительности? Все упирается в частоту возникновения "сигнала", если меньше частоты клока, то сигнал можно подать как клок Т-триггера в счетном режиме и, как советовали выше, считать перепады "клоком" -

PowerPC + Wiggler

Dimentius ответил Dimentius тема в Все остальные микроконтроллеры

Пришлось на прошлой неделе вернуться к этому вопросу. Скачал новый "Flash Programmer" и "OCD Commander". Как здесь уже писали, при работе с wiggler-ом проблемы у "Flash Programmer-а" в постоянном срыве из режима отладки в "running" и ограничении в 1024 байта при записи. Пришлось от него отказаться. "OCD Commander" повел себя более достойно и адекватно. Правда перспектива заливать "U-Boot" десятками минут немного расстраивала. Поэтому решил поступить по другому: Написал на асме маленькую программу в линейном коде без всяких вызовов, которая перекладывает данные из одной области памяти в другую, согласно протоколу работы с NOR-flash 28F128J3 от "Intel"(эта память стоит на моей плате). Подготовил "U-Boot" для моей платки(размер составил 2 сектора флешки). Преобразовал оба файла в формат s-records с адресами в Ram ("U-Boot" - 0x01000000, программки - 0x01060000), выгрузил через "OCD Commander" и запустил код по переносу данных. В результате программирование "U-Boot" составило около 30 сек. Думаю, что подобным образом можно сделать на любой платформе. Прикрепляю свой код для примера. Всем удачи. uboot_bootloader.zip -

"Шъерт побъери!" (с) Меня подобная мысль посещала, а вы ее только подтвердили. Я наивно полагал, что контроллер это делает автоматически по "completed". Видать где-то пропустил. Спасибо за подсказку.

-

Долго не занимался данным вопросом, сейчас нашлось время повозиться еще: 1) hid-core не используется, написан свой драйвер 2) Проблема не при подключении драйвера, а при опросе устройства по Ep0, конкретно при получении StringDescriptor и такое впечатление, что при кратности длины дескриптора 8ми байтам.

-

в том то и дело, что HID-устройство(я в описании указал: HID-dev. Int-IN+Int-OUT EPs)

-

Продолжаю "ковырятся", но что самое интересное, под виндой не было ни 5, ни 15ти сек.

-

Пробовал, сократил время с 15 сек. до 5 сек. ;)