verali

Свой-

Постов

80 -

Зарегистрирован

-

Посещение

Весь контент verali

-

Когда проект запускаю под Modelsim AE моделирование идет, а через квесту нет. Как вы думаете в чем может быть причина. PS:Библиотеки для квесты я компилировал через квартус, а потом в файле modelsim.ini прописывал вручную.

-

К сожалению платы пока нет

-

Здравствуйте! Хочу провести симуляцию проекта в QuestaSim. Но после запуска Questa не могу добавить интерисующие меня сигналы всвязи с их отсутствием. Делаю все по шагам, описанным в AN351: 1) В Quartus 14.0 создаю визардом новый проект. 2) Открываю Qsys и создаю систему, включающую nios, pio и on-chip ram. 3) Генерирую файлы testbench: Generate->generate TB system(Simple + verilog) 4) Открываю eclips и создаю новый проект, указываю путь к квесте и путь к файлу .sopsinfo 5) Создаю main.c c текстом программы, собираю проект (build project) Текст программы: #include "system.h" #include "altera_avalon_pio_regs.h" int main () { int leds = 0x1; int i = 0; while(1) { IOWR_ALTERA_AVALON_PIO_DATA(PIO_0_BASE, leds); for (i=0; i<10000; i++); if (leds<255) { leds ++; } else leds = 0; } return 0; } 6) Запускаю квесту: Run as->Nios II modelsim 7) В поиске ищу сигнал clock и pio, но они отсутствуют Может быть я делаю что-то упускаю из виду?

-

А без avalon spi реализовать возможно? Я не представляю о каком avalon мастере идет речь(

-

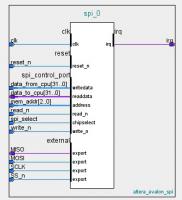

Посмотрел SPI core. Вижу такую куртинку: В мануале ug_embedded_ip.pdf ничего не сказано ни про data_from_cpu, ни про mem_addr, ни про data_to_cpu. Я могу додумать и предположить, что ядро позволяет использовать либо external либо spi_control_port (сигналы на прикрепленной мною картинке). Зачем нужны эти сигналы?

-

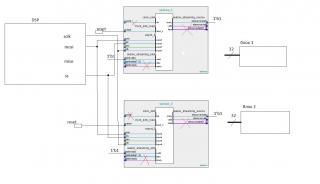

Всем привет. Делаю управление ПЛИС внешним процессором по интерфейсу spi. С процессора на плис идут два 32-х разрядных сигнала управления. Использую корку Avalon-ST Serial Peripheral Interface Core. Решил не заморачиваться с шиной Avalon и сделать все в квартусе, а не в qsys. До работы с интерфейсом сигналы, связанные с шиной Avalon(в cic и fir фильтрах), я задавал самостоятельно. Сейчас хочу поступить так же, поэтому из корки удаляю сигнал sysclk, stsinkdata, stsinkready, stsourseready, stsoursedata – то есть хоть что-то говорящее об Avalon. И вот здесь встал вопрос, а какой сигнал должен идти от spi slave до блока в ПЛИС? А как вы делаете управление по spi?

-

Спасибо!

-

Простите, а как скачать все файлы одновременно?Никогда с таким хранилищем не сталкивался.

-

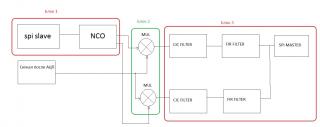

Подскажите пожалуйста, у меня такая система: Блок 1(первый красный прямоугольник) состоит из spi-slave и nco, блок 2 состоит из двух умножителей и третий блок из фильтров и spi-master. Правильно ли я понимаю, что следует выполнить следующие шаги : 1) Первый блок генерирую в qsys как отдельную систему. Генерирую HDL файл. 2) Второй блок я генерирую в квартусе с помощью визарда. В этом проекте находится top level. Соединяю первый и второй блок в quartus 3) Третий блок генерирую в qsys как отдельную систему. Генерирую HDL файл. Собираю все три блока в quartus. Направьте пожалуйста в нужном направлении

-

Из мануалов я понял, что qsys - это оболочка, в которой собирается вся система. Т.е если работаешь в qsys квартус уже не требуется.

-

Хочу попробовать всю систему засунуть в qsys, но почему то в qsys'e отсутствует умножитель, да и вообще простые арифметические операции. Кто работал в qsys подскажите как поступить.

-

-

Описание полностью идентично, как для ip ядра в Визарде, так и для ядра в qsys - они имеют только временные ограничения по работе.

-

Кто-нибудь соединял блоки DSP в Qsys? Требуется отдельная лицензия на ip ядра в qsys, чтобы их активировать?

-

Задача такая: На вход приемника (16 разрядный вход) приходит сигнал с АЦП . Управление планирую сделать по SPI. Съем данных (квадратуры) планирую сделать тоже по SPI. Не до конца понял назначение шины Avalon, требуется ли она для моего проекта, если управление идет по spi? Решил в качестве получения доп.опытав пересобрать систему в Qsys. Но есть одно НО: почему то для Cyclone V недоступно ядро NCO и CIC фильтр. Или требуется отдельная лицензия на эти ядра? Стоит Quartus 14.0 Web Edition

-

А чем отличается Qsys от SOPC Builder?

-

Для сборки системы я использовал Quartus. Делал step by step: последовательно соединял ip ядра и моделировал их. Получается что данную системы (цифровой приемник) правильнее сделать в Qsys или Sopc builder?

-

Шина Avalon

verali опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Собрал из IP ядер цифровой приемник (digital down converter). Провел моделирование в ModelSim. Все хорошо, но есть НО! В IP ядрах цифровых фильтров присутствуют входные и выходные сигналы для шины Avalon. Из литературы я понял, что Avalon - универсальная шина для построения системы на кристалле. Правильно ли я понимаю, что помимо прямого соединения компонентов цифровой обработки сигналов, их еще и надо связать этой шиной? CIC фильтр так же требует входной сигнал с этой шины (in_valid(), .out_ready(), .in_error(). При моделировании я самостоятельно задавал эти сигналы. Немного непонятно, зачем она нужна, направьте пожалуйста в правильную сторону. -

Выгрузка данных из ROM

verali ответил verali тема в Языки проектирования на ПЛИС (FPGA)

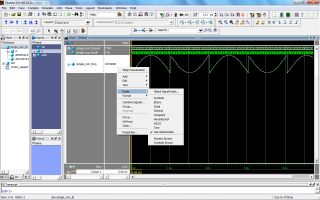

Ради интереса попробовал создать .mif файл и забить в него отрицательные числа, не забыв про A Memory Initialization File contains the initial values for each address in the memory. A separate file is required for each memory block. In a Memory Initialization File, you must specify the memory depth and width values. In addition, you can specify data radixes as binary (BIN), hexadecimal (HEX), octal (OCT), signed decimal (DEC), or unsigned decimal (UNS) to display and interpret addresses and data values. Data values must match the specified data radix Файл .mif следующего содержания: WIDTH=16; DEPTH=11; ADDRESS_RADIX=UNS; DATA_RADIX=DEC; CONTENT BEGIN 0 : 0; 1 : 5; 2 : 15; 3 : 80; 4 : 345; 5 : 656; 6 : -1; 7 : -2; 8 : -3; 9 : -4; 10 : -5; 11 : -6; В итоге, когда симулятор доходит до адреса, в котором отрицательное число, симулятор показывает 0, а не текущее отрицательное число: Получается в .mif не могут быть отрицательных чисел? Спасибо за совет! Я сейчас одновременно осваиваю как Quartus, QuestaSim и matlab. Объем очень большой, плюс к этому, т.к туториал на квесту на английском приходится переводить, сложно все одновременно делать без поддержки! Еще раз спасибо за помощь! -

Выгрузка данных из ROM

verali ответил verali тема в Языки проектирования на ПЛИС (FPGA)

Если я правильно понял в консоли QuestaSim набрать: radix signed Но ничего не изменилось. Или я неправильно делаю? -

Выгрузка данных из ROM

verali ответил verali тема в Языки проектирования на ПЛИС (FPGA)

-

Выгрузка данных из ROM

verali ответил verali тема в Языки проектирования на ПЛИС (FPGA)

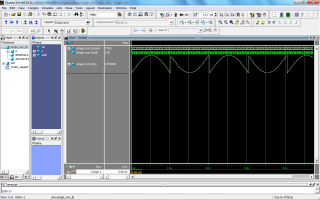

Не могу понять, почему QuestaSim не понимает знаковые числа, подскажите пожалуйста! Основной код: module single_rom ( addr, clk, q ); //Входные воздействия input [6:0] addr ; //длина адреса(в bin) input clk; output signed [15:0] q; //выходные данные //Внутренние регистры //внутренние соединения //Подключение ip-ядра rom rom_ip rom_ip_component ( .address (addr), .clock (clk), .q (q)); //Основной код //непрерывное присваивание endmodule Код testbench: `timescale 1 ps/ 1 ps module single_rom_tb(); // test vector input registers reg [6:0] addr; reg clk; // wires wire signed [15:0] q; // assign statements (if any) single_rom i1 ( // port map - connection between master ports and signals/registers .addr(addr), .clk(clk), .q(q) ); //clk initial begin clk = 0; forever #10 clk = ~clk; end //beginning address initial addr = 7'h00; //loop always begin @(posedge clk) if (addr >= 7'h64) addr = 7'h0; else addr = addr + 7'h1; end endmodule -

Здравствуйте! А в каком разделе стандарта SV четко написано, какие операторы являются синтезируемыми, а какие нет?

-

Выгрузка данных из ROM

verali ответил verali тема в Языки проектирования на ПЛИС (FPGA)

Сделал файл вида: -- Copyright © 1991-2013 Altera Corporation -- Your use of Altera Corporation's design tools, logic functions -- and other software and tools, and its AMPP partner logic -- functions, and any output files from any of the foregoing -- (including device programming or simulation files), and any -- associated documentation or information are expressly subject -- to the terms and conditions of the Altera Program License -- Subscription Agreement, Altera MegaCore Function License -- Agreement, or other applicable license agreement, including, -- without limitation, that your use is for the sole purpose of -- programming logic devices manufactured by Altera and sold by -- Altera or its authorized distributors. Please refer to the -- applicable agreement for further details. -- Quartus II generated Memory Initialization File (.mif) WIDTH=16; DEPTH=110; ADDRESS_RADIX=HEX; DATA_RADIX=BIN; CONTENT BEGIN 00 : 0000000000000000; 01 : 0000100000001001; 02 : 0001000000001010; 03 : 0001011111111011; 04 : 0001111111010100; 05 : 0010011110001101; 06 : 0010111100011101; 07 : 0011011001111111; 08 : 0011110110101001; 09 : 0100010010010100; 0A : 0100101100111011; 0B : 0101000110010101; 0C : 0101011110011101; 0D : 0101110101001101; 0E : 0110001010011110; 0F : 0110011110001100; 10 : 0110110000010001; 11 : 0111000000101001; 12 : 0111001111001111; 13 : 0111011100000001; 14 : 0111100110111010; 15 : 0111101111111000; 16 : 0111110110111001; 17 : 0111111011111011; 18 : 0111111110111101; 19 : 0111111111111110; 1A : 0111111110111101; 1B : 0111111011111011; 1C : 0111110110111001; 1D : 0111101111111000; 1E : 0111100110111010; 1F : 0111011100000001; 20 : 0111001111001111; 21 : 0111000000101001; 22 : 0110110000010001; 23 : 0110011110001100; 24 : 0110001010011110; 25 : 0101110101001101; 26 : 0101011110011101; 27 : 0101000110010101; 28 : 0100101100111011; 29 : 0100010010010100; 2A : 0011110110101001; 2B : 0011011001111111; 2C : 0010111100011101; 2D : 0010011110001101; 2E : 0001111111010100; 2F : 0001011111111011; 30 : 0001000000001010; 31 : 0000100000001001; 32 : 0000000000000000; 33 : 0111011111110110; 34 : 0110111111110101; 35 : 0110100000000100; 36 : 0110000000101011; 37 : 0101100001110010; 38 : 0101000011100010; 39 : 0100100110000000; 3A : 0100001001010110; 3B : 0011101101101011; 3C : 0011010011000100; 3D : 0010111001101010; 3E : 0010100001100010; 3F : 0010001010110010; 40 : 0001110101100001; 41 : 0001100001110011; 42 : 0001001111101110; 43 : 0000111111010110; 44 : 0000110000110000; 45 : 0000100011111110; 46 : 0000011001000101; 47 : 0000010000000111; 48 : 0000001001000110; 49 : 0000000100000100; 4A : 0000000001000010; 4B : 0000000000000010; 4C : 0000000001000010; 4D : 0000000100000100; 4E : 0000001001000110; 4F : 0000010000000111; 50 : 0000011001000101; 51 : 0000100011111110; 52 : 0000110000110000; 53 : 0000111111010110; 54 : 0001001111101110; 55 : 0001100001110011; 56 : 0001110101100001; 57 : 0010001010110010; 58 : 0010100001100010; 59 : 0010111001101010; 5A : 0011010011000100; 5B : 0011101101101011; 5C : 0100001001010110; 5D : 0100100110000000; 5E : 0101000011100010; 5F : 0101100001110010; 60 : 0110000000101011; 61 : 0110100000000100; 62 : 0001111111111111; 63 : 0111011111110110; 64 : 0111111111111111; 65 : 0000000000000000; 66 : 0000100000001001; 67 : 0001000000001010; 68 : 0001011111111011; 69 : 0001111111010100; 6A : 0010011110001101; 6B : 0010111100011101; 6C : 0011011001111111; 6D : 0011110110101001; END; Но при анализе выскакивает ошибка: Error (10170): Verilog HDL syntax error at xxx.mif(1) near text - Error (12153): Can't elaborate top-level user hierarchy Error: Quartus II 64-Bit Analysis & Synthesis was unsuccessful. 2 errors, 0 warnings Error: Peak virtual memory: 495 megabytes Error: Processing ended: Thu Nov 06 12:59:24 2014 Error: Elapsed time: 00:00:02 Error: Total CPU time (on all processors): 00:00:02 Сам код: // circle_rom module circle_rom ( addr, clk, q ); //Parameters parameter DATA_WIDTH_SIGNAL=16; //длина слова сигнала parameter ADDR_WIDTH=110; //длина адреса памяти //Input signals input [ADDR_WIDTH-1:0] addr; input clk; output reg [DATA_WIDTH_SIGNAL-1:0] q ; // Declare the ROM variable reg [DATA_WIDTH_SIGNAL-1:0] rom[110:0]; // регист будет содержать четыре 4-х разрядных чисел //описание внутренних регистров reg [ADDR_WIDTH-1:0] addr_reg ; //регист счетчика //считываем данные из файла и записываем весь массив в регист rom initial begin $readmemb("xxx.mif", rom); end //счетчик адреса always @ (posedge clk) begin addr_reg <= addr_reg + addr + 7'b01; //инкремент адреса q <= rom[addr_reg]; //выходное значение q end endmodule Может быть .mif считывается другой командой? -

Выгрузка данных из ROM

verali ответил verali тема в Языки проектирования на ПЛИС (FPGA)

Поясните пожалуйста этот момент. Как я понимаю DEPTH = 16; WIDTH = 8; ADDRESS_RADIX = HEX; DATA_RADIX = HEX; CONTENT BEGIN END это общий вид .mif файла А адреса придется забивать вручную, у меня ведь голый файл с двоичными числами. Я не понял как сгенерировать его(