verali

Свой-

Постов

80 -

Зарегистрирован

-

Посещение

Весь контент verali

-

А где в Квартусе прописать запрет на оптимизацию?

-

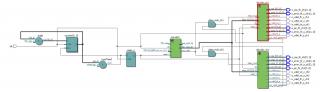

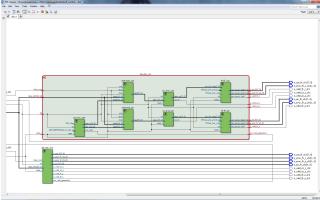

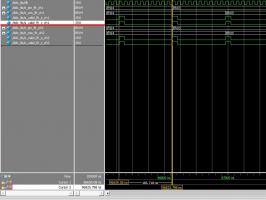

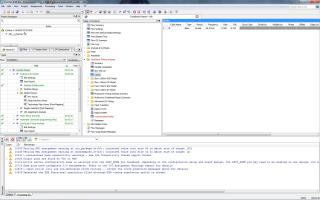

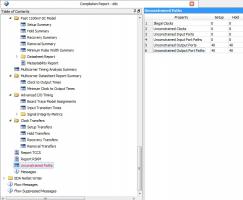

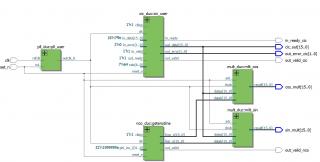

Всем добрый день! Имеем Cyclone V (обычный, без SOC) + Quartus 14.0 + QuestaSim. Собрал проект цифрового понижающего преобразователя (digital down converter) из альтеровских IP ядер (NCO, умножитель, FIR фильтр) и с opencores (CIC фильтр). Система двухканальная. В самом начале идет логика автоматического сброса (далее сброс будет приходить с процессора) Отдельно DDC, собранный из IP ядер. Данные с ПЛИС по последовательному порту идут в DSP. Под выходные данные с ПЛИС идет строб, который я вывожу на контрольные точки. В SDC файл прописываю свой клок, равный 60 МГц. В Warning присутствуют следующие предупреждения: 1)Unconstrained output ports 2)4 сигнала строба: Missing drive strength and slew rate Все остальные выходные информационные сигналы я вывожу на виртуальные пины, чтобы не мешались. В будущем они пойдут в DSP. При загрузке в ПЛИС стробы не идут - на контрольных точках висит высокий уровень. Буду признателен, если подскажете, как избавиться от варнингов.

-

Автоматический сброс на System Verilog

verali опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Добрый день! Являюсь новичком в Verilog и SV. До этого только подключал ip блоки к проекту, используя SV и писал простенькие testbench. Возникли трудности в банальном описании сброса. Внешний сброс приходит с процессора, доступ к которому сейчас не имею. Хочу проверить работоспособность "железа" путем автоматического сброса - допустим после 100 клоков сигнал reset переходит из 0 в 1 и далее никак не изменяется. Первая идея была использовать счетчик, который, досчитывая до 100, ставит сигнал reset в 1. Но, этот счетчик со временем обнулится, и сброс произойдет снова, что мне не подходит. Вопрос: возможно ли синтезировать данный сброс или надо искать другой путь? -

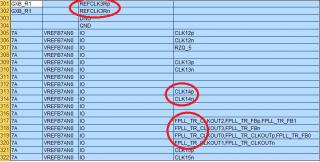

Сейчас описал sdc (ранее был не знаком с тем, что надо описывать клоки) - warning пропали. Посмотрите пожалуйста, все ли я описал в sdc. Листинг моего sdc: #************************************************************** # Time Information #************************************************************** set_time_format -unit ns -decimal_places 3 #************************************************************** # Create Clock #************************************************************** create_clock -name {altera_reserved_tck} -period 33.333 -waveform { 0.000 16.666 } [get_ports {altera_reserved_tck}] create_clock -name {clk} -period 10.000 -waveform { 0.000 5.000 } [get_ports {clk clk(n)}] #************************************************************** # Create Generated Clock #************************************************************** create_generated_clock -name {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} -source [get_pins {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|refclkin}] -duty_cycle 50.000 -multiply_by 6 -divide_by 2 -master_clock {clk} [get_pins {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]}] create_generated_clock -name {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk} -source [get_pins {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|vco0ph[0] }] -duty_cycle 50.000 -multiply_by 1 -divide_by 3 -master_clock {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~FRACTIONAL_PLL|vcoph[0]} [get_pins {pll_user|pll_duc_inst|altera_pll_i|general[0].gpll~PLL_OUTPUT_COUNTER|divclk}] #************************************************************** # Set Clock Latency #************************************************************** #************************************************************** # Set Clock Uncertainty #************************************************************** set_clock_uncertainty -rise_from [get_clocks {clk}] -rise_to [get_clocks {clk}] -setup 0.050 set_clock_uncertainty -rise_from [get_clocks {clk}] -rise_to [get_clocks {clk}] -hold 0.030 set_clock_uncertainty -rise_from [get_clocks {clk}] -fall_to [get_clocks {clk}] -setup 0.050 set_clock_uncertainty -rise_from [get_clocks {clk}] -fall_to [get_clocks {clk}] -hold 0.030 set_clock_uncertainty -fall_from [get_clocks {clk}] -rise_to [get_clocks {clk}] -setup 0.050 set_clock_uncertainty -fall_from [get_clocks {clk}] -rise_to [get_clocks {clk}] -hold 0.030 set_clock_uncertainty -fall_from [get_clocks {clk}] -fall_to [get_clocks {clk}] -setup 0.050 set_clock_uncertainty -fall_from [get_clocks {clk}] -fall_to [get_clocks {clk}] -hold 0.030 set_clock_uncertainty -rise_from [get_clocks {altera_reserved_tck}] -rise_to [get_clocks {altera_reserved_tck}] -setup 0.050 set_clock_uncertainty -rise_from [get_clocks {altera_reserved_tck}] -fall_to [get_clocks {altera_reserved_tck}] -setup 0.050 set_clock_uncertainty -fall_from [get_clocks {altera_reserved_tck}] -rise_to [get_clocks {altera_reserved_tck}] -setup 0.050 set_clock_uncertainty -fall_from [get_clocks {altera_reserved_tck}] -fall_to [get_clocks {altera_reserved_tck}] -setup 0.050 #************************************************************** # Set Input Delay #************************************************************** #************************************************************** # Set Output Delay #************************************************************** #************************************************************** # Set Clock Groups #************************************************************** set_clock_groups -asynchronous -group [get_clocks {altera_reserved_tck}] #************************************************************** # Set False Path #************************************************************** set_false_path -from [get_keepers {altera_reserved_tdi}] -to [get_keepers {pzdyqx*}] #************************************************************** # Set Multicycle Path #************************************************************** #************************************************************** # Set Maximum Delay #************************************************************** #************************************************************** # Set Minimum Delay #************************************************************** #************************************************************** # Set Input Transition #************************************************************** Спасибо за совет. Как я понимаю locked используется для синхронизации внешнего сброса с выходной частотой pll? В TimeQuest Timing Analyzer появились три частоты. 1)altera_reserved_tck 2)clk 3)pll_user Максимальные частоты 78, 195 и 262 соответственно.Правильно ли я понимаю, что в зависимости от того, чем я буду тактировать внутреннюю логику ПЛИС (без/с pll) меняется максимальная частота работы ПЛИС?

-

Клоки в Altera Arria V

verali опубликовал тема в Работаем с ПЛИС, области применения, выбор

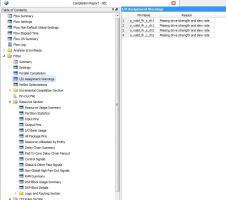

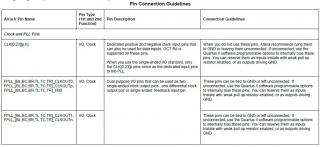

Добрый день! Собрал проект на ПЛИС из IP-блоков: После компиляции TimeQuest показывает, что максимальная скорость около 90 МГц, что для Arria V является очень низкой. В информационных сообщениях появляются Warnings: 1) 1 input pin(s) will use non-dedicated clock routing. Как я понял, мой клок использует путь(пин) не предназначенный для клока. В Connection Guidelines есть два типа клока - clk и pll. Логично предположить, что только ко второму можно подключить pll. Но в pin assignment pll является дополнительной опцией: Следовательно делаю вывод, что в любому clk я могу подключить pll. Верны ли мои предположения? 2) Node: clk was determinated to be a clock but was found without an associated clock assignment. Warning требует от меня где-то (может быть в assignment editor?) указать что этот пин используется как клок(так как клок может быть и клоком и обычным I/O)? Не могу найти, где это указать. Буду благодарен за наводку. 3) PLL cross checking found inconsistent PLL clock settings: was found missing 1 generated clock that corresponds to be a base clock with a period of: 10.000 Тут warning мне говорит, что я не подключил(потерял) клок, который идет на вход ФАПЧ, хотя из первого вложения видно, что внешний клок идет напрямую на ФАПЧ. Сразу скажу - внешний клок 100 МГц идет на ФАПЧ и выходят все те же 100 МГц. В институте так советовал делать преподаватель, ссылаясь на то, что увеличивается надежность всей системы, из-за того, что внешний клок может быть зашумленным, а выход ФАПЧ является чуть ли не прецизионным. 4)В TimeQuest есть так называемый altera_reserved_clock. Что это такое и почему его частота 33 МГц? Связан ли он какие-либо образом с SignalTap? -

Принцип работы CIC фильтра

verali ответил verali тема в Алгоритмы ЦОС (DSP)

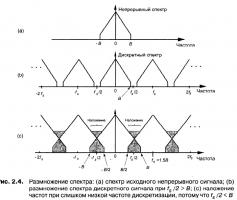

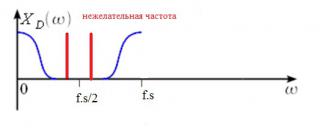

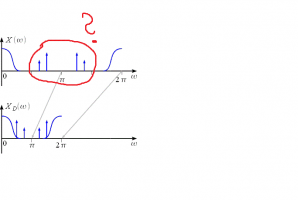

Под алиасингом я всегда понимал искажения, вызванные несоблюдением требования по Котельникову: Получается, что под алиасингом понимается любое нежелательная энергия сигнала на частотах до f.s/2? Почему полезный сигнал считается до Fs/2, а не ограничен интересующей нас полосой? Почему нас интересуют спектральные составляющие, лежащие вне полосы сигнала? -

Принцип работы CIC фильтра

verali ответил verali тема в Алгоритмы ЦОС (DSP)

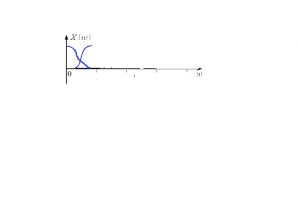

На dsplib мне не понятен рисунок 2а. 1)Что это за спектральные линии? Как я понимаю синей сплошной показан спектр до дискретизации. 2)В институте учили, что требование по Котельникову заключаются в том, чтобы частота дискретизации была минимум в два раза выше верхней боковой частоты. Соотвественно наложение частот (алиасинг) должно выглядеть следующим образом: -

Принцип работы CIC фильтра

verali ответил verali тема в Алгоритмы ЦОС (DSP)

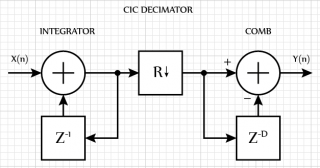

Мне не понятна физика работы. Да, там (и не только там) приведены формулы, АЧХ и ФЧХ, но физически я не могу понять, почему сначала сигнал надо накапливать, потом его вычитать. Почему эти блоки позволяют привести сигнал к требованию по Котельникову (а не просто выкинуть ненужные нам отсчеты без использования гребенки и интерполятора). Физическое понимание мне нужно для самостоятельного описания cic на hdl. -

Принцип работы CIC фильтра

verali опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день! Никак не могу понять принцип работы cic фильтра (дециматора и интерполятора), перелапатил кучу литературы (Р. Лайонс, А Сергеенко и т.д) и сайтов (dsplib, altera). Для начала возьмем фильтр-дециматор, который состоит из блока интегратора, блока прореживания и блока гребенчатого фильтра. Вопросы: 1) Для чего нужен каждый из блоков? Зачем требуется сначала накапливать, потом вычитать? Хочу понять именно физический смысл этих блоков. 2) Почему эти блоки (интегратор и гребенки) позволяют нам привести сигнал к требованию по Котельникову после децимации? Не могу понять физический принцип этого. -

Огромное спасибо!

-

Работаю в Quartus 14.1. Столкнулся с этой же проблемой - в папке проекта скрипт генерации коэффициентов компенсационного фильтра отсутствует. В описании сказано, что Матлабовский скрипт будет лежать в папке с проектом: Вы его нашли?

-

Реализация Cordic алгоритма на ПЛИС

verali ответил verali тема в Алгоритмы ЦОС (DSP)

Скорее всего так и есть. Автору статьи отписал. В случае ответа - отпишу. -

Реализация Cordic алгоритма на ПЛИС

verali опубликовал тема в Алгоритмы ЦОС (DSP)

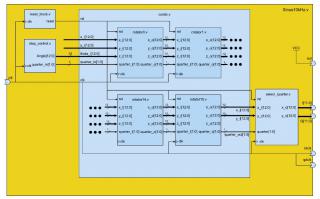

Добрый день! Решил повторить реализацию Cordic алгоритма из kit-e.ru/assets/files/pdf/2011_12_36.pdf на ПЛИС. Проект состоит из 5 модулей (структурная схема во вложении): 1) reset_block.v - аппаратный сброс и установка всех регистров в начальное положение. 2) step_control.v - модуль. формирующий шаг фазы для вычисления синуса и косинуса, а так же четверть в которой находится выходной сигнал 3) Cordic.v - модуль, формирующий конвейер из блоков, вычисляющих выходные значения синуса и косинуса. 4) rotator[0-15].v - модуль, поворачивающий вектор на заданный угол. 5) select_quarter.v - модуль, подводящий вычисленное значение синуса и косинуса под весь диапазон АЦП. В модуле step_control.v значение фазы Angle задает значение выходной частоты. В статье сказано, что значение Angle в 3216 соответствует фазе в 90 градусов, т.е увеличивая каждый такт значение Angle на 1, на выходе мы получим частоту равную f.out=F.clk/3216/4 (на 4 делится, чтобы получить полный период, а не только до 90 градусов). Откуда взято, что значение Angle в 3216 соответствует фазе в 90 градусов? -

Реализация Cordic алгоритма на ПЛИС

verali опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день! Решил повторить реализацию Cordic алгоритма из kit-e.ru/assets/files/pdf/2011_12_36.pdf на ПЛИС. Проект состоит из 5 модулей (структурная схема во вложении): 1) reset_block.v - аппаратный сброс и установка всех регистров в начальное положение. 2) step_control.v - модуль. формирующий шаг фазы для вычисления синуса и косинуса, а так же четверть в которой находится выходной сигнал 3) Cordic.v - модуль, формирующий конвейер из блоков, вычисляющих выходные значения синуса и косинуса. 4) rotator[0-15].v - модуль, поворачивающий вектор на заданный угол. 5) select_quarter.v - модуль, подводящий вычисленное значение синуса и косинуса под весь диапазон АЦП. В модуле step_control.v значение фазы Angle задает значение выходной частоты. В статье сказано, что значение Angle в 3216 соответствует фазе в 90 градусов, т.е увеличивая каждый такт значение Angle на 1, на выходе мы получим частоту равную f.out=F.clk/3216/4 (на 4 делится, чтобы получить полный период, а не только до 90 градусов). Откуда взято, что значение Angle в 3216 соответствует фазе в 90 градусов? -

Добрый день! Ситуация такая - пришли платы по старой теме. Разработчик, который всю плату рисовал и разбирался с blackfin (раньше проекты были на adsp21xx), давно уволился. Передо мною стоят задачи: 1)Написать тестовую программу, которая позволит проверить, есть ли в системе технические проблемы (разрывы цепи, недопайки и т.д). 2)Написать загрузчик. На плате два процессора и одна флешка. Необходимо написать программу для прошивки флешки через процессор (в ee-240 нашел программирования флешки Atmel через BF ). За пару недель до этого начал работать с отладочной платой ADSP-BF533. Пока успел только познакомиться с архитектурой и с ассамблером. Поморгал диодиками, задействовал таймер и прерывания. Сейчас уже приходится перемещаться на реальную железку (без отладчика). 1)При написании программы на отладочной плате пользовался готовым проектом и вносил туда изменения. В готовом проекте (в примерах) есть файл startup.h. Этот файл пользователь сам прописывает или же есть какой-нибудь генератор этого файла?

-

Все верно, два источника частоты для таймера.Я выбрал SCLK. Значит я ошибочно считал, что при каждом "шаге"(F11) в дебагере (использую ADSP bf533 EZ KIT LITE), значение в TIMERx_COUNTER должно увеличиваться на 1. Исходя из схемы работы таймера, счетчик таймера идет на инкремент и сравнивает свое значение с регистром TIMERx_COUNTER, пока значение в регистре счетчика не станет равным с TIMERx_COUNTER. Да, первым делом в обработчике прерывания сбрасываю статусный бит. Спасибо за объяснение. Сейчас попробую на железе помигать светодиодом, чтобы визуально оценить правильность работы таймера.

-

Таймер в blackfin 533

verali опубликовал тема в Сигнальные процессоры и их программирование - DSP

Добрый вечер! Разбираюсь с таймером в BF533. Делаю программу мигания светодиодом по прерыванию таймера 0. По теории после включения таймера в режиме ШИМ (PWMOUT) в регист TIMERx_COUNTER должен записаться 0 и счетчиком инкрементироваться до значения в регистре TIMERX_PERIOD. В моем же случае в регистр TIMERx_COUNTER после включения таймера записывается рандомное число и с каждым новым тактом значение в данном регистре увеличивается на рандомное число (причем с каждым разом это число разное), соответсвенно и прерывание срабатывает почти сразу после начала выполнения программы(программа входит в обработчик прерываний, устанавливается нулевой бит в регистре TIMER_STATUS). В регистре TIMER_CONFIG устанавливаю биты: 1)PWM_OUT - включение режима ШИМ 2)OUT_DIS - запрещение сигнала на выходе TMRx 3)PERIOD_CNT - генерируется ШИМ сигнал 4)IRQ_EN - разрешение прерывания 5)EMU_RUN - при эмуляции таймер работает Может быть кто-нибудь сталкивался с данной проблемой? -

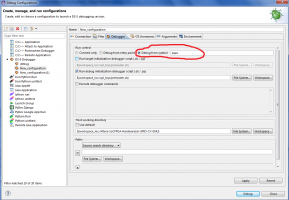

А как вы загрузили приложение поверх прилодера для отладки? Делали ли что-нибудь, помимо установки галочки в дебаггере напротив "debug from symbol"?

-

Решил пересобрать проект с нуля для Arrow SoCKit. Первое - скомпилировал GHRD, получив: - .svd - для отладчика DS-5 - .Handoff folder - описание аппаратной части для preloader generator - .sof - сама прошивка ПЛИС Второе - собираю прелоадер с помощью preloader generator и получаю: - u-boot-spl.bin - прелоадовский bin файл - preloader-mkpimage.bin - образ прелоадера Вопросы: 1) как preloader записать записать на SD карту: какие файлы и какие разделы создавать на карте? 2) После загрузки preloadera на SD планирую сделать отладку в debugger, опять же какие файлы добавлять в проект в eclipse для отладки?

-

Спасибо, сейчас попробую Не в этом дело

-

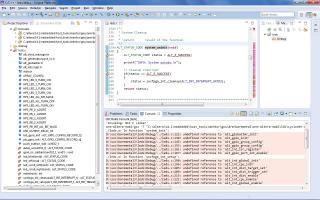

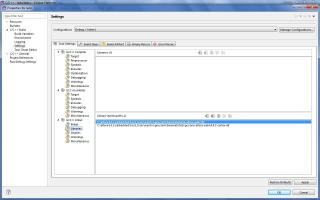

GPIO baremetal пример

verali опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Пробую собрать проект GPIO, представленный в разделе example baremetal на сайте altera. Линковщик не может найти требуемые файлы, хотя принудительно указал путь к библиотекам. В чем может быть проблема? В первом вложении сама ошибка во втором путь в библиотекам. -

Цифровая обработка происходит в fpga, в SoC находится еще и процессор! Думаю отличный повод начать изучать что-то новое.

-

Спасибо за разъяснение, где то вычитал, что bootrom находится во флеш-памяти процессора, поэтому и ввел самого себя в заблуждение. Сразу наткнулся на эту статью, но так как процесс заливки отличался от того, что представлено на rocketbard, решил повременить с разбором этой статьи. У меня точка-точка. tcp/ip - потому что на форуме посоветовали. Был вариант разбираться с bare-metal, но информации оказалось очень мало. Вариант с линуксом я выбрал, так как опыта написания дров у меня нет, вещи то может быть это и простые, но представления у меня о них очень слабые.

-

В первом сообщении я дал ссылку на мануал, в котором описывался процесс загрузки линукса без preloader и bootloader. Сделал все по этому мануалу и получилось через терминал (putty) поморгать диодиками на плате. Поэтому у меня возник вопрос - а почему так получилось? Так как я не собирал ни прилодер, ни бутлодер! Данные - это 32 разрядное слово идет с частотой 500 кГц. Как мне посоветовали надо делать tcp/ip

-

Сейчас я рассматриваю SoC именно как два разных устройства. Сообщения выше относятся к ARM Cortex-A9, так как именно на него я буду ставить linux. Как раз таки я хочу разгрести эту кучу и расставить все по полочкам.