egorman44

-

Постов

144 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные egorman44

-

-

Опубликовано · Изменено пользователем egorman44 · Пожаловаться

По мере чтения возникают вопросы.

Во-первых правильно ли я понял, для синхронизации сигнала мне необходим синхронизатор

(например два последовательных D- триггер). Он выглядит следующим образом:

(например два последовательных D- триггер). Он выглядит следующим образом: always @(posedge SCLK) begin a1 <= SDOFS; a2 <= a1; a3 <= a2; SDOFS_risingedge <= ((~a3)&a2); end

В таком случае , задержка при определение переднего фронта SDOFS составит 2 такта синхросигнала. Как мне говорит даташит

"SDOFS Framing Signal Output for SDO Serial Transfers. The frame sync is one bit wide and is active one SCLK period

before the first bit (MSB) of each output word. SDOFS is referenced to the positive edge of SCLK. SDOFS is in

three-state when SE is low." ,

После импульса SDOFS , длинной один такт SCLK, сразу следует первый бит посылки. Т.е. должен ли я исправить код на

always @(posedge SCLK) begin a1 <= SDOFS; a2 <= a1; SDOFS_risingedge <= ((~a2)&a1); end

чтобы не пропустить первый бит ? Или есть другие решения ?

-

Опубликовано · Изменено пользователем egorman44 · Пожаловаться

премного благодарствую !

вот здесь капиталисты тоже рассматривают почему inferred latch есть плохо :rolleyes:

http://electronics.stackexchange.com/quest...red-latches-bad

-

Господа спасибо за пищу для размышлений ! будем читать значит

и вопрос конечно офтоп , но хотелось бы очень узнать , как ближе перевести понятие "inferred latches" , что защелка это понятно, но какой смысл вкладывают в слово inferred ?

-

Добрый день всем! Начал потихоньку осваивать Verilog . Сейчас хотелось сделать проектик для работу с микросхемой AD73322 (front-end processor для речи и телефонии).

Протокол обмена между fpga и AD73322 следующий:

1. Ждать импульса на линии SDOFS , говорит о том что сейчас будет прием, AD73322 будет передавать пакет fpga

2. Затем принять 16 бит

3. Сделать чего- нибудь с ними(принятыми битами)

4. Сформировать импульс на линии SDIFS , говорит о том что сейчас будет передача ,AD73322 будет принимать пакет от fpga

5. Передать 16 бит

как я вижу задачу можно решить с применением FSM(Finite State Machine) дизайна . Просмотрев мануал "Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements", я остановился на методе с применением 3-х always блоков.

вопросы следующие:

1. Правильно ли решать подобную задачу с помощью Finite State Machine Design? Есть ли альтернативы?

2. Допусти у меня есть состояния wait_for_SDOF и ready_to_receive, переход из первого во второй осуществляется , по импульсу на линии SDOFS , как это должно выглядеть ? Мой вариант :

always @(state,SDOFS) begin next = 'bx; case (state) wait_for_SDOFS: if (SDOFS) next = ready_to_receive; else next = wait_for_SDOFS ; ... endcase end

не надо ли использовать конструкцию

posedge SDOFS

, так как мне нужен именно переход из "0" в "1", но как использовать его в блоке always, если я его запихну туда, ничего хорошего думаю не получиться.

Вообщем как поступают при ожидании синхронизирующего сигнала , как и в моей ситуации ?

-

Пока Proton не пришел :), посмотрите вот это, вдруг подойдет? Это под TI_CCS_3.1

Мерси мадам)

-

Уважаемый Proton не могли бы выложить rf_v2 еще раз, а то в той местности уже пусто :crying:

Буду Вам очень признателен.

-

Большое спасибо товарищи! Все вроде бы работает)

-

Скачайте AVR-Studio и пошагайте по своей программе в эмуляторе.

Думаю, что это будет для вас полезно.

ага спасибо) а вы как думаете откуда я состояние флага узнал в голове что ль просимулировал?

-

Здравствуйте дорогие форумчане. Разбираюсь с мк Atmel. Хотел выработать прерывание при достижении счетчиком какого либо числа. В регисры OCR1B(H/L) записал число до которого надобно считать, но не досчитав до заданного числа, флаги регистра TIFR1 : OCF1A, OCF1B, OCF1C получают значения логической единицы. После того как я инициализировал маску и разрешил прерывание программа уходит на вектор прерываний. необходимо ли сбрасывать флаги прерываний от МК или косяк в инициализации таймера/счетчика.

.include "m640def.inc" ; .list ; .def temp=R17 ; .def rab=R18 ; .equ kdel=30 ; ;------- reservation of call .dseg ; .org 0x200 ; buf: .byte 1 ; ;------- begining of program code .cseg ; .org 0 ; ;------- redefining of interrupt vector start: jmp init; Reset Handler nop ; reti ; IRQ0 Handler nop ; reti ; IRQ1 Handler nop ; reti ; IRQ2 Handler nop ; reti ; IRQ3 Handler nop ; reti ; IRQ4 Handler nop ; reti ; IRQ5 Handler nop ; reti ; IRQ6 Handler nop ; reti ; IRQ7 Handler nop ; reti ; PCINT0 Handler nop ; reti ; PCINT1 Handler nop ; reti ; PCINT2 Handler nop ; reti ; Watchdog Timeout Handler nop ; reti ; Timer2 CompareA Handler nop ; reti ; Timer2 CompareB Handler nop ; reti ; Timer2 Overflow Handler nop ; reti ; Timer1 Capture Handler nop ; reti ; Timer1 CompareA Handler nop ; jmp prtim ; Timer1 CompareB Handler nop ; reti ; Timer1 CompareC Handler nop ; reti ; Timer1 Overflow Handler nop ; reti ; Timer0 CompareA Handler nop ; reti ; Timer0 CompareB Handler nop ; reti ; Timer0 Overflow Handler nop ; reti ; SPI Transfer Complete Handler nop ; reti ; USART0 RX Complete Handler nop ; reti ; USART0,UDR Empty Handler nop ; reti ; USART0 TX Complete Handler nop ; reti ; Analog Comparator Handler nop ; reti ; ADC Conversion Complete Handl nop ; reti ; EEPROM Ready Handler nop ; reti ; Timer3 Capture Handler nop ; reti ; Timer3 CompareA Handler nop ; reti ; Timer3 CompareB Handler nop ; reti ; Timer3 CompareC Handler nop ; reti ; Timer3 Overflow Handler nop ; reti ; USART1 RX Complete Handler nop ; reti ; USART1,UDR Empty Handler nop ; reti ; USART1 TX Complete Handler nop ; reti ; 2-wire Serial Handler nop ; reti ; SPM Ready Handler nop ; reti ; Timer4 Capture Handler nop ; reti ; Timer4 CompareA Handler nop ; reti ; Timer4 CompareB Handler nop ; reti ; Timer4 CompareC Handler nop ; reti ; Timer4 Overflow Handler nop ; reti ; Timer5 Capture Handler nop ; reti ; Timer5 CompareA Handler nop ; reti ; Timer5 CompareB Handler nop ; reti ; Timer5 CompareC Handler nop ; reti ; Timer5 Overflow Handler nop ; reti ; USART2 RX Complete Handler nop ; reti ; USART2,UDR Empty Handler nop ; reti ; USART2 TX Complete Handler nop ; reti ; USART3 RX Complete Handler nop ; reti ; USART3,UDR Empty Handler nop ; reti ; USART3 TX Complete Handler nop ; int_ret: reti ;------ initialization module init: ldi r16, high(RAMEND) ; out SPH,r16 ; Set Stack Pointer to top of RAM ldi r16, low(RAMEND) ; out SPL,r16 ; ;------ I/O ports initialization ldi temp,0xFF ; sts DDRL,temp ; ;------ Timer 1 initialization ldi temp,0x01 ; sts TCCR1B,temp ; ldi temp,high(kdel); sts OCR1BH,temp ; ldi temp,low(kdel); sts OCR1BL,temp ; ;------ define interrupt mask ldi temp,0x04 ; sts TIMSK1,temp ; ;------ comparator initialization ldi temp,0x80 ; out ACSR,temp ; sei ; ;------ begining of main function main: ldi rab,0x80 ; ldi temp,0xFF ; sts buf,rab ; eor temp,rab ; sts PORTL,temp ; m1: rjmp m1 ; ;------ interrupt subprogram prtim: push temp ; push rab ; lds rab,buf ; ;------ left shift p1: lsr rab ; brcc p3 ; ldi rab,0x80 ; p3: ldi temp,0xFF ; eor temp,rab ; sts PORTL,temp ; sts buf,rab ; pop rab ; pop temp ; reti ;

-

нарисуйте conductive shape вместо трассы

так и пришлось поступить. спасибо ребят

-

Опубликовано · Изменено пользователем egorman44 · Пожаловаться

вообще не подводят трассу ширина которой больше площадки, д.б. термобарьер1.в CES пропишите ширину трасс 2мм 1мм 0,5мм и при подводе к площадке по ПКМ выберите 1 или 0,5мм

2.если таких компанентов много и делать лень то сделать RuleArea для данного компанента

дак там и при ширине 2 мм , уже чем площадки получается

---

т.е. как я понял нет такой возможности провести 2 мм трассу от пункта А к Б не сужая ее у контактной площадки?

-

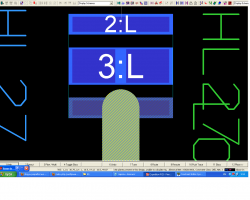

Опубликовано · Изменено пользователем egorman44 · Пожаловаться

Добрый день товарищи. Подскажите как убрать ограничение ширины трасс. Мне надобно провести дорожку шириной 2 мм. в ces я убрал ограничение между трассой и падом, но теперь из-за скругления трассы , она наезжает на соседнюю контактную площадку, при попытке увеличение ширины трассы. expedition ругается: "At least one width could not be performed: it causes a DRC violation'

-

Ключевое слов keyin ;)

нельзя ли поподробнее ?

чего с этим keyin делать?

-

Здравствуйте люди. подскажите пожалуйста есть ли возможность в expedition разместить компоненты группой на плату, допустим прямоугольной сеткой с одинаковыми расстояниями между компенонтами.?

-

а чем родной LP Wizard не угодил ?

есть некие компоненты которые он просто не может рисовать, думаю может производители других продуктов позаботились, разнообразя стандартные наборы smd и pth

-

и снова здравствуйте :)

Товарищи подскажите есть ли аналоги у менторовского LP Wizzard ? с помощью которых можно творить land patterns и экспортировать , допустим в тот же самый mentor?

-

Добрый день господа, а день добрый- выходной!

Подскажите пожалуйста , у меня допустим имеется микросхема с двумя одинаковыми выводами , к примеру gnd. Могу ли я в symbol editor нарисовать один пин gnd, а затем в pаrt editor присвоить два контакта этому выводу gnd? и что такое number of slots in component - при выгрузе символа из symbol editor?

заранее спасибо

-

точно точно) в воодушевляющем порыве , перепутал все !

-

Опубликовано · Изменено пользователем egorman44 · Пожаловаться

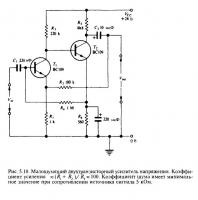

Ребяты , господа , товарищи!!!! это гениально!!!) теперь все встает на свои места) ведь ясно же ш что с коллектора T2, Т1 берет напряжение смещения!!! УРА, УРА ,УРА!!! снимаю шляпу перед всеми!!! СПАСИБО !!!

-

Добрый день господа! любители и профессионалы в области электроники !

Изучаю учебник М.Х. Джонса Электроника практический курс. Столкнулся со схемой описанной в параграфе 5.9.6. Малошумящий двухтранзисторный усилитель напряжения. Возник вопрос как работает сея штуковина.

Не пойму как задается коллекторный ток Т1=100 мкА, не вижу как задается смещение транзистора T1. Интересно будет ли работать данная схема?! Не пойму принцип работы обратной связи по постоянному току (за счет резистора R4),стабилизирущей режим покоя. Пожалуйста помогите чем сможете?)

-

c DC не знаком, но в DxD при получение чужого проекта всегда делаю FA-BA

и только затем лезу в корректировку проекта

вначале попробуйте пройти это

пробовал

-

Господа помогите разобраться.

Досталось мне переделать проект, заменил компоненты в DC скомпелировал CDB, сделал Package Design, в Exp провел прямую аннотацию, стал трассировать, вкл cross probe , и получил что ref des компонента в expedition не совпадает с ref des в DC. что делать?

----

да и Routed_pins до сих пор не активна

-

да если бы я сам покупал эти вилки

всем спасибо!

-

Какая хорошая подробность :) А поставить p-канальный транзистор вместо n-канального Вы можете?

боюсь что нет))

ибо очень много в наличии у меня n канальных...

Прием и последовательная передача данных .

в Языки проектирования на ПЛИС (FPGA)

Опубликовано · Пожаловаться

По мере погружения , появляются еще некоторый вопросы , требующие разъяснения

Хотел спросить о генерации сигнала сброса . Порыскал на просторах и нашел в книге Полякова (это в главе посвященной верификации) следующее:

Почему товарищ использует в одном initial блоке blocking и non-blocking assignment или для верификации так можно ? Я переправил ,

Вроде бы работает, но посмотрев RTL Viewer не увидел никакой синтезируемой схемы, привязанной к выходу RESET_INV, а лишь высокий уровень 1'h1 . Хотелось , бы услышать как ПРАВИЛЬНО исполнять сие?