egorman44

-

Постов

144 -

Зарегистрирован

-

Посещение

Сообщения, опубликованные egorman44

-

-

Ребяты всем спасибо , завтра буду пробовать выдерживать паузу :a14:

-

Всем здравствуйте ! :) У меня вопрос.

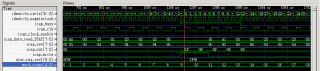

Есть у меня волшебный MAC контроллер от Xilinx (Ip "Tri - Mode Ethernet Mac cntr") использую в режиме 100 Mbps работает исключительно на передачу. Каждые 4 мс моей логикой формируются 8 пакетов примерно по 1024 байт, для этого используется 8 буферов по 2048 байт каждый. Размер буфера выбрал исходя из количества оставшихся блоков RAM. Данные поступают от фреймера E1.

Мне это все дело необходимо передать PHY трансмиттеру. Есть ли какой-либо минимальный интервал между посылкой пакетов по MII, или я вполне могу слать следующий как только закончена пересылка предыдущего ? На сколько я понял PHY мне не может доложить, что пакет ушел в сеть ? А может все это дело разнести по времени, по мере заполнения буферов, чтобы сразу во внешку все не передавалось ?

UPD: я так понял достаточно соблюсти Interpacket gap ?

-

а вот так вот:

counter<= (counter + 1) % 13;

-

нет, там выполняются операции, вот это результат я хотел бы получать в reg блока на Verilog.

Ну так соедините все это дело. Модуль VHDL и Verilog модуль, в топовом схематике.

UPD: Хотя как пишут, можно использовать оба модуля в проекте если Ваш синтезатор поддерживает оба языка, и в качестве топового модуля использовать HDL. Если выбрали в качестве топового модуля Verilog, то VHDL модуль объявите как если бы он был написан на Verilog'e.

-

reg [3:0] iT1 = iTime1[3:0];

reg [3:0] iT2 = iTime2[3:0];

На сколько я помню значение типу данных reg присваиваются в блоках always, а вышеописанным образом вы их инициализируете.

reg [3:0] iT1; reg [3:0] iT2; always @(*) begin iT1 = iTime1; iT2 = iTime2; end

Это если вы хотите , чтобы значение в регистрах изменялось асинхронно.

Ну и думается Вам надо как, то соединить эти два модуля, каким нибудь схемотехническим топовым модулем. Модуль на VHDL у Вас состоит их объявления портов, только ?

-

STATUS регистр доступен через Impact.

Пример на сайте Xilinx: XTP104 - KC705 MultiBoot Design

Мне конечно надо чтобы в полевых условиях это работало, где-то далеко от импакта :) но можно сравнить с тем непонятным значением что я получаю, каждый раз как пытаюсь читать STAT reg.

Нечто подобное делалось для пятого Virtex. После включения питания грузилась резервная прошивка, она запускала загрузку боевой. Если происходил сбой по CRC или таймауту Watchdog, то грузилась обратно резервная. Чтобы система не зашла в бесконечный цикл, в резервной прошивке читался Boot History Status Register (BOOTSTS) через ICAP. В приложенном файле модуль, отвечающий за логику перезагрузки ПЛИСа. Может чем поможет :)Посмотрим !

Всем Спасибо!

-

изначально цифровой сигнал DATA однонаправленный? какая тактовая частота CLK для DATA?

Да однонаправленный, двунаправленный я уже как то пробрасывал

JTAG вообще не быстрый у меня - 6 МГц.

Если тактовая в плис раза в 4 и более выше поступления данных (Ваш случай), тогда я брал и "переносил входной сигнал" на свою тактовую частоту плис, т.е. детектировал передний и задний фронт сигнала данных и формировал импульс данных. Уже сформированный на частоте плис сигнал данных - выдавал наружу.Вот я и подумал, что может есть какое-то правило. Думается чем быстрее сигнал, тем быстрее разбегаются фронты, соответственно ПЛИСиной можно их маленько выровнять. Но с другой стороны если сигнал слишком уж шустрый, то с какой его частотой надо молотить, чтобы впихнуть в синхронизатор.

-

логика уровня 3,3В

LVCМOS - КМОП

LVTTL - ТТЛ

логика

Объяснять что такое КМОП и ТТЛ логика? короткий ответ здесь

тип логики прописывается в ucf/sdc файле для каждого пина ПЛИС

нет, спасибо, это я где-то слышал уже ;)

меня интересует вопрос чисто описательный , как описывать правильнее, когда пробрасываешь какой-то инерфейс через ПЛИС

// вот имеем допустим module( input DATA_in, input CLK_in, output DATA_out, output CLK_in ); assign DATA_out = DATA_in; // пробрасываем все проводом assign CLK_out = CLK_in; // и это тоже endmodule

// или это дело пропустить через синхронизатор и выдать на выход ? module( input DATA_in, input CLK_in, output DATA_out, output CLK_in ); wire sys_clk; // допустим клок с ПЛЛ reg [1:0] CLK_pipe, DATA_pipe; always@(posedge sys_clk) begin CLK_pipe <= {CLK_pipe[0],CLK_in}; DATA_pipe <= {DATA_pipe[0], DATA_in}; end assign DATA_out = DATA_pipep[1]; assign CLK_out = CLK_pipe[1]; endmoduleИли второй случай ересь ? Вот Вы как делаете ?

-

По плате и через кабель "100 МГц" на LVCMOS или LVTTL?

Это я же ш для примера про 100 МГц

Какие различия при пробросе линии для LVCOS и LVTTL , поведайте ? Надо их к соответствующим банкам подключить ?

-

Здравствуйте :)

Буквально вчера делал проброс JTAG'a, и задумался как сделать сие правильно.

1. Бросить линию проводом, но тогда фазы сигналов возможно разбегутся .

2. Пропустить через синхронизатор и выдать наружу, сигнал малость сдвинется, но фронты из ПЛИС уйдут в одно и тоже время.

JTAG, которой я использовал, достаточно медленный 6МГц, я попробовал и так и сяк, оба раза успешно. Хотелось бы узнать как правильно и есть ли какой критерий для определения границы. Например если надо пробросить сигнал в 100 МГц, как быть ?

-

У меня возникли подозрения, что я как то неправильно читаю либо интерпретирую прочитанное из регистра STAT. В регистре STAT должен содержаться режим конфигурации 3 бита, у меня выставлен Internal Master SPI что в бинарном виде выглядит как 3'b011 , но к сожалению в полученных от ICAP (16'hCF9F) данных, я не увидел нигде, ничего похожего на 3'b011. Принятые данные 16'hCF9F надо побайтно перевернуть получиться значение -> 16'F1F9, режим конфигурации располагается в 11:9 битах , но там нули. :(

Кто-то может пробовал читать этот регистр через ICAP / SelectMAP ?

-

Здравствуйте многоуважаемые форумчане! Есть проект который использует MultiBoot. Хотелось бы узнать есть ли способ как-либо детектировать событие, когда ПЛИС хотела загрузиться с конфигурации 1 на конфигурацию 2 , но по каким-либо причинам это не получилось и вернулась на конфигурацию 1. Нашел такой регистр как STATUS. Вроде бы в нем присутствуют соответствующие флаги "Configuration Watchdog Timer expired" и "Post-configuration CRC check error", но к моему удивлению они уже установлены в лог.1 когда я их читаю после подачи питания, когда запускается конфигурация 1 , т.е. говорят о наличии ошибки. Подскажите может кто делал, в чем тут фокус ?

-

И ещё: при симуляции Simulate Behavioral Model не отображается сигнал с выхода V. Я так понимаю его просто нету поэтому он не отображается?

а входные то воздействия у вас имеются ? тестбенч писали ?

UPD: хотя,и без написания тестбенча Вы просто можете в симуляторе Isim, принудительно присвоить значение на выводе (Force constant...),благо у Вас их не очень много, затем нажать на кнопку Run for the time specified on the toolboar, затем опять принудительно присвоить значения на ваших входах, и опять запустить симуляцию,и так по кругу пока не переберете все интересующие Вас значения.

-

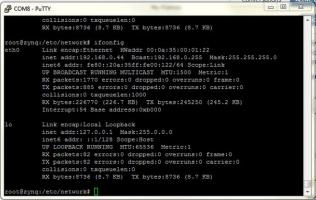

А на компе ICMP сервер доступен? Там в виндах иногда фаервол пинги не пропускает. Лучше всего посмотреть wireshark'ом.

Только вернулся к плате

да на самом деле фаервол не пропускал. Задал правило , пинг стали проходить. Спасибо !

да на самом деле фаервол не пропускал. Задал правило , пинг стали проходить. Спасибо ! -

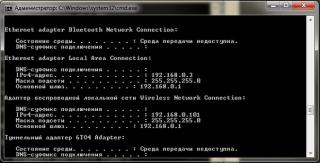

Всем здравствуйте, очень хотел подключиться к Zinq'у по FTP и посмотреть допустим в каком -нибудь Far'e папочки которые есть в файловой системе на плате

На Zinq'e стоит Ubuntu 12.10. Посмотрел - поискал как выставить сетевые настройки на Ubuntu, вроде бы получилось. Подключил кабелем к ноуту, лампочки загорелись. Стал пинговать с ноута пакеты прроходят, стал пинговать в обратнм направлении - облом. Причем заглянул в арп таблицу на плате там все в порядке , как я думаю :rolleyes:

На Zinq'e стоит Ubuntu 12.10. Посмотрел - поискал как выставить сетевые настройки на Ubuntu, вроде бы получилось. Подключил кабелем к ноуту, лампочки загорелись. Стал пинговать с ноута пакеты прроходят, стал пинговать в обратнм направлении - облом. Причем заглянул в арп таблицу на плате там все в порядке , как я думаю :rolleyes: подскажите где что подкрутить чтобы пинг прошел с платы на ноут ?

прикрипел настройки компа и платы , так на всяк случай . :laughing:

-

У меня еще вопрос как по перепаду выскочастотного клока зафиксировать перепад низкочастотного клока? Или то что при ВЧ импульсе n-1 НЧ сигнал был 0, а при ВЧ импульсе n НЧ сигнал стал 1.

reg [2:0] low_freq_pipe; always @(posedge high_freq_clk) begin low_freq_pipe <= {low_freq_pipe[1:0],low_freq_clk}; end wire low_freq_rise_edge = !low_freq_pipe[2] & low_freq_pipe[1]; wire low_freq_fall_edge = low_freq_pipe[2] &!low_freq_pipe[1]; -

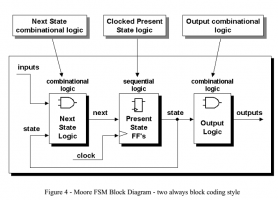

Нахожусь в ступоре :) Когда возник вопрос "а как собственно описывать автомат правильно" , то на просторах интернета нашел "Synthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 Enhancements" от Sunburst Design. Там много всяких техник описано, но про один always блок было упомянуто как о технике которую надо избегать.

Зато имеется гигантская разница в возможных последствиях в части недостижения требуемой скорости работы в целом при использовании комбинаторно вычисленного следующего состояния автомата где либо, кроме как для занесения его в регистр, хранящий текущее состояние. Плохой стиль, именно использовать следующее состояние. Поэтому, лучше сразу предупредить все попытки его использования, априори не давая доступа к нему.Да к вроде бы следующее состояние (NEXT) и используется исключительно для определении текущего (STATE), согласно "two always block coding style".

-

Отвратный стиль

интересно, а Вы как тогда описываете автоматы ? В одном always блоке ?

-

имеет множество бонусов, в том числе когда блок инстансируешь можно скопировать, и остается только точки доставить (в случае блокнота++ единым столбцом за один раз) и в скобки сигналы, быстрее чем направление и разрядность резать.

в ISE есть View HDL Instantioation template, даже копировать ничего не приходится :)

-

Недавно читал книгу, так в ней сказано, что не стоит экономить на строках повышающих понимаемость кода, это влечет к потере $3.48 при заработной плате в $100.000 в год .

There is no economic reason to reduce the number of lines of code. Unless, of course, it also improves the maintainability. Saving one line of code, with an average of 50 characters per line, saves only 50 bytes on the storage medium. With 10Gb hard drives costing less than $300 today, this represents a savings of $28x10-9. The time saved in typing, assuming an extremely slow typing speed of one character per second and a loaded labor rate for an engineer at $100,000 a year, amounts to $0.69. However, if saving that line reduces the understandability of the code where it will require an additional 5 minutes to figure out its operation, the additional cost incurred amounts to $4.17. The total loss from reducing code by 1 line equals $3.48. And that is for a single line, and a single instance of maintenance.

There is no economic reason to reduce the number of lines of code. Unless, of course, it also improves the maintainability. Saving one line of code, with an average of 50 characters per line, saves only 50 bytes on the storage medium. With 10Gb hard drives costing less than $300 today, this represents a savings of $28x10-9. The time saved in typing, assuming an extremely slow typing speed of one character per second and a loaded labor rate for an engineer at $100,000 a year, amounts to $0.69. However, if saving that line reduces the understandability of the code where it will require an additional 5 minutes to figure out its operation, the additional cost incurred amounts to $4.17. The total loss from reducing code by 1 line equals $3.48. And that is for a single line, and a single instance of maintenance. -

Первое - нужно установить региональный стандарт "Английский (США)".

Вот этого я как раз и не сделал , огромное спасибо за оказанную помощь! :a14:

-

-

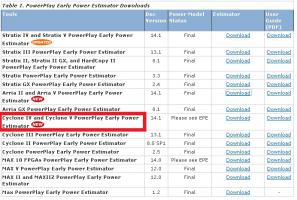

Всем здравствуйте ! Искал я тут доку о каком- нибудь среднем потреблении мощности вышеупомянутой SoC, но наткнулся на "PowerPlay Early Power Estimators (EPE) and Power Analyzer". Но в этой замечательной программке я никак не могу выбрать, интересующий меня чип (5CSXXXXX), все что есть это ЕР4ХХХ. У кого нибудь получилось посчитать потребление для Cyclon V SoC с помощью этой программы? Поделитесь секретом пожалуйста ?

-

извиняюсь конечно , что вот так влезаю ... но вопрос назрел, и как раз из этой оперы.

У меня имеется spartan с внутренней flash'кой. Доступ к памяти осуществляется через примитив SPI_ACCESS, соответственно по интерфейсу SPI. В доках сказано, что частота на которой может работать данный примитив 50/33 МГц, в зависимости от команды. Моя системная тактовая 51.2 МГц. Вся синхронная логика модуля тактируется на частоте 51.2 МГц а на вход примитива данные поступают со скоростью 25.6 МГц, чтобы влезть в тайминг. Вот так:

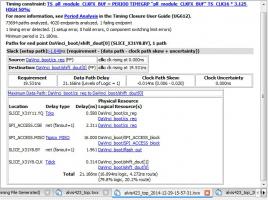

reg clk_div; //---------------------------------------------------- // Flash clock generator //---------------------------------------------------- always @(negedge system_rst or posedge system_clk) if (!system_rst) clk_div <= 1'b0; else if (flash_state == TRANSFER) clk_div <= !clk_div; else if (flash_state == TRANSFER_STOP) clk_div <= 1'b0; //---------------------------------------------------- // Flash chip select generator //---------------------------------------------------- always @(negedge system_rst or posedge system_clk) if (!system_rst) cs_reg <= 1'b1; else if (flash_state == CS_ON) cs_reg <= 1'b0; else if (flash_state == CS_OFF) cs_reg <= 1'b1; //---------------------------------------------------- // Flash shift data input register //---------------------------------------------------- always @(posedge system_clk) begin if (flash_state == NOP2) shift_din <= mux_load; else if (bit_count == 3'b111 && TRANSFER && clk_div) shift_din <= mux_load; else if (clk_div) shift_din <= {shift_din[6:0],1'b0}; end wire SPI_CLK = (flash_state == TRANSFER) ? (clk_div) : 1'b1; wire MOSI_OUT = (flash_state == TRANSFER) ? shift_din[7] : 1'b1; SPI_ACCESS #( .SIM_DEVICE("3S700AN") ) SPI_ACCESS_block ( .MISO (flash_out), // 1-bit SPI output data .MOSI (shift_din ), // 1-bit SPI input data .CSB (cs_reg), // 1-bit SPI chip enable .CLK (SPI_CLK) // 1-bit SPI clock input );Из отчета, на сколько я понимаю, неприятности происходят из-за того что cs_reg тактируется на системной тактовой. Ну и черт с ним, данные же заходят с частотой clk_div. И при конфигурации ПЛИС не возникает никаких неприятностей, все работает как и должно. Но очень уж меня раздражает надпись 1 ERROR напротив Timing Constraints. Как бы мне от нее избавиться ?

Прошивка FLASH xcf04s (Spartan 3e)

в Работаем с ПЛИС, области применения, выбор

Опубликовано · Пожаловаться

А на пинах M[2:0], какой режим конфигурации у Вас выбран ? Я так полагаю они должны задаваться на плате какими-то джамперами .