TiNat

Свой-

Постов

97 -

Зарегистрирован

-

Посещение

Весь контент TiNat

-

Добрый день. Полазил по ссылкам, приведенным выше. С ходу не нашел то, что меня интересует. А именно: может кто подскажет приемлемый вариант комплекта зондовая станция+измеритель для измерения ВАХ, ВФХ характеристик элементной базы (транзисторы, резисторы, конденсаторы). Постараюсь кратко описать предполагаемые требования (они у нас самих пока что не до конца сформулированы, все обсуждаемо). 1) Зондовая станция с возможностью измерения пластин 100, 150, 200 мм. Интересен вариант автоматической загрузки пластин. Изолированная измерительная зона (не зависит от климата окружающей среды), интересен вариант с быстыми измерениями на плюсовой температуре. 2) Матрица коммутации + зондовая голова. Необходимо проводить измерения при зондовой голове на 2 вывода, 35 выводов, 40 выводов. Расположение тестовых площадок - стандартное для нас. 3) Измеритель. НЕ требуется точность по току в области "фемто", НЕ требуются измерения с помощью изолированных проводов, НЕ требуются измерения RF. Что необходимо: измерение токов не ниже 1пА, предел по току - можно не выше 100мА. Приемлемая точность задания напряжения с источника, интересен вариант иметь возможность подавать до 700В. Интересен вариант с зашитыми вариантами схем включения тестовых элементов с n источками тока и m источниками напряжения. Интересен вариант с зашитыми алгоритмами стандартных современных измерений (например пороговое напряжение транзистора по методике gMax, другие подобного рода схемы, работаюшие на измерении и обработке по сути первых производных функций). Должна присутствовать возможность калибровки. 4) Сама работа должна быть поставлена следующим образом: оператору предоставляется перечень параметров на все заложенные тестовые элементы, ему необходимо интуитивно понятно составить измерительную программу, позволяющую за одно контактирование к тестовой линейке провести измерение ХХХ параметров и сохранить их в выходном файле (например excel формат) Возможно я написал какие-то банальные вещи, для тех, кто с этим работает. по итогу, может кто-то подскажет готовый вариант. Может кто-то работает с таким оборудованием. Интересен диапазон цен и возможность установки и наладки данного оборудования. Заранее спасибо.

-

Я именно такой код и использовал. Но можно вместо этого кода использовать следующий: ih = car(setof( instHead cv~>instHeaders instHead~>libName == "projlib" && instHead~>cellName == "pmos")) dbSetInstHeaderMasterName(ih "new_projlib" ih~>cellName ih~>viewName) Результат аналогичный.

-

Спасибо. Опробую такой вариант.

-

Можно. Но в этом случае поменяется ссылка во всех ячейках, которые относятся к старой библиотеке. А мне надо поменять ссылку только одного типа ячейки (поэтому я могу поставить два условия: cell name = pmos и lib name = projlib к примеру).

-

Добрый день. Использую Cadence 5141. В Virtuoso Layout Editor хочу заменить элементы одной библиотеки такими же элементами из другой бибилотеки. Выбираю команду Search... и там использую опцию replace. В случае если число элементов к примеру 70000, они выделяются за ~10 секунд, если их число 120000, то времени необходимо больше, но незначительно: ~30 секунд. Но если их число 180000, то cadence виснет. Я ждал порядка часа, но элементы так и не выделились, при этом, память на машине не забита. Кто-небудь может подсказать, это глюк Cadence, или у них зашито в программе количество выделяемых объектов в какой-небудь буфер. Можно ли вообще побороть такую проблему? P.S. Такая же проблема возникла и в Schematic Editor при выделении большого числа объектов.

-

Посмотри А.Г. Алексенко, И.И. Шагурин "Микросхемотехника", такая старая книжечка. Там что-то подобное было.

-

Я сам вопрос задал, сам на него и отвечу. В причине я разобрался. При разработке правил RCX на этапе создания скрипта (script initialization) необходимо использовать опцию -length_units и указать значение метры (meters), т.к по умолчанию значение опции -length_units в микронах. В правилах LVS все параметры были экстрагированы в метрах, следовательно в случае выходного формата Extracted View (формат с паразитами) значение в метрах воспринамилось как в микронах, и результат был нулевым.

-

Добрый вечер. Из моего опыта проведения LVS в Calibre и последующего проведения PEX могу предположить: при проведении PEX до включения самого блока правил PEX Calibre проводит обычный LVS. Сразу напрашивается вариант по Вашему описанию такой, что влияют некоторые опции правил, которые начинаются с ключевого слова LVS*. Например, самый очевидный вариант - это LVS FILTERING. Т.е. у Вас эти резисторы, возможно, отфильтровываются, с образованием разрыва цепи (либо с образованием закоротки). Это можно посмотреть в самом тексте правил. Также было интересно посмотреть и сравнить Ваш LVS-репорт при проведении обычного LVS и при проведении PEX. Интересует количество девайсов и нетов до и после трансформации. Может быть смогу помочь, если увижу эти данные.

-

Не могли бы уточнить, в каких пакетах Вы видели папку gift. Я не нешел ни в одном пакете Cadence, с какими приходится работать.

-

Скорее всего я разобрался почему XFAB периметр считает по трем сторонам, и это, на мой взгляд, правильно. В Spectre для модели bsim3v3 помимо параметра cjsw (удельной емкости боковой части стокового/истокового p-n перехода) есть парметр cjswg (удельная емкость боковой части стокового/истокового p-n перехода в сторону канала транзистора). По умолчанию cjsw=cjswg (когда нет возможности определить cjswg), в этом случае периметр стоковых/истоковых областей можно считать по четрыем сторонам. Spectre считает емкость перехода по следующей формуле: cd = ad x cjbs + pd x cjbssw – Weff x cjbssw + Weff x cjbsswg, где cjbs функция от cj, mj и pb; cjbssw функция от cjsw, mjsw и pbsw; cjbsswg функция от cjswg, mjswg и pbswg. Слудует обратить внимание на Weff - эффективная ширина канала. Теперь представим, что в нашей топологии имеются транзисторы, у которых затвор имеет перегибы. В этом случае при экстракции необходимо учитывать изгибы (колени) затвора и пересчитывать их в эквивалентное значение ширины канала. Тогда Weff для данного транзистора не будет равно длине грани, где затвор соприкасается с областью стока (истока). Поэтому правильно будет считать периметр по трем сторонам, а в файле модели (в subckt) к рассчитанному периметру добавлять рассчитанное значение Weff. В этом случае будет учтена ошибка (резность длины грани, где затвор соприкасается с областью стока (истока),и Weff). Если транзисторы в design kit запрещено рисовать с перегнутыми затворами, то в этом случае pd и ps можно считать по четырем сторонам.

-

В Cadence лучше чем документация, идущая с софтом Вы ничего не найдете, мое мнение.

-

Без библиотеки рамок он бесполезен.

-

Design kit тут не причем, его угадывать не надо. Я пишу правила, для техпроцесса, имеющегося на нашей фабрике. При написании правил для RCX возникли проблемы, описанные в моем посте. Я понимаю, что там какой-то маленький нюасн, до которого я недорубил. Может кто-то тоже при разработке правил с таким сталкивался, поэтому и задал вопрос.

-

Да, имеется простой модуль напсанный на SKILL и может подключаться к любому проекту.

-

Такой модуль можно написать и без использования AutoCAD, хотя результат в AutoCad, возможно, более премлем чем в топологическом редакторе Cadence. У нас он полностью реализован Cadence. Создается библиотека рамок, которые есть на производстве. А далее любой кристалл автоматически подсаживается на выбранную рамку, проиходит "разварка" и подсчитывается длина проволоки. Результат - чертеж в топологическом редакторе Cadence.

-

Добрый день. Не хочу создавать новую тему, напишу здесь. Вопрос к разработчикам правил LVS и RCX в Assura. При запуске RCX в av_extracted view (выходной формат Extracted View) значения параметров as/ad, ps/pd МОП транзисторов нулевые, но если изменить выходной формат на LVS Extracted View, то значения as/ad, ps/pd соответствуют нарисованным. Не могу понять, почему у меня не экстрагируются в av_extracted view значения as/ad, ps/pd в случае выходного формата Extracted View. Кто-небудь сталкивался с таким?

-

Как я вижу, Вы работаете с XFAB. А это значит, что для проведения верификации LVS и для проведения post payout моделирования с паразитами используются 2 разных нетлиста. Про это я и говорю. Если Вы внимательно посмотрите в правила LVS, да и даже в Ваш же log, то увидите, что там стоят опции LVS filtering. Это значит, что при проведении LVS восстановленные паразитные элементы будут игнорироваться. При проведении PEX они не игнорируются, поэтому и возникает ошибка. Предполагаю, что у Вас неправильно инсталлирован design kit, ибо для проведения PEX должна быть автоматом включена галочка netlisting_for_simulation. Как-то так. Либо Вы просто выдрали отдельно правила и пытаетесь их подключать. При этом нужно учитывать, что при запуске необходимо обязательно включать еще и дополнительные опции #DEFINE. А теперь по поводу самой ошибки. Как я считаю, все очевидно. У Вас в топологии не подписаны порты. Или подписаны в неправильном слое. Например, в металле-4, а при этом в правилах LVS стоят настройки для трех металлов. Поэтому пины и не находятся. Решение данной проблемы пустяковое. Нужно только внимательно посмотреть опции загрузки правил.

-

Мы тоже столкнулись с аналогичной проблемой. Работали не только с КМОП процессами, но и с БиКМОП. И нигде в составе PDK аналоговых библиотек не было, хотя на сайте XFAB они указыны. Но т.к нам это было не принципиально, мы с этим не заморачивались и работали с тем, что было.

-

Размеров рамки у меня нет. Может быть этот чертеж поможет. Указаны размеры посаженного кристалла на рамке.

-

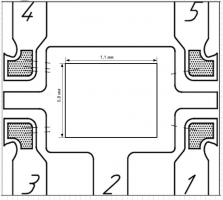

В архиве чертеж рамки корпуса SOIC-8 в формате gds (для выполнения разварки в cadence) и в формате AutoCad. К сожалению, SOT23-6 не нашел, но видел чертеж разваренного кристалла в корпус SOT23-5. Думаю, что резмер крисаллодержателя в этих корпусах одинаков. Размер разваренного кристалла 1,1х0,8 мм. Значительно больший кристалл туда не влезет. SOIC_8.rar

-

Спасибо. Выручили.

-

Спасибо огромное. Это именно то, что мне было нужно. Только для корректного использования мне еще необходим приложенный файл процесса. А в идеале весь PDK (с возможностью инсталляции). Если не сложно, то можете ли Вы выложить tgz архив (я думаю, что он весит 1-5 мегабайт, если больше - то хотя бы файл процесса). И, возможно утерян, а может тогда еще у них не было, но тут нету резистора (resistor.ample). Если я прошу не очень много, то выручите, пожалуйста, еще раз !!

-

Ищу скрипты на ample

TiNat опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

Добрый день. Может у кого-нибудь есть пример скриптов на ample для топологической генерации элементов в Mentor Graphics? Интересуют отдельные девайсы с максимумом возможных опций. Можно из PDK какой-нибудь фабрики, если он не заскриптован. В идеале - если у кого-нибудь есть расскриптованная версия полного стандартного менторовского генератора devices.ample . Рассмотрю "любые варианты" помощи. Заранее спасибо. -

С этим я согласен. Сразу не так Вас понял. Делаю сам что-то типа PDK. Равное и неравное количество истоков я учел. И периметр я рассчитывал по 4 сторонам. Потом посмотрел XFAB и всю транзисторную библиотеку переделал по причине: "на XFAB умные люди работают". Теперь задумался, в чем фишка расчета периметра у XFAB. Задал вопрос на форуме. До сих пор ответа не нашел, а снова переделывать транзисторы не хочется.

-

Все-таки возможно Вы не совсем правильно поняли вопрос. Ссылка на XFAB была просто "к слову". Не будут. Внимательно почитайте мои предыдущие посты и внимательно посмотрите spice-модели. Вопрос остается открытым.