Lixlex

Участник-

Постов

52 -

Зарегистрирован

-

Посещение

Весь контент Lixlex

-

HTG-707

Lixlex ответил Lixlex тема в Работаем с ПЛИС, области применения, выбор

HTG-V7-OPTIC_REV_10_Schematic.pdf -

Возможно будет полезно: https://github.com/lucasbrasilino/net2axis https://fpga-systems.ru/publ/raznoe/interfaces/skript_net2axis/26-1-0-100

-

Здравствуйте. Во сколько примерно обойдется производство мелкой партии (100-500 шт) подобных велофонарей? Только механические части, без электроники.

-

А еще лучше не мучаться с генерацией ip-корок fifo, а вместо этого использовать XPM

-

Вариантов куча. Из того, что сходу пришло в голову: Поднять Ethernet и слать даные UDP-пакетами Взять IP-ядро JTAG2AXI и подключить его к двухпортовой памяти. Использовать UART, если нет требований к скорости

-

В этом случае мы лишь в 2 раза(и то не факт) выигрываем по утилизации, но в 64 раза проигрываем в пропускной способности.

-

А с какой целью интересуетесь? Четких требований пока нет, я хотел бы выяснить, есть ли еще возможность для оптимизации на уровне lps-функций. Пробовал имплементацию под 325й кинтекс - целиком влезла одна E-функция.

-

Если пойти тривиальным путём получается следующая картина: S-функция. На один байт входного вектора расходуется одна ячейка BRAM. Двухпортовой памяти соответственно требуется в два раза меньше. P-функция для FPGA бесплатно L-функция - 2000 lut. В процессорных реализациях используют таблицы предвычислений L и S функций: https://github.com/drobotun/stribog_precalc/blob/master/gost_3411_2012_const.h Но для финального вычисления требуется аж 64 обращения к таблицам, так что для FPGA этот метод выглядит бесполезным. Есть ли другие пути оптимизации этого алгоритма или вся оптимизация возможна только за счет потери пропускной способности?

-

Arria 10 & EMI

Lixlex ответил Novi4ok тема в Работаем с ПЛИС, области применения, выбор

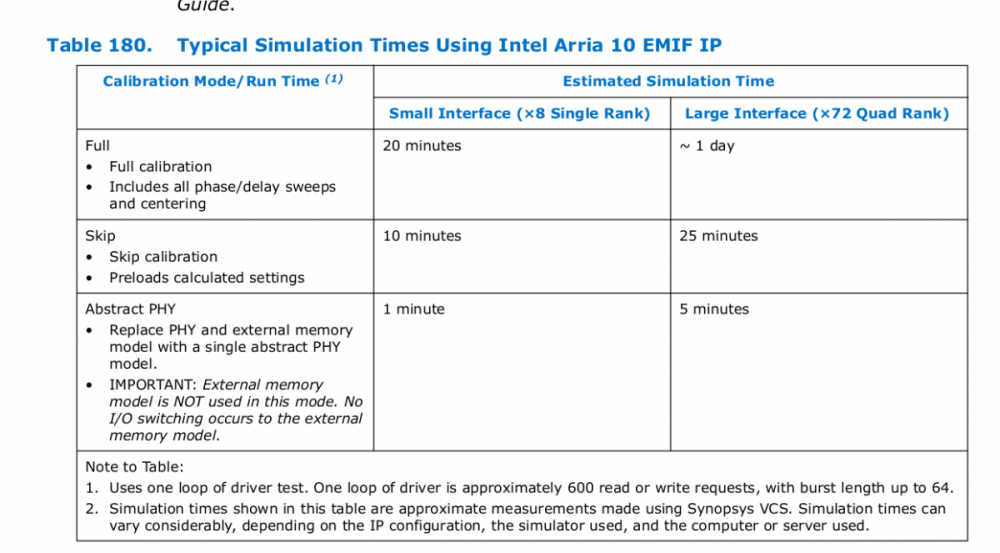

Был ли у кого опыт симуляции DDR4 EMIF ядра? Запустил тестбенч из example design, есть несколько вопросов. 1. Согласно таблице из ug-20115.pdf для 4х-рангового модуля цикл симуляции составляет 1 день. Опция skip calibration значительно сократить время симуляции не помогла, симулируется по прежнему в районе суток. Как получить заявленные ~25минут? 2. Во время симуляции линии DQ, DQS/DQS_n на временных диаграммах ModelSim постоянно в Z-состоянии. Однако тесты проходят, в логах появляются записанные/прочитанные данные. Как вообще такие чудеса возможны? 3. Был ли у кого-нибудь опыт использования Verilog-модели памяти Micron? Хотелось бы заменить интеловскую модель на микроновскую. https://www.micron.com/products/dram/ddr4-sdram/part-catalog/mt40a256m16ge-083e-aut -

PCIe and FPGA

Lixlex ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Благодарю за ответ! А не подскажите в каком документе можно уточнить этот момент? Если действительно данные с одинаковым тегом приходят в строго определенном порядке это немного упростит жизнь. А не затруднит ли Вас подробнее рассказать про заполнение памяти? Из ядра выходит 256-битная axi-stream, соответственно память должна быть аналогичной разрядности. Учитывая, что граница дробления меньше разрядности шины данных, данные подаваемые на вход памяти нужно как-то динамически сдвигать. И всё это дело должно происходить на 250 МГц. Как это сделать не могу представить. Упростит ли мне задачу режим Address Aligned? Правильно ли я понимаю, что в этом режиме, если первый пакет имел валидные данные с 0 по 2й DWORD, то в следующем пакете валидные данные пойдут начиная с 3го DWORDа? -

PCIe and FPGA

Lixlex ответил polyvyannyy тема в Работаем с ПЛИС, области применения, выбор

Спрошу здесь, дабы не создавать отдельный топик. Есть IP-ядро UltraScale FPGA Gen3 Integrated Block for PCI Express. Необходимо обращаться к памяти, расположенной за root complex. Правильно ли я понимаю, что на одиночный запрос Memory Read Request может прийти как целый одиночный пакет с данными, так и несколько "дробленных", причем в произвольном порядке? Какая будет граница данных при дроблении? Как правильно организовать сбор принятых данных? -

Система автосборки Verilog проекта.

Lixlex ответил lexx тема в Управление проектами

Вы бы для начала описали используемый инструментарий(СПАР, семейство FPGA, симулятор), иначе о чем вообще говорить? -

Добрый день! Все верно описали. В простейшем случае используют IP-ядро. Для Xilinx это memory interface generator. Из ядра торчит пользовательский интерфейс - шина AXI 4 и физический интерфейс к памяти. Собственно через AXI 4 ядру передаются команды на чтение и запись. Для вашей платы должен быть reference design с DDR, советую посмотреть. https://www.xilinx.com/support/documentatio...kits/xtp047.pdf

-

Оффтоп: А чем Вас не устроил способ настройки ILA через визард setup debug? Обычно я в отдельной секции кода дублирую исследуемые цепи(для уникальности к имени добавляю какой-нибудь выделяющийся префикс) и помечаю новые цепи директивой mark debug. Таким образом убиваю сразу двух зайцев: 1) Имеем доступ к выходам исследуемых регистров(как известно, если пометить регистр директивой mark debug это нам ничего не даст) 2) После отладки удаляем debug-секцию и получаем чистый код В качестве недостатка способа могу отметить необходимость написания двух строк кода на одну исследуемую цепь(если речь идет о verilog).

-

HTG-707

Lixlex опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, досталась мне плата HTG-707 от хайтек глобал. К сожалению без документации. Писал в саппорт - благополучно отфутболили. Может у кого есть юзергайд на эту плату? Поделитесь пожалуйста. -

Изготовление кабеля SMA2SATA

Lixlex опубликовал тема в Работаем с ПЛИС, области применения, выбор

Хочу подключить sata-девайс к отладочной плате, на которой один из трансиверов выведен на sma-гнёзда. Планирую порезать саташный шлейф, распустить дифпары и соединить с sma-пигтейлом. Нужно получить стабильный линк на SATA gen.1. Был ли у кого-нибудь похожий опыт? -

SATA2->3(xilinx)

Lixlex ответил tolik1 тема в Работаем с ПЛИС, области применения, выбор

Моя проблема оказалась в тактировании oob-части трансивера. Потребовалось завести более медленный клок на CLKRSVD[0] -

SATA2->3(xilinx)

Lixlex ответил tolik1 тема в Работаем с ПЛИС, области применения, выбор

Не буду создавать новую тему, спрошу здесь. Имеется плата Z7 MiniITX на XC7Z100. В режиме SATA gen2. все работает нормально. Перенастраиваю GTX в режим SATA gen1 - получаю следующий эффект: Линк поднимается на некоторое время. Успеваю даже принять Device to Host Register. Через какое-то время получаю rxelecidle на пару тактов, rxcdrlock падает и соответственно следующего ALIGN от девайса больше не получаю. Как себя должен вести rxcdrlock? У меня он в "иголках" но на форумах Xilinx пишут, что это вроде как нормально... Как определить причину, почему пропадает rxcdrlock? -

kintex7+pci-e

Lixlex ответил exigo тема в Работаем с ПЛИС, области применения, выбор

Нет, пины надо править под вашу плату. -

У xilinx есть корка. Под 6е семейство даже есть вариант ее украсть. Если интересно как, расскажу в личку.

-

Неоднократно натыкался на подобные глюки Vivado. Видимо неспроста все советуют использовать сторонние инструменты симуляции.

-

Альтернатива RFID

Lixlex ответил ssvSerge тема в Вопросы системного уровня проектирования

С герконами пропадает возможность идентифицировать каждый объект -

Макет на kintex 7, но есть возможность перенести всё это дело на цинк. Смотрел в сторону petalinux, но там, как я понял, тоже не всё так просто, да и с линуксом у меня нет опыта(в плане сборки ядра и написания драйверов)

-

Думал про этот вариант, в крайнем случае буду вынужден пробивать его. А как дешевле всего организовать передачу данных от одноплатника к плисине?

-

Приветсвтую! Выбор интерфейса остается за мной, главное, чтобы привод был доставабельным.

.thumb.jpg.780e93313383270b40237636cde9f7b4.jpg)