Zigor

Участник-

Постов

39 -

Зарегистрирован

-

Посещение

Весь контент Zigor

-

Данные от endpoint PCIe

Zigor опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Вопрос скорее про сам PCIe, но тем не менее) Запустил обмен данными по PCIe, имеется RC на Сyclone V GX и EP на Cyclone V GT. Перетащил драйвера линукса под голый NoisII, подшлифовал, система енумеруется, настраиваю устройства в EP. Nios в RC отсылает данные через порт TxS, EP ловит их BAR0. Хочу чтобы EP отсылал данные в RC самостятельно, без запросов. Для этого включаю соответствующий бит в COMMAND_REGISTER чтобы EP работал как мастер, разрешаю обращения к памяти. 1. При подключенное EP напрямую к RC данные пересылаются без проблем, корка в EP засовывает их в порт TxS, в RC получаю их с порта RxM. 2. Если подключаю EP через плату свича на XIO3130, при условии что порты XIO3130 настраиваю (командный регистр, номера шин, диапазоны адресов всего 6 параметров), то могу так же обращаться к IP ядрам в EP устанавливать и читать параметры по адресам, но данные которые шлет EP - до RC уже не доходят. Порты в RC и в XIO3130 настраиваю одинаково, диапазон адресов, биты в коммандном регистре. Спасибо! -

Да, для начала надо поднять шину без ОС. Напрямую с ниоса. В принципе ничего сложного быть не должно. Т.е. читай конфиг пространство и прописывай туда индексы шин. Но при попытки прочитать что-то из ConfigSpace своего RootPort на котором сидит ниос - в ответ тишина. Через Avalon я не могу посмотреть ConfigSpace. Может надо в HIP PCIe что-то еще включить чтоб можно было отправлять и принимать TLP? Т.е. какая последовательность обращений к своему RP должна быть?

-

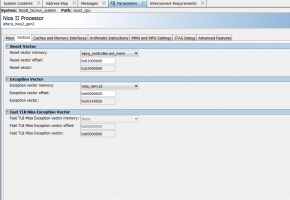

Добрый день! Пытаюсь прочесть конфиг. пространство PCIe RootPort из NiosII. Просмотрел исходники Linux, использую функции для общения через интерфейс TLP на шине CRA. К рутпорту цепляю endpoint - система переходит в L0 и DataLinkLayer работает. Используемая функция: pcie-altera.c static int tlp_cfg_dword_read(struct altera_pcie *pcie, u8 bus, u32 devfn, int where, u8 byte_en, u32 *value) { u32 headers[TLP_HDR_SIZE]; if (bus == pcie->root_bus_nr) headers[0] = TLP_CFG_DW0(TLP_FMTTYPE_CFGRD0); else headers[0] = TLP_CFG_DW0(TLP_FMTTYPE_CFGRD1); headers[1] = TLP_CFG_DW1(TLP_REQ_ID(pcie->root_bus_nr, RP_DEVFN), TLP_READ_TAG, byte_en); headers[2] = TLP_CFG_DW2(bus, devfn, where); tlp_write_packet(pcie, headers, 0, false); return tlp_read_packet(pcie, value); } Посылаю конф.запрос type 0 на чтение шины 0, dev 0, func 0 (на что должен откликнуться Rootport). Т.е. это самая первая операция которую я делаю до енумерации. Заголовок TLP header: [0] 0x04000001 [1] 0x00001D0F [2] 0x00000000 Функция возвращает PCIBIOS_DEVICE_NOT_FOUND. Корректен ли мой отправляемый рутпорту запрос/пакет? Спасибо!

-

Затык в том, что непонятен сам механизм общения с HIP PCIe Altera. Пишу Configuration Type 0 Request в CRA TLP TX. В ответ тишина. Как прочитать Configuration Space рутпорта? Как отправить конф запрос в endpoint? Записывать пакет в CRA TLP TX и опрашивать RP_RXCPL_STATUS?

-

rootport поднял на плате terasic DE1, будет работать под линуксами. Сейчас отлаживаюсь по Avalon-JTAG Master Сначала необходимо отладить enumeration без операционки. И вот тут возникает непонимание - 1. Что значит перебирать bus, device, function - когда у тебя в Qsys есть твой HIP Root и подключенный к нему Avalon-JTAG Master? Где их читать.. и как)) 2. Чтение документации Altera не дает понимания по какому адресу лежит Type 1 Configuration Space Header, в документации сказано 0x000:0x03C. Если имеется в виду абсолютное смещение в CRA, то чтение 0го адреса дает нули вместо Device ID и Vendor ID. Спасибо за помощь!

-

PCIe enumeration

Zigor опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Собрал систему из отладочных плат для проверки PCIe. Линк работает, rootport перешел в L0 Теперь стоит задача сделать енумерацию устройств на шине, пока что одной endpoint, потом через switch. Где можно как это делается, пример драйвера на С? Спасибо! -

Ошибки в Modelsim

Zigor ответил Zigor тема в Среды разработки - обсуждаем САПРы

Для отладки в моделсиме собрал проект где есть и EndPoint и RootPort. Может в этом причина? Изначально стоит задача отладить RootPort - с ним в железе проблемы. -

Ошибки в Modelsim

Zigor опубликовал тема в Среды разработки - обсуждаем САПРы

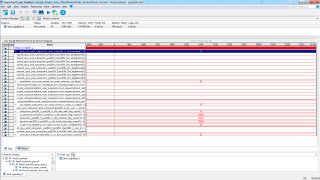

Добрый день! Отлаживаю систему с PCIe. В железе не пошло - пробую Modelsim 10.4. Пишу на VHDL. При запуске начинает сыпать такого типа сообщениями # vsim -gui -l msim_transcript -do "PCIe_sim_run_msim_rtl_vhdl.do" # Start time: 16:36:38 on Oct 24,2016 # ** Note: (vsim-3812) Design is being optimized... # # ** Error (suppressible): E:/_ilya/_Project_Avia/_AlteraWorks/PCIe_sim/PCIe_sim_system/synthesis/submodules/PCIe_sim_system_EndPoint_subsystem.vhd(1385): (vopt-1130) Port "hpg_ctrler" of entity "altpcie_cv_hip_avmm_hwtcl" is not in the component being instantiated. # # ** Error (suppressible): E:/_ilya/_Project_Avia/_AlteraWorks/PCIe_sim/PCIe_sim_system/synthesis/submodules/PCIe_sim_system_EndPoint_subsystem.vhd(1385): (vopt-1130) Port "RxmAddress_1_o" of entity "altpcie_cv_hip_avmm_hwtcl" is not in the component being instantiated. ........ # ** Error (suppressible): E:/_ilya/_Project_Avia/_AlteraWorks/PCIe_sim/PCIe_sim_system/synthesis/submodules/PCIe_sim_system_RootPort_subsystem.vhd(1242): (vopt-1130) Port "IntxReq_i" of entity "altpcie_cv_hip_avmm_hwtcl" is not in the component being instantiated. # # ** Error (suppressible): E:/_ilya/_Project_Avia/_AlteraWorks/PCIe_sim/PCIe_sim_system/synthesis/submodules/PCIe_sim_system_RootPort_subsystem.vhd(1242): (vopt-1130) Port "rx_st_data" of entity "altpcie_cv_hip_avmm_hwtcl" is not in the component being instantiated. # # Optimization failed # Error loading design Как это можно побороть? Спасибо! -

Добрый день! На макетных платах отлаживаю работу системы с PCIe gen1 x1. Плата Altera Cyclone V GT (endpoint) и Terasic DE1 Cyclone V GX с платой расширения hsmc->PCIe в качестве rootport. Качество линка предварительно проверил гоняя данные трансиверами на той же 2.5Gb скорости. Все поет и пляшет в обоих направлениях. Когда доходит дело до проектов с HIP PCIe от Altera дело дальше link training не идет. Синхронно запускаю сигналтап на обоих платах: Со стороны endpoint ltssmstate доходит до 00010: Polling.Active Со стороны rootport - 00001: Detect.Active и потом сваливается в 00000: Detect.Quiet. Как можно отладить/посмотреть что они первоначально друг другу шлют? Те же самые TSы... Спасибо!

-

Прошивка в EPCQ256

Zigor опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Добрый день! Работаю с отладочной платой Terasic DE1 Cyclone V GX Неделю ломаю голову над размещением прошивки в EPCQ256. В примерах от Terasic сделано просто elf в виде hex цепляется в памяти nios в qsys. Данный метод лишен изящества и гибкости. Хочу размещать sof а потом hex по заданному оффсету. Путем перекапывание форумов и документации и тестирования разных методов на данный момент устаканил следующий вариант: sof2flash --input="NiosII_txLinux.sof" --output="software/NiosII_txLinux_epcq_HW.flash" --epcq –verbose elf2flash --input="software/NiosII_txLinux/NiosII_txLinux.elf" --output="software/NiosII_txLinux_epcq_SW.flash" --base=0x22000000 --end=0x23FFFFFF --reset=0x23000000 \ --boot=c:/altera/15.1/ip/altera/nios2_ip/altera_nios2/boot_loader_epcq256_cv.srec --save nios2-elf-objcopy -I srec -O ihex "software/NiosII_txLinux_epcq_SW.flash" "software/NiosII_txLinux_epcq_SW.hex" Далее в Convert Programming Files добавляю SOF с 0го адреса Ставлю "Compressed" По абсолютному адресу добавляю HEX, вижу что оффсет правильный - 0х01000000 Выбираю Active Serial x4 Конверчу (в map файле тоже смещение верное) Заливаю квартус программером Вижу что логика инициализируется-стартует а ниос нет( Спасибо! -

Как именно? С выхода трансиверов данные завести на фифо?

-

Да... этот топик уже видел. Назначил ручками в редакторе - фиттер так же орет(((

-

Fitter ругается на недостаток LAB

Zigor опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Разрабатываю проект на основе платы Terrasic DE1 (Cyclone V GX). принимаю данные с JESD АЦП, загоняю в блоки обрабоки, контролирую весь процесс с NiosII. Все работало без чудес. Добавил немного функционала - Fitter стал ругаться: Error (170025): Fitter requires that more entities of type LAB be placed in a region than are available in the region Error (170026): Region "lower-left" corner: X1_Y9; Region "upper-right" corner: X25_Y34 Похоже, ему перестал нравится мой блок управления гигабитными трансиверами и приема данных, который с помощью сигнала bitslip синхронизируется с потоком данных от АЦП. Хотя тоже странно - этот блок давно отлажен и работает в разных проектах. Проект занимает меньше половины кристалла: Logic utilization (in ALMs) 12,194 / 29,080 ( 42 % ) Очень не хочется дробить проект на более мелкие. Может кто-то сталкивался с чем-то подобным? -

Минимальный датарэйт трансиверов 614Мбитс, у меня 1000Мбитс Поставил, только не после трансиверов а после ядра - вытащил то что можно для отладки трансиверов согласно рекомендациям из альтеровской даташиты на ядро (стр 7-3) 1. Инициализирую АЦП и генератор 2. Ресечу секвенсер 3. Поднимаю ресеты трансивера | link | frame 4. Устанавливаю в регистре SYNCN_SYSREF_CTRL значения csr_rbd_offset csr_lmfc_offset csr_sysref_singledet | csr_sysref_alwayson | csr_link_reinit 5. Снимаю ресеты трансивера | link | frame Вижу картинку в STP Картина не меняется если пропускаю пункты 3-5 Трансиверы в LTD моде, PHY_CLK с каждого прет 25Мгц как и положено (смотрю на осциллографе). Но больше ничего не происходит, kchardata в нулях.

-

Link Clk == Lane_Data_Rate / 40 - согласно даташиту ядра от Альтеры В АЦП сериализация 20х, частота сэмплирования 50 * 20 == 1000 К меняю на 20 и в АЦП и я ЯДРЕ, это не воспрещается)))

-

Jesd204b & Cyclone V GT

Zigor опубликовал тема в Работаем с ПЛИС, области применения, выбор

Добрый день! Собираю систему на Cyclone V GT Development Kit и вот такой платы АЦП http://dallaslogic.com/prod_dev-adc34j/ В качестве примера взял дизайн https://www.altera.com/en_US/pdfs/literature/an/an729.pdf с NiosII и Альтеровским Jesd IP Настройки системы JESD LMF 442 N 12 NP 12 K 20 Fsampling 50 MHz Datarate 1000Mbs Device clock 100 MHz Sysref 2.5 MHz Link clk 25 Mhz Frame clk 50 MHz Приемник не переходит в фазу ILA, вываливает ошибки SYSREF период и PHASE Compensation FIFO Empty Частоту Sysref пробовал ставить 1.25Мгц - та же ошибка Если link clk поднять до 50Мгц то ошибка PHASE Compensation FIFO Empty пропадает, но 50Мгц противоречит расчетам из datasheet (1000 / 40). С Jesd да и с трансиверами опыта работы не было - что можно предпринять для отладки? -

Добрый день! При компиляции проекта в Quartus15 столкнулся с ошибкой : Error (10003): Can't open encrypted VHDL or Verilog HDL file "/synthesis/submodules/DE0_NANO_SDRAM_SYS_nios2_qsys.v" -- current license file does not contain a valid license for encrypted file Кто-нибудь сталкивался с подобным?

-

инициализация линка PCIe без выключения питания

Zigor опубликовал тема в ISA/PCI/PCI-X/PCI Express

Добрый день! Стоит задача разработать систему с передачей данных от PCIe endpoint к rootport. Использую отладочную плату на Cyclone V GT - https://www.altera.com/products/boards_and_...clone-v-gt.html На начальном этапе заливаю пример http://www.alterawiki.com/wiki/Reference_D...DMA_-_Cyclone_V Проверяю наличие платы в системе (Win7) прогой http://teledynelecroy.com/protocolanalyzer...px?seriesid=447 После включения питания материнки и загрузки системы плата определяется. Если заново сконфигурировать альтеру то система плату не находит. Возможно спрошу дурь, но я еще в начале процесса приседаний с PCIe, поэтому не обессудьте))) Вопрос - каким образом можно перезапускать инициализации линка PCIe в системе после загрузки циклона без выключения/включения питания материнки? Спасибо! -

Добрый день! 1. Начинаю работу с отл.платой на Cyclone V GT. При попытке запустить программу Board Test System от Altera - программулина слетает. Пробовал и на ноутбуке и на десктопе. С подключенной по сети платой и без. 2. В Quick Start Quide для платы дается указание чтоб прошивать плату новой прошивкой BTS (стр 3) файлом (<installation directory>\kits\ cycloneVGT_5cgtfd9ef35_fpga\factory_ recovery\build_factory_source\bts_config. flash) Но в указанной директории файла bts_config.flash нет))) Спасибо!!!!

-

Гибридная схема модема

Zigor опубликовал тема в Вопросы аналоговой техники

Добрый день! Проектирую систему связи на QAM для медного кабеля. Несущая downstream 100кГц - обратно 10-20кГц. Направьте пожалуйста в нужное русло - где и что почитать по гибридным схемам. Может есть готовые AFE для таких случаев? Спасибо! -

Расчет петлевого фильтра

Zigor опубликовал тема в Алгоритмы ЦОС (DSP)

Добрый день! 1. Рассчитываю петлевой фильтр, сделал файл в екселе, подставляю значения из примера на стр265 (см источник во вложении) - получаются другие константы для фильтра. Что еще учитывается в расчетах? 2. Посмотрел модельку http://www.mathworks.com/help/comm/example...tured-data.html В инициализации Kp рассчитывается как SimParams.TimingRecTEDGain = 2.7*2*K*A^2+2.7*2*K*A^2; % K_p for Timing Recovery PLL, determined by 2KA^2*2.7 (for binary PAM), QPSK could be treated as two individual binary PAM, 2.7 is for raised cosine filter with roll-off factor 0.5 Как рассчитывать передаточный коэффициент для QAM16, QAM64? Спасибо! synchronization_notes.pdf pll_loop_filter_calc.zip -

По эквалайзеру для QAM16

Zigor ответил Zigor тема в Алгоритмы ЦОС (DSP)

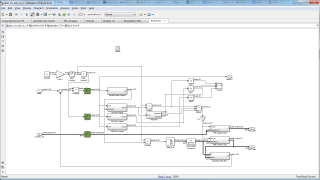

Честно говоря отличий много - за основу взята модель заточенная под HDL (http://www.mathworks.com/help/comm/examples/hdl-optimized-qam-transmitter-and-receiver.html) Перевел с QAM64 на QAM16 Отказался от блока грубой подстройки частоты RRC фильтр в приемнике и интерполятор работают на частоте дискретизации 8 сэмплов на такт (в исходной модели Zero Cross TED) В исходной модели примитивный 1-Tap DLMS подстраивается по 14 символьной преамбуле, я отказался от этой идеи и прикрутил блок эквалайзера по образцу модели с форума с FFE работающим на 2 сэмпла и следом уже схемой кручения фазы и FBE, 1 отсчет на такт. Этот блок пока что в плавающей точке для проверки идеи. Можно я Вам в личку куда-нибудь модель закину чтоб на пальцах не объяснять масштаб бедствия ))) ? -

По эквалайзеру для QAM16

Zigor ответил Zigor тема в Алгоритмы ЦОС (DSP)

Вы имеете ввиду изменения в моей модели относительно опорной? -

По эквалайзеру для QAM16

Zigor ответил Zigor тема в Алгоритмы ЦОС (DSP)

Вот с этим то у меня проблемы, если выкидываю смещение фазы из канала и соответственно выкидываю умножение на сопряженную ошибку, то эквалайзер отстраивается, Если же умножаю на заранее постоянное известное смещение по фазе (которое сам руками задаю в канале, сдвиг по частоте == 0) все разваливается. -

По эквалайзеру для QAM16

Zigor ответил Zigor тема в Алгоритмы ЦОС (DSP)

Какой источник посоветуете?