vin

Свой-

Постов

293 -

Зарегистрирован

-

Посещение

Весь контент vin

-

Embedded Linux Software Engineer (Киев)

vin опубликовал тема в Предлагаю работу

Здравствуйте, Разыскиваем под текущие проекты на постоянной основе линукс эмбеддера, уровня middle и выше под платформы TI DM8168 / iMX6/ iMX8 / NVIDIA Xavier/ Allwinner H5 и др. - патчинг ядра - написание драйверов - портирование существующего кода на ARM платформу - C/C++ Территориально нужен Киев или пригород. Детали прошу в личку. Заранее благодарю. Иван -

Altium Designer на виртуальной машине

vin ответил MVJ тема в Altium Designer, DXP, Protel

Здравствуйте Коллеги, а какие видеокарты (производитель + имя/серия) используют тут те, у кого Altium таки работает в VB? -

HART Communication Protocol, EPIC, ProfiBUS

vin ответил vin тема в Предлагаю работу

Разыскиваем также эксперта по HART Communication на почасовую ставку за услуги экспертизы и направление разработки в правильное русло. -

HART Communication Protocol, EPIC, ProfiBUS

vin ответил vin тема в Предлагаю работу

Детали по HART тут https://www.fieldcommgroup.org/sites/defaul...nGuide_r7.1.pdf -

HART Communication Protocol, EPIC, ProfiBUS

vin опубликовал тема в Предлагаю работу

Здравствуйте! На постоянное сотрудничество нужен программист микроконтроллеров под стандарты HART и подобные EPIC, ProfiBUS. Микроконтроллеры семейства TI MSP430. Территориально, Киев. Детали в личку. С уважением, Иван -

IGLOO программист

vin ответил vin тема в Предлагаю работу

ТЗ к сожалению (или счастью) не для розглашения. Поэтому прошу контактировать в личку. -

IGLOO программист

vin опубликовал тема в Предлагаю работу

Здравствуйте! Ищем профи FPGA программиста под проект обработки видео на Microsemi IGLOO. Контакт в личку. С уважением! -

Приветствую! При выгрузке символов DRA из платы BRD выгружаются также все пустые слои (subclass) присутствующие в самой BRD. Подскажите, если ли skill команда которая может убить ВСЕ ПУСТЫЕ СЛОИ (SUBCLASS) АВТОМАТОМ? Заранее благодарю!

-

Здравствуйте! Вопрос по "TRANSPARANT" моде просмотра в 10.7 и 12.1 версиях. На вложении включены паста, силк, маска и топ медь. В 10.7 все "просвечивается" красиво, а в 12.1 просто ужасно. Можно ли 12.1 привести к виду 10.7? Если да, то как? Заранее благодарю.

-

Благодарю!

-

правило: зазор неметаллизированное отверстие до меди

vin опубликовал тема в Altium Designer, DXP, Protel

Здравствуйте, надоело на каждое неметаллизированное отверстие (NPT hole) ложить отдельный кипаут и определять зазор к меди. Вопрос, можно ли задать 1 правило: для всех неметаллизированных отверстий отступ от края отверстия до меди 0.3мм на всех слоях? Если да, то как? Заранее благодарю! -

вопрос по Exposed Pad

vin ответил diwil тема в Работаем с трассировкой

именно, подтверждено TI в их рекомендациях по thermal vias -

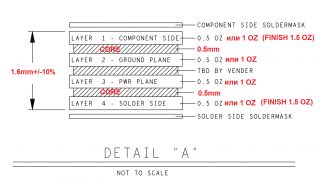

4 слоя, 1.6mm, c 2-мя корами?

vin ответил vin тема в Изготовление ПП - PCB manufacturing

вообщем обошлись стандартной хитростью - положили землю на третьем слое как референс плейн в топу. -

4 слоя, 1.6mm, c 2-мя корами?

vin опубликовал тема в Изготовление ПП - PCB manufacturing

Здравствуйте Коллеги, Возник вопрос по стєкапу: Нужно на внешней стороне платы соблюсти 50 Ом для антены в меди с шириной проводника 0.9мм. При таком условии на ширину проводника (0.9мм) и требуемом импедансе (50 Ом) высота до плейна должна равняеться порядка 0.5мм. Смотрите вложение. Вопросы: 1) Возможно ли склеить такой стэкап из 2-х стандартных коров, чтобы не набирать цену большим количеством слоев препрега? 2) Какой вариант стэкапа наиболее экономически эффективен для такой задачи? Заранее благодарю! -

Пайка печатных плат

vin опубликовал тема в Предлагаю работу

Здравствуйте, Интересуют надежные руки и глаза, чтобы паять прототипы и небольшие количества (десятки штук) одного наименования, в Киеве. -

1) Посчитайте нетлист в CAM350 [utilites-> Netlist Extract]. 2) Экстрактните IPC-D-356 из CAD-а и втяните в CAM350 [Analysis-> Nets-> Import IPC netlist]. 3) Сравните и увидите где КЗ [Analysis-> Nets-> Compare External Nets].

-

Резюме: Для gcc 4.6.x и выше при ВЫКЛюченной опции «Build in thumb mode» все собирается и работает. Для gcc 4.6.x и выше при ВКЛюченной опции «Build in thumb mode» все собирается и НЕ работает.

-

Здравствуйте, На просетапленой плате в CM (Constraint Manager) пропадают настройки из таблицы, которые были ранее прописаны в нее. Самое интересное, что "пропавшие" настройки таки работают, но посмотреть их или поправить уже не получается, ибо соответствующие строки пропали из CM. Сие происходит в версии Allegro 16.5. Кто-то наблюдал подобное?

-

Проблема решена! Бутстрап 3.1 ftp://ftp.linux4sam.org/pub/Android4SAM/v...trap-3.1.tar.gz и "правильный" компилятор (ибо собирается без ошибок разными версиями, но не работает) сделали свое дело.

-

Вывод A13 физически присутствует. Еще не пробовали. Проблема до сих пор не решена.

-

A13 в нуле. Проблема не ушла. Сейчас пробуем варьировать тайминги. Еще идеи есть?

-

Здравствуйте! Собрали свою плату на AT91SAM9G45. 1. Изначально поставили на первую партию DDR2-667 Micron MT47H64M8CF-3, ту что использует и сам Atmel на своих китах. Итого 2 модуля, имеем 128MB ОЗУ и наслаждаемся линуксом.. 2. На следующуюю партию поставили DDR2-800 NANYA NT5TU64M8DE-AC и линукс перестал грузится. Экспериментальным путем обнаружили, что если в инициализации DDR2 в бутстрапе #ifdef CONFIG_DDR2 static SDdramConfig ddram_config; /*------------------------------------------------------------------------------*/ /* \fn ddramc_hw_init */ /* \brief This function performs DDRAMC HW initialization */ /*------------------------------------------------------------------------------*/ void ddramc_hw_init(void) { ddram_config.ddramc_mdr = (AT91C_DDRC2_DBW_16_BITS | AT91C_DDRC2_MD_DDR2_SDRAM); ddram_config.ddramc_cr = (AT91C_DDRC2_NC_DDR10_SDR9 | // 10 column bits (1K) AT91C_DDRC2_NR_14 | // 14 row bits (8K) AT91C_DDRC2_CAS_3 | // CAS Latency 3 AT91C_DDRC2_DLL_RESET_DISABLED); // DLL not reset // ddram_config.ddramc_rtr = 0x24B; ddram_config.ddramc_rtr = 0x4121; ddram_config.ddramc_t0pr = (AT91C_DDRC2_TRAS_6 | // 6 * 7.5 = 45 ns AT91C_DDRC2_TRCD_2 | // 2 * 7.5 = 22.5 ns AT91C_DDRC2_TWR_2 | // 2 * 7.5 = 15 ns AT91C_DDRC2_TRC_8 | // 8 * 7.5 = 75 ns AT91C_DDRC2_TRP_2 | // 2 * 7.5 = 22.5 ns AT91C_DDRC2_TRRD_1 | // 1 * 7.5 = 7.5 ns AT91C_DDRC2_TWTR_1 | // 1 clock cycle AT91C_DDRC2_TMRD_2); // 2 clock cycles ddram_config.ddramc_t1pr = (AT91C_DDRC2_TXP_2 | // 2 * 7.5 = 15 ns 200 << 16 | // 200 clock cycles, TXSRD: Exit self refresh delay to Read command 16 << 8 | // 16 * 7.5 = 120 ns TXSNR: Exit self refresh delay to non read command AT91C_DDRC2_TRFC_14 << 0); // 14 * 7.5 = 142 ns (must be 140 ns for 1Gb DDR) ddram_config.ddramc_t2pr = (AT91C_DDRC2_TRTP_1 | // 1 * 7.5 = 7.5 ns AT91C_DDRC2_TRPA_0 | // 0 * 7.5 = 0 ns AT91C_DDRC2_TXARDS_7 | // 7 clock cycles AT91C_DDRC2_TXARD_2); // 2 clock cycles // ENABLE DDR2 clock writel(AT91C_PMC_DDR, AT91C_BASE_PMC + PMC_SCER); /* * DDRAM2 controller */ ddram_init(AT91C_BASE_DDR2C, AT91C_DDR2, &ddram_config); sdram_init(16); /* * Setup Smart Media, first enable the address range of CS3 in HMATRIX user interface */ // writel(readl(AT91C_BASE_CCFG + CCFG_EBICSA) | AT91C_EBI_CS1A_SDRAMC, // AT91C_BASE_CCFG + CCFG_EBICSA); /* * EBI IO in 1.8V mode */ // writel(readl(AT91C_BASE_CCFG + CCFG_EBICSA) & ~(1 << 16), // AT91C_BASE_CCFG + CCFG_EBICSA); /* * EBI DDRAM controller */ // ddram_init(AT91C_BASE_DDR2CP1, AT91C_EBI_CS1, &ddram_config); } #endif /* CONFIG_DDR2 */ убрать верхний адрес, т.е. поменять AT91C_DDRC2_NR_14 | // 14 row bits (8K) на AT91C_DDRC2_NR_13 | // 14 row bits (8K) то линукс грузится и все работает, но имеем только 64М ОЗУ. Сравнили даташиты Micron & Nanya, практически идентичны по параметрам. Просьба, если кто знает тонкости инициализации DDR2, подскажите куда копать? Заранее благодарю. NANYA_NTC_DDR2_512M_D_R16_Consumer.pdf

-

Нужен RF инженер-консультант

vin опубликовал тема в Предлагаю работу

Здравствуйте, Ищем RF инженера-консультанта для грамотного выполнения дизайнерских работ (частоты 1-10 ГГц и выше) со знанием дела и умением пользоваться соответствующими програмными тулзами. Человек нужен из Киева или пригорода. Оплата почасовая. -

расчёт ширины дорожки

vin ответил Doka тема в Разрабатываем ПП в САПР - PCB development

Рекомендую The Saturn PCB Toolkit is the best resource for PCB related calculations you can find. It incorporates many features that PCB designers and engineers are in regular need of like current capacity of a PCB trace, via current, differential pairs and much more. Please download our PCB Toolkit today for free and enjoy! http://saturnpcb.com/pcb_toolkit.htm -

БЛАГОДАРЮ, за лог! Завтра будет в руках хаб с внешним питанием, попробую через него.