-

Постов

428 -

Зарегистрирован

-

Посещение

Весь контент novartis

-

Мы другую захотели. И цена была такая же, поэтому глючную отправили им обратно, а они нам новую другую прислали. Там все их тесты прогнал, и свои проекты позапускал. Ошибок не было.

-

Купили плату от Терасика с Ариией 10 год назад (DE5a-Net-DDR4). Начал их тесты запускать, дошел до тестов памяти QDRII. Не проходят тесты. Начал разбираться, свои проекты собирать с нуля. Если одну микросхему QDRII в проекте задействую, тест проходит, данные записываются, считываются, никаких ошибок, хоть сутками тестируй. Проверил все четыре микросхемы QDRII по одиночке - нет ошибок. Как только в проекте задействуются две и больше микросхем - изредка начинают идти битовые ошибки в читаемых данных, причем по любому каналу может ошибка прилететь. Переписывалсиь с Терасиком (долгий процесс, то у них китайский новый год, то день независимости Тайваня...), договорились, что они сами потестят плату онлайн, дали им удаленный доступ. Сначала они свои тесты гоняли, потом еще какую то прошивку залили (там какие то расширенные тесты). Ошибки подтвердили, сделали возврат платы и денег.

-

нет. Почему вы такой вопрос задали?) TLP пакет содержит заголовок 16 байт и данные. Хост в простейшем случае может послать IO32 запрос на запись или на чтение, для запроса "запись" в TLP пакете будет заголовок 16 байт и 4 байта данных. Если заюзать функцию типа такой _mm256_storeu_si256, то в TLP пакете будет заголовок 16 байт и 32 байта данных. PCIE пакеты.pdf

-

да, это рабочий вариант Логично) Чтобы хосту записать в плис по pcie 64 байта, нужно отправить 16 TLP пакетов по 4 байта данных, пусть время между TLP пакетами 50нс-100 нс, значит на пересылку 64 байт уйдет 800нс-1600 нс. При дма будет так: хост записывает команду на старт дма, плис посылает TLP пакет на чтение 64 байт, хост отвечает одним TLP пакетом с 64 байтами данных. Где-то 1100 нс выйдет. Я так понимаю Nios+PCIE собраны в QSYS, у модуля PCIE есть порт Txs (Avalon Memory Mapped Slave), если в этот порт послать транзакцию на чтение данных, указать адрес (который неким образом соответствует адресу, переданному с хоста), указать burst (длину читаемых данных), то получится dma. Но у вас к PCIE подключен Nios, не знаю вроде не умеет ниос посылать burst транзакции, он обычными IO операциями по 4 байта оперирует, так что надо ставить dma контроллер, можно свой написать, подключить его к Txs параллельно ниосу.

-

С помощью такой команды можно записать 32 байта за раз _mm256_storeu_si256. Это на чтение они медленные (может и микросекунда быть, зависит от платформы), а на запись пауза между TLP пакетами 50-100нс (ну тоже зависит от платформы)

-

17.1 Standard Спасибо за подсказку, надо глянуть, что в pro выдает (Quartus 19.4 Pro такой у меня установлен)

-

atman скорей всего предлагает такую же плату, как в объявлении на авито, но за 35 тыс. руб.

-

Интел IP ядро Single и Double арифметика

novartis опубликовал тема в Среды разработки - обсуждаем САПРы

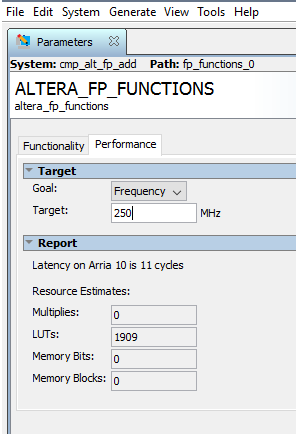

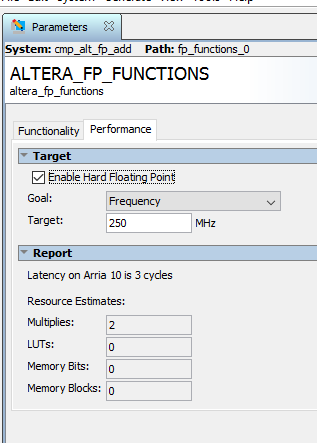

У Интела (Альтеры) есть готовые ip корки для вещественной арифметики. Мне понадобилось сложение. Если выбрать Single формат, то задержка на расчет будет 3 такта на частоте 250МГц и будут задействованы 2 аппаратных блока Аррии 10. А вот если выбрать Double формат, то задержка на расчет будет 11 тактов на частоте 250МГц, и почему то без аппаратных блоков. Это в интеле (алтере) инженеры ленивые и не захотели на аппаратных блоках реализацию писать, или для double есть какие то существенные отличия, сложности? Single: Double: -

можно поэкспериментировать с logic lock регионами, создать одинаковые регионы по размеру и по расположению и там, и там, и запретить размещение других модулей в этом регионе.

-

Нужно сделать: 1). запись в регистр root_conf_space флагов Memory Space Enable, Bus Master Enable (X"00000006") TX TLP пакет: 00000006 00000004 0000000F 44000001 В ответ придет RX TLP пакет: 00000000 00000000 00000004 0A000000 2). запись в регистр root_conf_space номера шины Endpoint устройства (X"00" & PCIE_SECONDARY_BUS_NUM & PCIE_SECONDARY_BUS_NUM & X"00") TX TLP пакет: 00000000 00000018 0000010F 44000001 00000000 00000000 00000000 00010100 В ответ придет RX TLP пакет: 00000000 00000100 00000004 0A000000 3). Можно читать регистры root_conf_space Запрос: 00000000 00000000 0000020F 04000001 Ответ: 00000000 00000200 00000004 4A000001 00000000 00000000 00000000 00014987

-

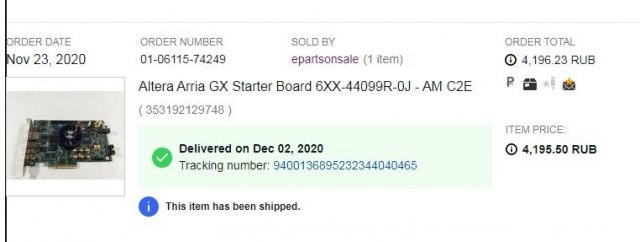

Купил эту плату на ebay в декабре, вместе с доставкой вышло чуть больше 5 тысяч рублей. Включил, лампочки мигают, на большее пока руки не дошли, купил именно из-за низкой цены и на предыдущей работе с ней много работал, нормальная плата. Помню у продавца их много было (>10 шт), сейчас нет, еще и в описании было написано с ошибкой, что это просто Arria GX, а не Arria V GX.

-

Я в 2013 году разбирался с Bar Expansion Если Bar Expansion у Pcie устройства разрешен, то bios прочитает первые 4 байта этого бара, если там 0x55aa (вот сейчас уже не помню, может и 0xaa55), bios поймёт, что у вас действительно option rom, и bios его прочитает весь. Если же в памяти будут другие начальные байты, то bios все вычитывать не будет. Нужно убедиться, что процесс чтения Бара происходит корректно. Это вопрос к вашим разработчикам проекта для ПЛИС, пусть добавят signal tap и покажут, какие запросы приходят по pcie (должен прийти запрос на чтение Bar Expansion) и как они отвечают на эти запросы. "посмотреть в соответствующей области ОЗУ ПЭВМ" - это не то, это уже результат, а как пришли к этому результату можно понять только через signal tap. Вполне возможно, что старые процессоры читают по 32 бита за раз, а новые процессоры по 256 бит, а на такой вариант запроса у ваших разработчиков проекта для ПЛИС не корректно формируется ответ с данными. Если тут все будет в порядке, то надо читать документацию на AMD Ryzen и Intel Сascade Lake, смотреть как там устроена работа с option rom.

-

так не сработало А так сработало! Спасибо!

-

А еще вопрос. Сейчас удаленно из квартуса могу залить прошивку. В консоле jtag удаленный видится. А залить из консоли прошивку удаленно не получается C:\altera\17.1\quartus\bin64>jtagconfig.exe 1) DE5 on 193.169.11.115 [3-2] 02E660DD 10AX115H1(.|E2|ES)/10AX115H2/.. C:\altera\17.1\quartus\bin64>quartus_pgm.exe -m jtag -c 1 -o "p;E:\Work\User\projects\pr.sof" Error (213013): Programming hardware cable not detected Что не так?

-

Полное отключение фаервола на линукс машине помогло: systemctl stop firewalld Теперь буду думать какое правило надо прописать для jtadg

-

машина с Linux Centos, графического рабочего стола нет, надо иногда сигналтап смотреть, поэтому пытаюсь поднять удаленный jtag, поставил квартус программатор 17.1. Запускаю ./jtagd && ./jtagconfig --enableremote pass4 netstat -l -t -p говорит: tcp 0 0 0.0.0.0:jtag-server 0.0.0.0:* LISTEN - lsof -i :1309 ничего не говорит (хотя должен сказать, что порт 1309 открыл jtagd) ./jtagconfig --enum 1) DE5 [3-9] 02E060DD 10AT115S1 Команда hostname возвращает имя машины PC1 На другой машине в этой же сети открываю программатор, Hardware Setup -> Jtag Settings -> Add Server. В появившемся окне нужно ввести Server Name и Server Password. Какое Server Name вводить? PC1?

-

так в user space через mmap() я hugapage 1G выделил. Вообще первым шагом добавил в grub строку "hugepagesz=1g hugepages=64 default_hugepagesz=1g". После этого dmegs стал сообщать: HugeTLB: allocating 64 of page size 1 GB failed. Only allocated 13 hugepages. И в /proc/meminfo тоже написано, что HugePages есть: HugePages_Total: 13 HugePages_Free: 13 HugePages_Rsvd: 0 HugePages_Surp: 0 Hugepagesize: 1048576 kB DirectMap4k: 125296 kB DirectMap2M: 2881536 kB DirectMap1G: 13631488 kB Когда запускаю свою user программу, которая выделяет восемь hugapage 1G (физический адрес каждой страницы передается в fpga и fpga начинает по pcie последовательно записывать эти страницы данными), то в /proc/meminfo уже написано: HugePages_Total: 13 HugePages_Free: 5 HugePages_Rsvd: 0 HugePages_Surp: 0 Hugepagesize: 1048576 kB DirectMap4k: 125296 kB DirectMap2M: 2881536 kB DirectMap1G: 13631488 kB Раз в user space через mmap() я hugapage 1G выделил, то должна же быть возможность сделать тоже самое в кернел модуле...

-

u32 skp = 0x10000000; u32* kp0 = (u32*)kmalloc(skp, GFP_KERNEL | __GFP_COMP); u32* kp1 = (u32*)kmalloc(skp, GFP_KERNEL | __GFP_COMP); printk(KERN_INFO "skp = %d (0x%016llx)\n", skp, skp); printk(KERN_INFO "kp0 = %d (0x%016llx)\n", kp0, kp0); printk(KERN_INFO "kp1 = %d (0x%016llx)\n", kp1, kp1); u32 svp = 0x10000000; u32* vp0 = (u32*)vmalloc(svp); u32* vp1 = (u32*)vmalloc(svp); printk(KERN_INFO "svp = %d (0x%016llx)\n", svp, svp); printk(KERN_INFO "vp0 = %d (0x%016llx)\n", vp0, vp0); printk(KERN_INFO "vp1 = %d (0x%016llx)\n", vp1, vp1); Ага, тоже нашел этот ответ, попробовал, выдает следующее: [ 1266.791973] skp = 268435456 (0x0000000010000000) [ 1266.791975] kp0 = 0 (0x0000000000000000) [ 1266.791976] kp1 = 0 (0x0000000000000000) [ 1266.791976] svp = 268435456 (0x0000000010000000) [ 1266.798007] vp0 = 1073762304 (0xffffa4f540005000) [ 1266.830376] vp1 = 1342201856 (0xffffa4f550006000) kmalloc() вернул нул, не смог выделить 256 МБ буферы. vmalloc() смог выделить. Задействованы ли при этом hugepage в 2 МБ не знаю. Hugepage 1G не задействованы, по-прежнему свободных 13 штук. Если уменьшить размер запрашиваемого буфера, то kmalloc() и vmalloc() успешно возвращают указатели на память. Если задать размер в гигабайт (0x40000000), то система падает, уходит в ребут (из-за vmalloc(0x40000000) ) Ну продолжаю дальше искать решение

-

С CMA и dma_alloc_coherent я разобрался 4 года назад (была OpenSuse 13.2, версия ядра 3.16), и не проблема сделать это и сейчас. Но нужно задействовать именно hugepages. Это повысит эффективность работы с памятью (будет меньше обращений к TLB).

-

dma_alloc_coherent вернёт указатель на непрерывную физическую память, состоящую из восьми hugepage?

-

На машине установлен CentOS (версия ядра 3.10.0-1127.el7.x86_64). Есть необходимость выделить огромные физически непрерывные куски памяти (несколько буферов по гигабайту к примеру). В user space программе я выделил 8 hugepage 1G с помощью mmap(), код подсмотрел здесь https://github.com/max0x7ba/atomic_queue/tree/master/src До запуска программы /proc/meminfo показывает, что доступно 13 Hugepage страниц, свободно 13 Hugepage страниц. При работающей программе количество свободных страниц = 5. Записываю, читаю данные в этих страницах. Ну как бы в user space задача решена. Но руководитель проекта говорит надо в кернел модуле восемь Hugepage 1G страниц выделить, а юзерские программы уже будут обращаться к этому кернел модулю и мапить себе эти буферы. Перерыл интернет, не могу найти как выделить Hugepage 1G в кернел модуле. Пните в нужную сторону.

-

Чтение и запись на одной частоте идут или на двух?

-

года два назад на алиэкспресс покупал, самые обычные. В один рейзер x16 вставлена плата с FPGA, в другой рейзер x16 вставлена сетевая карта. Эти два рейзера соединены между собой usb кабелем. К одному из этих рейзеров припаял витую пару к pcie refclk, другой конец витой пары припаял к рейзеру x1 - этот рейзер x1 вставляю в материнскую плату компа, от него и беру опорный клок для pcie. Ниоса нет. Сначала простую стейт машину набросал, потом реализовал простенький логический блок, который берет команды из памяти (чтобы команды мог без перепрошивки менять). Вместо сетевой карты цеплял NVME SSD диск, прочитал endpoint config space, запустил nvme контроллер (CC.EN = 1), посмотрел, что взводится ответный сигнал CSTS.RDY. Пока на этом остановился. Мне думается, что этот PCIe switch все у вас и портит.

-

Да, все получилось. Соединил плату Стратикс 5 и плату сетевой карты через рейзер x8. Пробовал запитать в плис pcie корку от другой опорной тактовой частоты с платы, ничего не получалось (опорная частота должна быть с дедикейтед клок пин, должна находиться в том же регионе, что и пины линков и т.п.), поэтому в итоге припаял к райзеру витую пару (одна пара из обычного эзернет кабеля) и подал опорный клок с материнской платы. Root Complex завёлся. Прочитал root config space. Прочитал endpoint config space.

-

тогда так делать не надо У вас есть данные - адресные входы для внешней мс sdram, и есть тактирующий эти данные клок ck. С фазой ck ничего специально придумывать не надо. Нужно оценить длину дорожек от пинов плис до микросхемы SDRAM. Подставить в констрейны и квартус там сам все разрулит. Как оценить длину дорожек и в какие констрейны подставлять - надо почитать мануалы от интела. Вот в том документе есть Board Delay (Data) и Board Delay (Clock) = 0.8ns. Надо подобные констрейны наколдовать.