goodsoul

Участник-

Постов

145 -

Зарегистрирован

-

Посещение

Весь контент goodsoul

-

>>Если короче то интел/альтера выпустил аналог версаля Все-таки Versal - это ACAP. Agilex - FPGA. >>Не очень понял что они имеют ввиду под "тензорным блоком" На сайте Intel об этом написано. Если кратко - тензорный блок был представлен в S10NX. В Agilex E и D тензорный режим вкрутили в стандартный DSP блок. Т.е. помимо привычных INT и FP режимов добавился тензорный режим чтобы выдать много TOPS в INT8. Еще раз - в Versal для AI добавили отдельные ускорители, которые нужно отдельно программировать. В Agilex - это часть DSP блока. ИМХО, основная суть анoнса в том, что появились новые подсемейства Agilex/Agilex SoC в небольших емкостях, со свежими ARMами, которые производят не на TSMC, а на фабриках Intel. Это все важно в контексте спекуляций о том, что Intel сфокусирован только на больших и дорогих FPGA.

-

В последнем квартусе появился атрибут preserve_for_debug. Подробнее здесь: https://youtu.be/sEKc2ut42gU

-

Релиз Quartus Prime Pro 21.3

goodsoul опубликовал тема в Среды разработки - обсуждаем САПРы

Quartus Prime Pro 21.3 доступен для скачивания. Release Notes: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/rn/rn-qts-pro-dev-support.pdf • Improvements for Intel® Agilex™ FPGA power, performance, runtime, memory, and logic utilization†• The first release of the Nios V/m microcontroller (the next generation of softcore processors based on the open-source RISC V architecture)• New, faster compilation options for use during the early stages of development• Signal preservation for use in RTL development and Platform Designer system development• Incremental Signal Tap compilation, providing faster iterations during the debug cycle• Simulator Aware Signal Tap (Beta) expanding the scope of visibility of the Signal Tap Logic Analyzer tool• New and improved Design Assistant design rules for synthesis, clock domain crossing (CDC), reset domain crossing (RDC)• Siemens EDA Questa*-Intel FPGA and Starter Edition simulators for faster 64-bit simulation• And Many More https://blogs.intel.com/psg/intel-quartus-prime-software-verson-21-3-available-now-agilex-power-and-performance-nios-v-simulator-aware-signal-tap-and-more/ NIOS V требует $0 лицензию - ее можно сгенерировать в Self-Service Licensing Center; пока что доступен только для Q.pro NIOS II никуда не исчезает и доступен для использования. -

Давненько я в RTL не залезал, но судя по коду - это вообще не память. Это чистая комбинационка, поэтому ramstyle здесь бессилен. >>Да и к тому же матлаб везде нахваливают за его удобство и чуть ли не пару кнопок нажал и всё - код сгенерирован и можно работать. К сожалению результат нагенеренного кода не всегда оптимален для ПЛИС, особенно для конкретного сеймейства, где могут быть дополнительные заморочки связанные с конвейрезицией, ресетами и пр. Поэтому старайтесь использовать родные вендорские IP ядра или DSP builder, который знает все тонкости целевого семейства ПЛИС.

-

Если зайти на страницу для скачки Quartus Prime 19.1 std, то можно увидеть следующий текст: To use the Quartus Prime Standard Edition Design Software, Version 19.1 on Windows, you must download and install the patch available in this KDB Solution. https://www.intel.com/content/altera-www/global/en_us/index/support/support-resources/knowledge-base/tools/2020/fatal--cannot-generate-ip-in-a-windows-evironment-.html Патч ставили? Что касается NIOS II, то начиная с 19.1 Eclipse IDE нужно ставить отдельно. Что значит "не запускается"?

-

См. режим PCS Direct. В этом режиме встроенные хард PCS блоки не используются. "Enforces rules required by the PCS Direct mode. In this configuration the data flows through the PCS channel, but all the internal PCS blocks are bypassed. If required, the PCS functionality can be implemented in the FPGA fabric." https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/stratix-10/ug_stratix10_l_htile_xcvr_phy.pdf - страница 38, таблица 12 "Transceiver Configuration Rule Parameters"

-

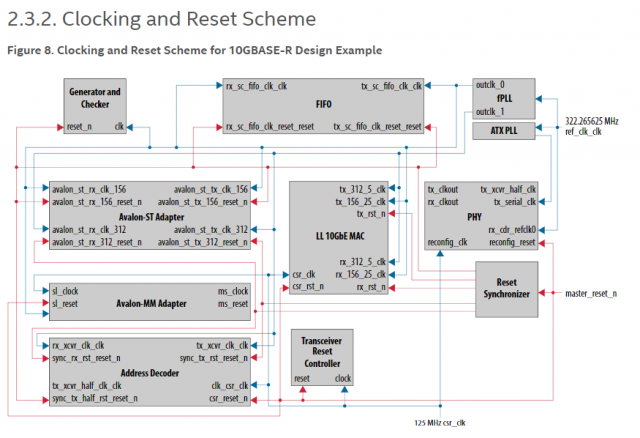

Platform designer умеет для корок готовые design examples генерировать. Посмотрите https://www.intel.com/content/www/us/en/programmable/documentation/umc1467272429805.html#nfa1448439896708 В частности, Figure 8. Clocking and Reset Scheme for 10GBASE-R Design Example

-

В концепцию FPGAaaS я не верю по следующим причинам: 1) Те, кто использует FPGA для типичных FPGA'шных задач хотят иметь локальное железо. И это будет не ускоритель типа PAC/Alveo, а скорее всего девкит или конструктор с FMC. Нужен доступ к жеелзу для испытаний, дебага и пр. Девкиты в датацентр ставить никто не будет. Они просто не сделаны для этого 2) FPGA в облаке в качестве ускорителя - утопия на данный момент. Я не могу понять зачем FPGA-ускоритель обычному юзеру. Спроса на FPGA со стороны SW девелоперов я пока не наблюдаю. Это очень нишевая платформа на данный момент. x86 и даже GPU - куда более general purpose платформы по сравнению с FPGA. Согласно информации, которая есть у меня, все FPGAaaS деплойменты не приносят прибыли и являются скорее имиджевым проектом: мол, смотрите, наши FPGA в облаке. Спрос на это ничтожно мал. Но я верю в FPGA в облачной инфраструктуре, например как часть SmatNIC для оффлоада инфраструктурных нагрузок (storage, Open Virtual Switch и т.п.). Но это совсем другая история.

-

я поставил. Даже под Agilex проект собрал.

-

100g + FPGA

goodsoul ответил Lmx2315 тема в Работаем с ПЛИС, области применения, выбор

Нужно помнить, что экспортная классификация чипов и готовых устройств (плат) на их основе отличается. По крайней мере отладочные платы на S10 в РФ нормально попадают. 100G бывает разный. CFP/CFP2/CFP4/QSFP28... с FEC и без него. Перед тем как браться за железку следует понять что вообще делать будете. В современных FPGA от Intel/Xilinx многое уже доступно в виде hard IP. Не только трансиверная часть, но и мак с феком. Плат довольно много. Вот свежая на S10: https://www.terasic.com.tw/cgi-bin/page/arc...44&PartNo=1 -

Выскажу капитанскую мысль, но тем не менее: чем меньше техпроцесс, тем больше статика. Но меньше динамика. Поэтому правильная стратегия при переходе на топовые семейства это уменьшать ресурсы (т.е. размер ПЛИС) и поднимать частоту. Например, уменьшить кол-во ресурсов в два раза и поднять частоту в два раза. Пропускная способность останется той же, но потреблять будет меньше.

-

Quartus + Matlab

goodsoul ответил svatoslav_p тема в Среды разработки - обсуждаем САПРы

Я с DSP builder'ом плотно не работал, т.к. ЦОС не моя тема. Однако знающий человек высказал следующую мысль: - Очевидно, DSP builder, как и любой другой HLD инструмент призван повысить продуктивность работы. Обратная сторона медали - конечный результат может занимать больше ресурсов. Для больших плис с сотнями тысяч LE это не особо критично. - Используя дсп билдер можно быстрее вносить изменения в проект и пробовать разные подходы и ограничения (играть с разными структурами фильтров, распараллеивать, конвейеризировать и т.п.). Можно задать целевую частоту, и тулза сама выберет подходящую структуру и глубину конвейера. - На выходе билдера вы получите проект с учетом архитектурных особенностей целевого кристалла. Включая поддержку hard floating point блоков (a10/s10) и архитектуры hyper-flex в high-end семействах (s10, falcon mesa). К примеру, если у вас есть RTL код, написанный для A10, то не факт что он хорошо ляжет на S10, т.к. архитектура разная. В случае дсп билдера нужно лишь перегенерить систему под другое семейство. -

Китайские ПЛИС

goodsoul ответил irinamiros тема в Среды разработки - обсуждаем САПРы

>>Интересуют конкретно эти модели pin2pin? Это был скорее вопрос общего плана. У нас FPGA как правило используются в спец.оборудовнии. Соответственно, будет очень обидно узнать, что фабрика в Китае просто свернула производство. -

Китайские ПЛИС

goodsoul ответил irinamiros тема в Среды разработки - обсуждаем САПРы

Это все очень круто. Но 1) ПЛИС такого уровня и так не подпадают под экспортные ограничения 2) Есть ли гарантии, что эти устройства будут производить хотя бы лет 10? -

как это видит Intel Платформа: https://www.altera.com/solutions/accelerati.../platforms.html Готовые решения: https://www.altera.com/solutions/accelerati.../solutions.html (обработка изображений/видео, базы данных, биг дата, компрессия и пр.) Программный стек:https://www.altera.com/solutions/acceleration-hub/acceleration-stack.html Свое решение можно запилить на RTL или OpenCL

-

Акселерация различных нагурзок (workloads) в датацентрах (AI, DB acceleration, genomics, finance...). Но там применяются как правило уже готовые платы сертифицированные и валидированные для серверного использования. Т.е. FPGA можно рассматривать как альтернативу GPU для многих задач.

-

Если я правильно понял задачу, то VHDL: -- synthesis translate_off -- synthesis translate_on должно помочь. Указывает синтезатору квартуса игнорить кусок кода. Оно?

-

Специально проверил: у меня на Win10 ничего не делающий Qpro 17.1 отжирает 0% CPU. Да и 17.0 не припомню чтобы так себя вёл.

-

>>Заменит Verilog или будет как дополнение к разработке? HLS позиционируется как дополнительный инструмент разработки для RTL-дизайнера (в отличие от OpenCL SDK, который для software developers) Основной профит: 1) Ускорение функциональной симуляции (C/C++ код можно отсимулировать гораздо быстрее) 2) Ускорение разработки IP-ядер. Сишные функции конвертируются в IP-ядра со стандартным интерфейсом (Avalon), которые затем можно в QSys интегрировать. DSP, обработка видео и т.п. вещи неплохо ложатся. На счет реализации control logic, конечных автоматов и пр. я не уверен

-

Релиз Intel Quartus Prime 17.1

goodsoul опубликовал тема в Среды разработки - обсуждаем САПРы

Состоялся релиз Intel Quartus Prime 17.1: https://www.altera.com/products/design-soft...what-s-new.html Поддержка семейств в Standard Edition: MAX II-V-10, Cyclone IV-V-10LP, Arria II-V-10, Stratix IV-V Поддержка семейств в PRO Edition: Cyclone 10 GX, Arria 10, Stratix 10 (включая Stratix 10 MX со встроенным HBM2) Улучшена поддержка Cyclone 10LP/GX (больше IP ядер) HLS (High Level Synthesis) - бесплатно https://www.altera.com/products/design-soft...r/overview.html OpenCL SDK for FPGAs - теперь тоже бесплатно https://www.altera.com/products/design-soft...l/overview.html Конф память: Поддержка EPCQ-A: https://www.altera.com/content/dam/altera-w...re/an/an822.pdf Новые туториалы на youtube канале: https://www.youtube.com/user/alteracorp/videos -

Путь в пропасть - не размещать заказ за 3-6 месяцев до начала производства. >> не покупать с каталогов из принципа, а только у местных официалов Дело не в принципе, а в стоимости. В каталогах все в 2-4 раза дороже. Каталоги себя оправдывают только на мелкосерийке (где и упаковки не наберется) или прототипах. Хотел бы я посмотреть как какую-нибудь РЛС с каталога укомплектуют.

-

Мой опус был не про каталоги (digikey, mouser и пр) и склады, а про channel. Так что можете отнести его к другой реальности - в моей реальности с каталогов вообще никто не покупает.

-

В соседней теме я изложил свое видение проблемы: https://electronix.ru/forum/index.php?showt...43243&st=15 Там все гораздо проще. Особых отличий не вижу. Есть комбинация быстродействия (быстрый/средний/медленный) + температурный грейд. В рамках одного корпуса все взаимозаменяемо. На самом деле нет. Там конечно разбавили Альтеру интеловским народом, но в целом штат разработчиков увеличен, т.к. интелу FPGA нужны. >>пустые pdf-ники даташитов со ссылками на сайт и т.д. связано с постоянным обновлением сайта, но вроде оперативно фиксят. А так да, "under maintenance" частенько можно увидеть. По тех процессу Интел тем не менее все еще впереди на пару-тройку лет (я не про маркетинговые нанометры, а по реальным физ.характеристикам). В серверном сегменте он доминирует с долей >90%, так что если будет реализована стратегия дооснащения всех датацентров плисами (как в дискретном исполнении, так и в составе Xeon'ов), то долю ксая можно будет рассматривать под микроскопом. Если говорить про 20nm, то согласно бенчмаркам Arria 10 поинтересней будет: https://www.altera.com/content/dam/altera-w...and-results.pdf (upd: согласен, к бенчмаркам стоит подходить аккуратно, т.к. каждый производитель постарается их под себя "заточить") Ксай делает свое дело хорошо, но архитектурно мало что меняет. Альтера хоть hard float-point добавила, архитектуру обновила (hyperflex). Я слышал, что ксай вынужден будет пойти по тому же пути и делать свой hyperflex (скоро узнаем). >>ИМХО, продажа Интелу это уже следствие архитектурных ошибок Альтеры На самом деле вот настоящая причина: https://www.top500.org/news/microsoft-takes...the-next-level/ В общем я предлагаю не смешивать технологию/корпорации с локальными проблемами в РФ (санкции, доставаемость и т.п) - это процессы совершенно разного уровня. На глобальном уровне что Ксай, что Интел продолжают делать свое дело и очень скоро будут аносированы next-gen продукты что у одних, что у других. Все будут биться за датацентровый сегмент, AI и пр. Конкуренция не отменяется, и это хорошо. То, что происходит на локальном уровне в РФ зависит от адекватности и компетентности канала продажи (дистрибов). Более того, я буду вынужден многих огорчить, но объем FPGA-сегмента в РФ (всех производителей вместе) настолько ничтожен, что если перед Интелом/Ксаем встанет дилемма - закрыть продажи в РФ полностью, либо хапнуть проблем с дядей Сэмом, то они без раздумий выберут первый вариант. Нужно отдавать себе отчет, что отношения между РФ и США находятся, мягко говоря, в натянутом состоянии. И закладывая "вражеские" микросхемы нужно подумать на 10 шагов вперед - какой парт, как достать, как легендировать, лицензия или нет и пр. Уже не работает схема "на отъ**ись" как раньше - мы заложим, а дальше как-нибудь привезем. Прошли те времена. И самое важное - всех нужно контролировать, т.к. на каждом шагу тотальная некомпетентность. Зачастую менеджеры по продажам вообще понятия не имеют, что они продают. Многим до фонаря, телефонами в ларьке торговать или контролируемой на экспорт технологией. Они могут наобещать, а потом выясниться что или заказ забыли разместить, или лицензию даже не начали офорлмять, или даже не понимают как отличить лицензируемый парт от нелецинзируемого и т.п. Озаботьтесь грамотной легендой, скооперируйтесь заранее с "белым и пушистым" прикрытием и используйте конкретно тот парт, который уже ввозится - это самый простой вариант

-

Идем сюда: https://www.altera.com/support/support-reso...vices/eccn.html Вбиваем партномер: 5AGXMA5G6F35C6N Вылезает ECCN код 3A991, что подразумевает отсутствие необходимости оформления экспортной лицензии. Можно тыкать дистрибьюторов туда лицом и требовать объяснений. В этом случае я вижу банальную некомпетентность менеджера дистриба или закупщика (или то и другое). Приобретение Альтеры Интелом здесь вообще не при чем.

-

a) Ориентируйтесь на Cyclone IV, Cyclone V, MAX10, Cyclone 10 LP б) Если опыта мало - не связывайтесь с noname платами с ali. Огребете проблем с качеством, документацией, примерами и поддержкой. Лучше немного переплатить, но получить нормальный продукт. Терасик или что-то вроде этого: http://maximator-fpga.org/ в) Если не ошибаюсь, то версия "e" бесплатная. См. здесь: https://www.altera.com/products/processors/overview.html г) NIOS II синтезируемый процессор, поэтому ему нужны ALM и память. Примерные resource utilization: https://www.altera.com/en_US/pdfs/literatur..._nios2_perf.pdf (см. table 3)