-

Постов

4 590 -

Зарегистрирован

Весь контент fill

-

Выложите конкретный пример, иначе абсолютно не понятно. MVO ставите в Plane_Shape. Тянуть трассу к MVO не хотите. Каким образом тогда пины соединяются с MVO? Если пины принадлежат той же цепи что и Plane_Shape, то зачем вообще MVO, если для сшивки Plane_Shape с плейн на другом слое можно разместить просто массив переходов Via_Array или сшить через Stitch_Shape.

-

Т.е. ширина трасс и количество переходных никак не взаимосвязаны?

-

Setup>Advanced_Setup>Multiple_Via_Objects - конфигурируете правила ширина трассы-тип_MVO и к каким классам\цепям применить. После этого MVO сами будут появляться при проводке трасс данных цепей, с данной шириной. Так в чем проблема то?

-

Не совсем понял вопроса. Но можно например запустить Add_Via и затем, когда via на курсоре нажать ПКМ>Change_MVO_Pattern>... и выбрать нужный MVO

-

xDM Design

fill ответил Zuse тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

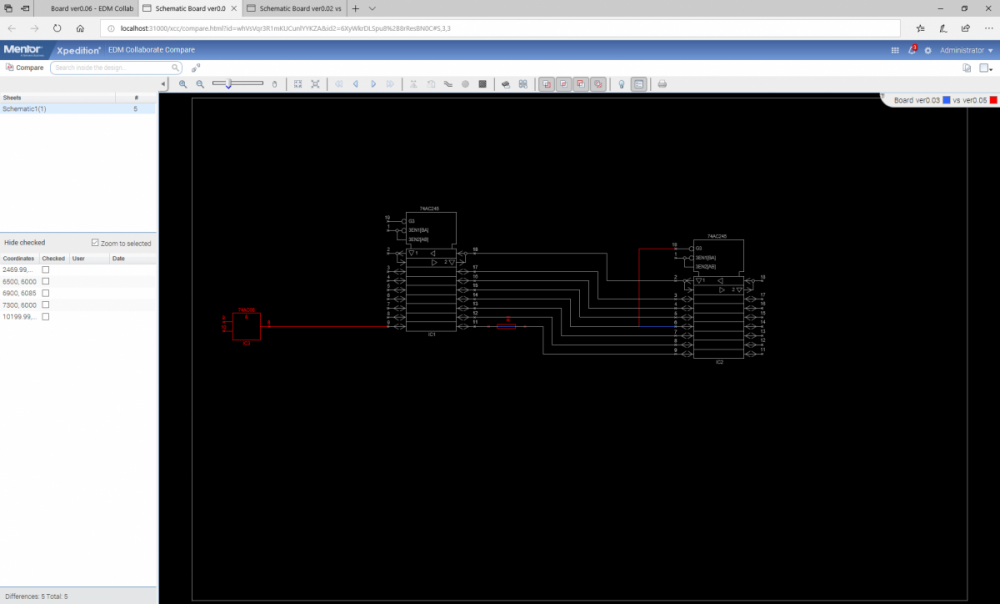

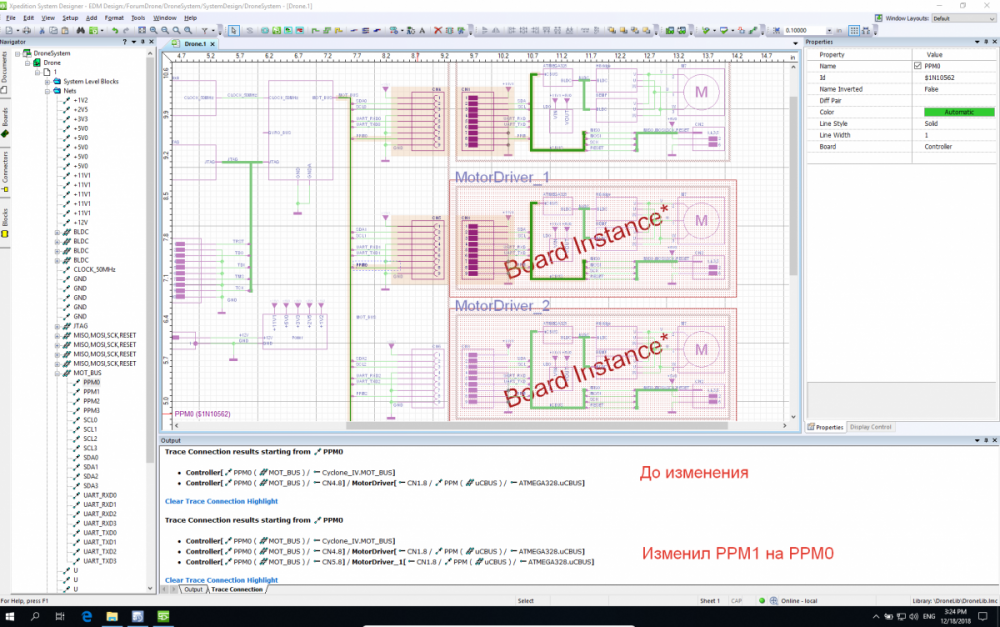

1. В окне Version List можно выбрать нужную версию и открыть в соответствующем редакторе. Соответственно если далее сделать check in, то данные этой версии снова станут последними\текущими. Есть также команда Prune для удаления не нужных версий или Freeze чтобы наоборот не перетёрлась данная версия. 2. А смысл вообще делать пространные описания если можно быстро запустить сравнение между любыми версиями и увидеть различия, в том числе и графически как в топологии, так и в схеме. Простейший пример, версия 3 и 5: -

-

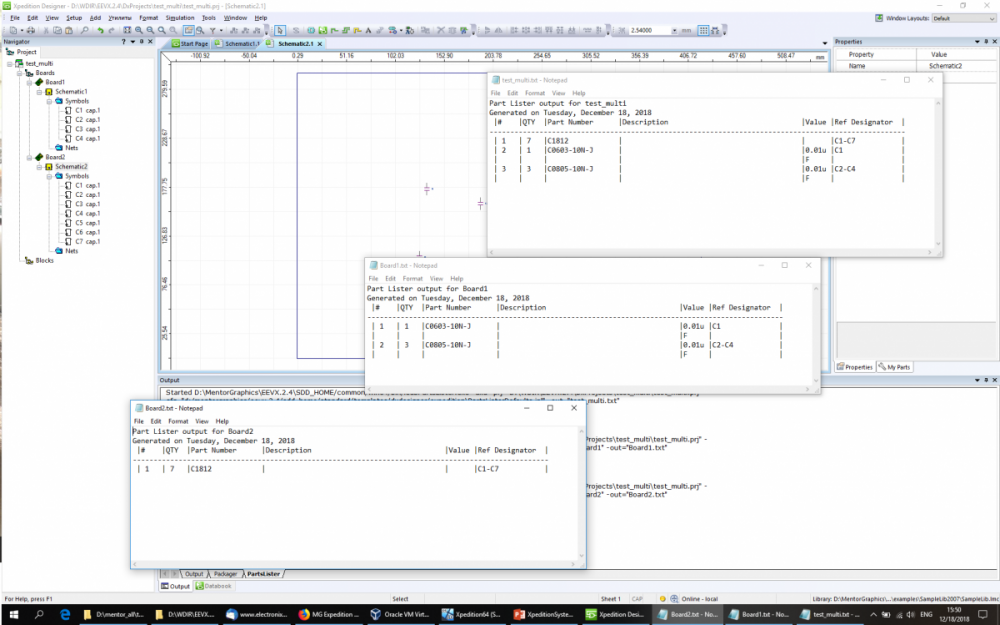

1. В каждой board своя схема со своей нумерацией и связана со cвоей pcb. Естественно в схемах разных board порядковые номера могут повторятся. 2. Надо ставить EDM Design.

-

Да. Два варианта: 1. Просто внутри схемного редактора в навигаторе добавить еще одну board. 2. Использовать System Designer - более продвинутый вариант много-платного проекта, с отслеживанием перераспределения компонентов по платам, разъемов\кабелей и т.д.

-

Скорее всего просто у вас оба проекта указывают на один и тот же файл borders.ini

-

Grop Outline

fill ответил Roman53 тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Я заметил что формирование групповых линий зависит и от последовательности извлечения компонентов. Например у правой верхней группы, групповая линия есть только на Bottom, не смотря на то что некоторые компоненты я в последствии переместил на Top. -

Grop Outline

fill ответил Roman53 тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Вот пример из Tutorial, который есть у всех. Сделал push нескольких групп - цвет их поменялся на синий. При выключении переключателей Plaining Groups, исчезает изображение и соответствующих групп. После извлечения компонентов работает переключатель Group Outline. Заметьте, у правой верхней группы групповая линия исчезла совсем. У левой нижней группы есть две линии, т.к. компоненты расположены на обеих сторонах платы, соответственно отображение линии Top осталось. -

Презентация

-

Вопрос по HyperLynx

fill ответил _sda тема в Разрабатываем ПП в САПР - PCB development

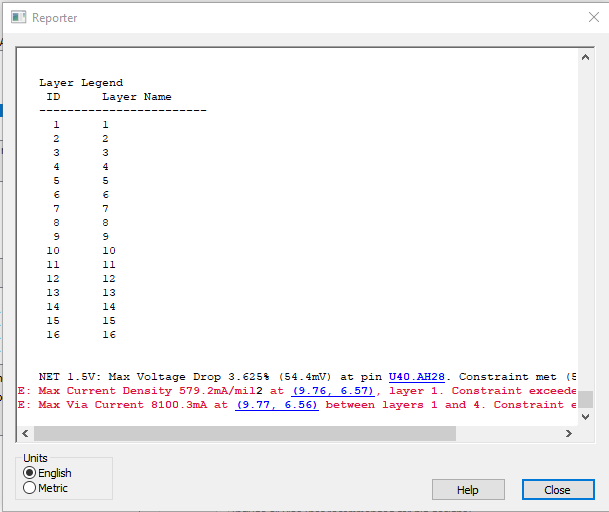

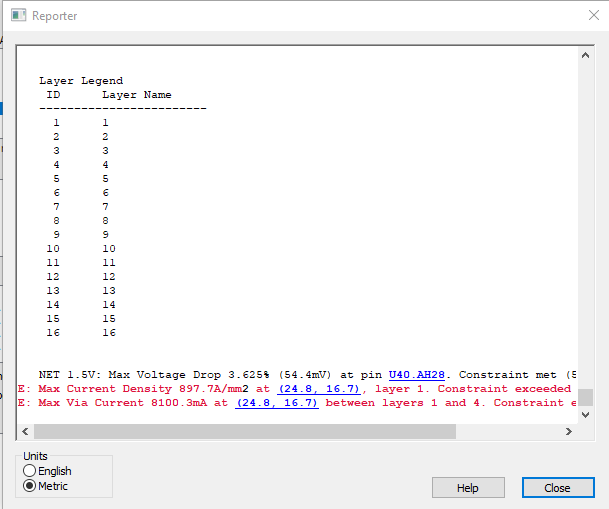

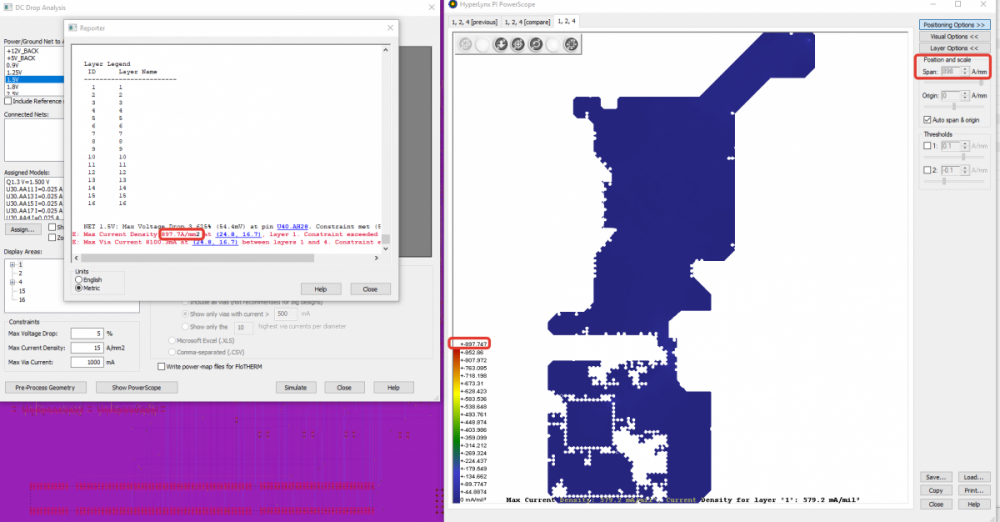

Суть в том что разбираться с тем что было 2 года назад никто не будет. Насколько я вижу, проблема в том что в PowerScope не меняется отображение в соответствии с единицами измерения (всегда отображает mA/mill2), хотя сами результаты в отчетах меняются в соответствии с изменением единиц. В отчете это видно: При этом внизу экрана всегда отображается максимальное значение в mA/mil2. И интерактивные графические данные плотности тока идут в mA/mil2. SR создал. Надеюсь что исправят быстро. Сравнил результаты в mA/mil2 между релизами - разница ~2%. -

Я вижу что на таких компонентах, при их выборе, в статусной строке сразу написано NO Pushable. Т.е. откуда то пришел такой признак. Надо разбираться в последовательности операций приводящих к такому результату.

-

Вопрос по HyperLynx

fill ответил _sda тема в Разрабатываем ПП в САПР - PCB development

9.4.2 вышла 2 года назад. Текущая версия VX2.4_Update1 -

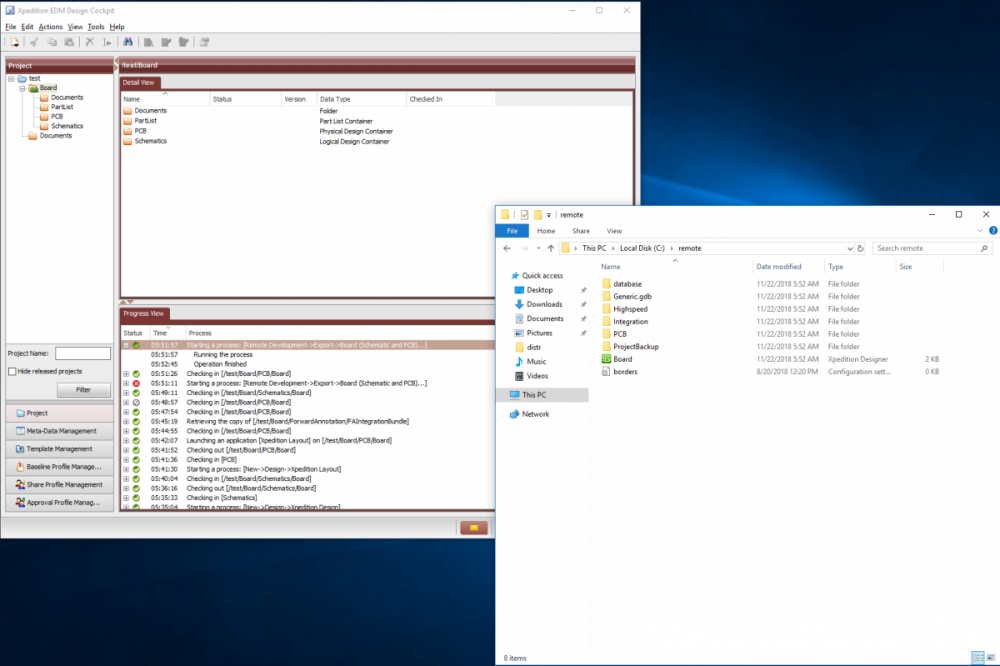

Я у себя проблему не вижу. Создал проект. Схема. Прямая Аннотация. Топология. Check in обеих. Выдал в папку remote. В первый раз, можете заметить была ошибка - не сделал cheсk in топологии.

-

Проект в студию - мало ли чего там может быть. Мы не экстрасенсы.

-

Достаточно установить Editir_Control>Place> Online 2D Placement DRC в Warning

-

Насколько я понимаю, система считает что проект не синхронизирован, т.е. не выполнены аннотации.

-

Ваши данные сильно устарели, уже несколько лет как используются другие солверы (от Nimbic), хотя часть задач (для антенн) решается и через IE3D.

-

Вы все время говорите только о HL SI\PI. А в линейке HL есть еще Hyperlynx Full Solver, HyperLynx Fast Solver, HyperLynx DRC... Если говорите о DDR Wizard, то помимо HTML отчета там есть еще и графики (полученные в результате реального моделирования), по которым собственно отчет и формировался. Кроме того вы себе сами противоречите - с одной стороны говорите что " предпочитаю разбираться досконально во всём сам " с другой стороны безоговорочно доверяете тому что подобрал вам софт в качестве решения по конденсаторам развязки, при том что выбор он провел из линейки всего одного производителя и что параметров оптимизации может быть много. Например в видео показан пример как даже для одного типа анализа развязки можно получить разные результаты в зависимости будем ли мы рассматривать отдельные пины питания или будем их рассматривать как группу.

-

1. Умеет. 2. Пакетные проверки позволяют существенно сократить время разработки, т.к. нет необходимости моделировать то, что уже ранее было промоделировано и нужно просто проверить есть ли подобные проблемные места в новом проекте. Проверку может запустить любой человек, даже не понимающий тонкостей приготовления моделирования и анализа полученных результатов - задача быстро найти проблемные места и устранить их самостоятельно или передать эти данные для разборки специалисту.

-

Для контроля версий есть EDM Design, о функциях которого вы видимо даже не слышали. Кроме Hyperlynx SI\PI есть еще HyperLynx Advanced Solvers с точно таким же функционалом как у Sigrity. Sigrity может провести автоматическую верификацию SERDES каналов на предмет выполнения нормативов конкретного стандарта передачи данных? А в HL SI\PI уже поддерживается несколько десятков протоколов. Может быть Sigrity может провести быструю проверку всей платы и найти в ней за несколько минут нарушения связанные с ЦС\ЦП\ЭМИ? А в HL DRC есть уже 63 типа проверок. Назовите в чем конкретно Sigrity обходит по функционалу линейку продуктов HyperLynx. А для начала обновите свои знания. Прочтите например из последнего