avarte

Свой-

Постов

78 -

Зарегистрирован

-

Посещение

Весь контент avarte

-

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

Вы всегда на буферах прописываете? кстати попробовал на самих входа/выходах прописывать, работает и предупреждений меньше вылазит, только что отобразить нельзя чтобы на схеме видно было. -

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

спасибо, про 2клик не знал вопрос по подобной проблеме задан на “форум.хилинх.сом” однако и там ответа не было однако же, это баг? -

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

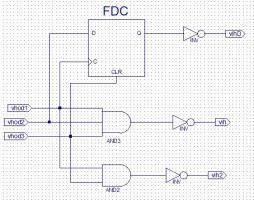

т.е. вы предполагаете что PACE косячит? может попробуете загрузить файлы с первого поста и попробовать, потому что у меня не работает самое интересное что если на VHDL написать элемент D-тригера то все хорошо, но необходимо использовать именно стандартные элементы и рисовать в схемном редакторе. в ISE 13.3 тоже самое, скорее всего я где то, чего-то не учел и не выбрал вот только понять не могу где -

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

программа не принимает такой вариант -

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

iosifk спасибо за замечание, однако это не решает вставшую проблему буферы тоже её не решают вопрос остается открытым -

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

замечания на отсутствие буферов выдается, но я пока не заморачиваюсь, т.к. проект не окончательный а она и без буферов работает, вот только если буферы могут мою ошибку исправить, ща попробую -

непонятные ошибки

avarte ответил avarte тема в Среды разработки - обсуждаем САПРы

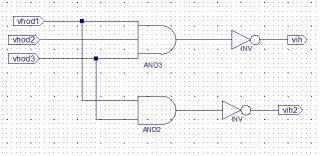

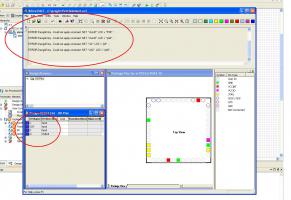

не ответили мне и правильно сделали, я бы тоже не отвечал на белиберду, просто писал вечером уже весь в мыле. более подробное описание проблемы в программе ICE 14.4 для плис XC9574xl vq44 10c создается вот такой проект после чего запускается Xilinx PACE и я вижу все свои входы и выходы проекта, нормально их расставляю потом дорисовываю D-триггер в соответствующем виде и после запуска Xilinx PACE, вижу что те выходы, которые были проставленные на предыдущим шаге, стали ОШИБКАМИ, и программа предлагает расставить выходы только D-тригера, а не проекта целиком прошу указать на мои ошибки, и натолкнуть на мысль что я делаю неправильно сам проект загружен в первом посте. -

непонятные ошибки

avarte опубликовал тема в Среды разработки - обсуждаем САПРы

xc9572xl vq44 10c проектирую в ISE 14.4 суть проблемы в том что в проекте есть 3 входа и 3 выхода при попытке запустить “подключение к ножкам” имеем не выходы проекта и выходы элемента D-тригер, если удалить Dтригер то все нормально и I/O проекта нормально подключаются к ножкам и прошивается. возможно что что-то просто упускаю, т.к. давно не занимался плисами и вот реши вспомнить, прошу помощи. rt1.rar -

после предварительной регистрации приходит письмо с сообщением что дата проведения вебинара 18 февраля 2013 г. в 17:00 (мск)

-

Как использовать ноги глобальных сигналов как вход/выход и как использовать как глобальные ? так понимаю, чтобы использовать как просто вход/выход нужно в проекте подцепить на них STD_LOGIC-овские линии, а как использовать их как глобальные????

-

Цветовая маркировка р/элементов

avarte опубликовал тема в В помощь начинающему

Вот ТУТ можно ознакомится с большим числом графического материала по заявленой в названии темы теме. -

Вот я лохонулся Как тему закрыть?

-

регистрация Xilinx ISE 9.2i ?

avarte опубликовал тема в Среды разработки - обсуждаем САПРы

скачал серийник с ФТП, а прога не хочет его принимать, или может я его не туда вписывал? -

спасибо за идею вот что у меня получилось

-

почему не работает j:= i rem 12; ?

avarte опубликовал тема в Языки проектирования на ПЛИС (FPGA)

должен быть генератор выдающий последовательность 204 байта В8,2,3,4,5,6,7,8,9,10,11,12,1,2,3,4,5,6,7,8,910,11,12,1,2,3,4,5,6,7,8,9,10,11,12 ,1,2,3 ...и.т.д. до конца посылки в 204 байта но вот незадача ISE выдает ошибку на строке "j:= i rem 12;" с пояснением "ERROR:Xst:769 - "D:/xilinx_diplom/svert_peremej_3/generator.vhd" line 26: Operator <REMAINDER> must have constant operands or first operand must be power of 2" вот собственно код library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity generator is Port ( clk : in STD_LOGIC; potok : out STD_LOGIC_vector (7 downto 0); sinxro : out STD_LOGIC ); end generator; architecture Behavioral of generator is begin generator: process(clk) variable i: integer range 1 to 204; -- 408 variable j: integer range 1 to 12; begin if(clk'event and clk='1') then -- выставление сигнала на фронте импульса case i is -- формирование выходного сигнала when 1 => potok <=x"b8"; --B8 when others => j:= i rem 12; potok <= conv_std_logic_vector(j,8); end case; case i is -- формирование синхро импульса when 1 => sinxro <='1'; when others => sinxro <='0'; end case; i:=i + 1; end if; end process generator; end Behavioral; подскажите в чем я ошибаюсь -

это часть кодера Рида-Соломона в общем это будет цикл для расчета значений в полях Галуа

-

собственно это был не мой алгоритм, поэтому и возник вопрос. А про 9 разрядов тоже правильно, а 9 и взял мой алгоритм такой rso16:=(rso+ X"0078"); if(rso16 >= X"00FF")then rso1:=(rso+ X"78")-X"FF"; else rso1:=(rso+ X"78"); end if; и ведь точно спасибо а все таки тот “+1” нужен или как у меня -X"FF" ?

-

реализация на VHDL алгоритма

avarte опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Нужно реализовать rso1 = (rso + 7816 ) mod 25510. имею: Variable rso,rso1: STD_LOGIC_VECTOR(7 downto 0); Variable rso16:STD_LOGIC_VECTOR(15 downto 0); и собственно вот такой алгоритм rso16:=(rso+ X"0078"); if(rso16 > X"00FF")then rso1:=(rso+ X"78")+1; else rso1:=(rso+ X"78"); end if; не пойму логику Зачем если число и так больше 255 к нему еще добавлять единицу? -

кстати ДА, спасибо за идею

-

Уважаемые форумчане, с этим алгоритмом я разобрался, теперь встала противоположная задача написать на VHDL: из параллельного 8-и битного потока сделать последовательный, интересно тут что нибудь подобное обсуждалось, чето поиск не рулит.

-

Дабы не плодить споров по поводу логики выкладываю схему задача в последовательном потоке искать 8-и битное слово как сделать элемент ”И” я знаю вводная та-же, а до сложения вот что получилось entity skrembler_priemnic is Port ( clk : in STD_LOGIC; potok_mp2 : in STD_LOGIC; potok_skr : out STD_LOGIC; potok_paral : out STD_LOGIC_vector (7 downto 0) ); end skrembler_priemnic; architecture Behavioral of skrembler_priemnic is begin process(clk) -- сдвиговый регистр signal count: std_logic_vector(8 downto 0); begin if(clk'event and clk='1') then count <= count (7 downto 0) & potok_mp2; potok_paral <= count(7 downto 0); potok_skr <= count(8); end if; end process; end Behavioral;

-

Спасибо ДРУГИ! если я использую сигнал вместо переменной то, на сколько я понимаю, не будет разницы как писать count <= count (6 downto 0) & potok; potok_paral <= count; или potok_paral <= count; count <= count (6 downto 0) & potok; правильно? логика при этом останется одинаковая.

-

все понятно

-

Я просто раньше AVR занимался, а тут понадобилось изучить XILINX А то что новичков не убавляется, дак это ИМХО только радоваться надо.

-

сам-бы хотел, а то все кусками из интернета поначитался, а в магазинах у нас такой литературы почти нету да и ту привозят одну две позиции