hitch

Участник-

Постов

29 -

Зарегистрирован

-

Посещение

Весь контент hitch

-

library ieee; use ieee.std_logic_1164.all; entity multiplexer is port( sel : in std_logic; in1 : in std_logic; in2 : in std_logic; out1 : out std_logic; out2 : out std_logic; out3 : out std_logic; out4 : out std_logic; out5 : out std_logic ); end multiplexer; architecture rtl of multiplexer is function mux(sel, in1, in2 : std_logic) return std_logic is type pattern is array (0 to 3) of std_logic; type truth_table_t is array (natural range <>) of pattern; constant truth_table : truth_table_t := -- sel in1 in2 out (('0', '0', '0', '0'), ('0', '0', '1', '0'), ('0', '1', '0', '1'), ('0', '1', '1', '1'), ('1', '0', '0', '0'), ('1', '0', '1', '1'), ('1', '1', '0', '0'), ('1', '1', '1', '1')); variable m : std_logic; begin for i in truth_table'range loop --if truth_table(i)(0 to 2) = (sel & in1 & in2) then if (sel & in1 & in2) = truth_table(i)(0 to 2) then m := truth_table(i)(3); end if; end loop; return m; end mux; begin mux1: process(sel, in1, in2) begin case sel is when '0' => out1 <= in1; -- Вариант 1 when others => out1 <= in2; -- Вариант 2 --when '1' => out1 <= in2; --when others => null; end case; end process; mux2: process(sel, in1, in2) begin if sel = '0' then out2 <= in1; -- Вариант 1 else out2 <= in2; -- Вариант 2 --elsif sel = '1' then --out2 <= in2; --else --out2 <= in2; end if; end process; mux3: with sel select out3 <= in1 when '0', -- Вариант 1 in2 when others; -- Вариант 2 --in2 when '1', --unaffected when others; mux4: out4 <= in1 when sel = '0' else -- Вариант 1 in2; -- Вариант 2 --in2 when sel = '1' else --unaffected; mux5: out5 <= mux(sel, in1, in2); end architecture; Авторский эксперимент с различными описаниями мультиплексора. Синтезируется в один ЛЭ, хотя выходов 5. Следовательно описания полностью идентичны.

-

Литература по VHDL

hitch ответил AntonB тема в Языки проектирования на ПЛИС (FPGA)

Ashenden P.J., Lewis J. - VHDL-2008. Just the New Stuff. 2008 -

Подтверждаю! Без спец. ПО вообще не заработает прошивка из Квартуса. Удивлён... Думал сначала, что у вас прошивка после спец. ПО не шьётся... Вот выдержка из документации: 3 Загрузка конфигурационных данных из JAM STAPL Загрузка конфигурационных данных в целевую ПЛИС по порту JTAG может быть осуществлена с помощью «Quartus II Jam Tools» (исполняемый файл quartus_jli), входящего в состав Quartus. (https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/an/an425.pdf)

-

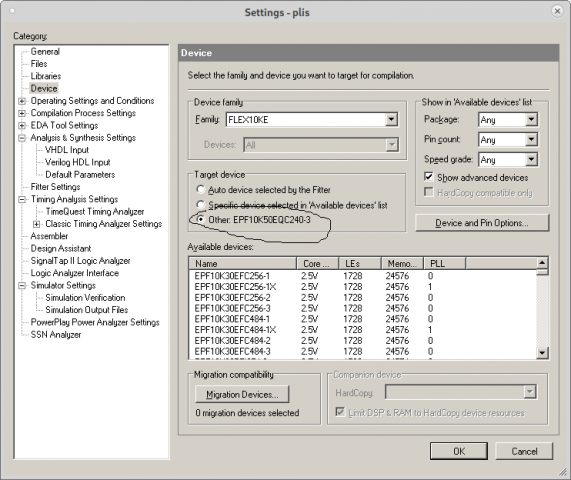

При создании проекта брал её, потом после закрытия Квартуса отредактировал указанный файл, а потом в Квартусе проверил, что стало вот как... ПЛИС напрямую даже не пробовал конфигурировать, только через ПЗУ. В программаторе Квартуса, чтобы он не ругался на неизвестное устройство выбирал EPF10K50SQ240 - длина регистра у них одинаковая. Вообще мне кажется я где-то читал, что эту ПЛИС можно напрямую прошить только через JAM-player, но никак через sof-файл. Попробуйте указать в настройках проекта формирование jam-файла и через плейер прошить, если конечно вариант через ПЗУ совсем не подходит.

-

У меня Quartus II v9.0 SP2 и в списке тоже нет требуемой м/с EPF10K50EQC240-3. Однако я отредактировал файл qsf с настройками проекта в следующей строчке set_global_assignment -name DEVICE "EPF10K50EQC240-3" и САПР при компиляции был совсем не против сгенерить прошивку и для ХС6.

-

pof-файл из квартуса 9.0 сразу готов к прошивке в РС1У.

-

- SCR1 система команд RV32I|E[MC] от компании Syntacore - Freedom E310 RV32(I/E)MC от компании SiFive, кроме того его под себя адаптировали Microsemi тут - E203 RV32IMAC от китайской компании Silicon Integrated - uRV RV32IMC от CERN - проект pulp от Цюрихского и Болонского гос. универов, но там возможно слишком много периферии для вас. Есть ещё более 10 открытых проектов, но они либо не 32 с компактным набором инструкций, либо не развиваются.

-

Иван Покровский наверное читает наш форум, раз выложил у себя на сайте основные материалы конференции. За это ему большое спасибо! :)

-

Scala (и библиотека Chisel) людям потребовалась на этапе создания полностью конфигурируемых моделей. После правки одного конфиг. файла можно получить как 32, так и 64 битный проц. Кроме того, на выходе не только синтезабельный верилог, но и высокоточная модель на Си, которая моделируется в разы быстрее. Конечно scala может сгенерировать код менее оптимальный, чем мы с вами напишем сразу на верилоге,. За это такой подход и ругают. Однако скорость разработки увеличилась в 10-100 раз. Даже в библиотеке корок Microsemi лежит ядро от Sifive, которое сгенерено из Скалы. Такой верилог в дальнейшем практичеки не возможно изменить под себя, но это требование к нему и не выставлялось

-

Как и обещали организаторы заморской конференции, они выложили в открытый доступ все материалы. Жаль, что наши же соотечественники стали брать деньги не только за участие в своём мероприятии, но и за материалы.

-

Спасибо! Из раздатки что-нибудь стоящее было? Реклама говорила, что будут ещё миландровцы и "все все все"... Такая реклама. Кстати, у нас ещё этим делом интересуются в бауманке, Микроне, НИИСИ РАН и НПО А, так что направление врят ли захиреет, как OpenRISC.

-

Кто был на мероприятии RISC V Developers Forum поделитесь пожалуйста впечатлениями, а ещё лучше материалами :) З.Ы. Информация для размышления... В конце ноября прошло другое знаковое событие, так его организаторы в течении близжайших недель предоставят все материалы совершенно бесплатно. З.З.Ы Хорошо, что унас подобный форум вообще состоялся. Спасибо организаторам!

-

Судя по схеме у вас точно в цепочке одна микросхема и другой выбирать принудительно не надо. Возможно вы ошибочно выбрали не ту ПЗУ, например EPC2 вместо EPC4. Кроме того ошибка может быть при создании файла pof - в настройках проекта нужно проверить указанный тип ПЗУ. А вообще вот что про поддержку в программаторе квартуса готоворит производитель - так может быть лучше весь проект пределать в квартусе, а не конвертировать прошивку?

-

Если прибор работает "на столе" и с небольшим разбросом температуры, то ХС1 уверенно конфигурируется на 20 МГц. На температуре могут быть нюансы. Там, где важна скорость инициализации можно и закрыть глаза на Д4 проведя дополнительные испытания. (Это практически дославный ответ-совет спеца из ВЗПП, к которому мы придерживаемся).

-

ГК81 на 20 МГц. У ХС1 есть ограничение на частоту конфигурирования, меньшее, чем у ХС4 и РС1. И скорее всего при переходном процессе генератор перепрыгивал на большую частоту, поэтому и могли быть зависания.

-

5576РС1 + 5576ХС1. Оба случая с 2 мс. Во-втором случае процесс не перезапускается, потому что в какой-то из этих микросхем зависает автомат. В какой конкретно не особенно-то и важно, замены им нет. Поэтому задержку добавляли порядка 3-5 мс и всё заработало.

-

Проблема была с временем готовности (стабильностью характеристик) источника питания и особенно тактового генератора. В первом случае процесс конфигурирования может быть перезапущен многократно, а во втором случае и вовсе "зависнуть". Микросхема очень чувствительна к частоте и скважности такта. На время переходного процесса при включении один прибор лечили двумя инверторами и RC-цепочкой в цепи nINIT_CONF, тем самым задерживая искуственно начало конфигурирования.

-

Ещё 2 источника полностью отвечающие на вопрос о связи между резервированием и увеличением надёжности в аппаратуре: Dubrova E. - Fault-Tolerant Design (Springer-Verlag New York). 2013 - раздел 4.2.2 N-Modular Redundancy и диаграмма 4.10. Фёдоров Ю.Н. - Основы построения АСУТП взрывоопасных производств. Том 1. Методология (Синтег). 2006 - раздел 4.

-

Многие наиболее востребованные ядра у производителей открыты при платной подписке. Не так ли? Если оно узкоспециализированно, вывешивают отдельный ценник и его закрывают, чтобы у покупателя естественным образом не возникло желание делиться этим ядром. И тут возникает парадокс с новым типом произведений искусства, коим ПО и является, с картины можно делать репродукции и даже оригиналы дарить друзьям, а ПО нет... Нужно выставлять адекватные цены и продавать серийно, а не заламывать баснословные цены в предположении, что украдут. Мне кажется, Иосиф Григорьевич, вы на стороне производителей, раз предположили, что автор сразу же начнёт наживаться на чужом ядре, а не захочет в первую очередь его оптимизировать под себя. Да и с трудами Ричарда Столмана наверное не согласны :)

-

При всём уважении к вам, считаю замечание не логичным. Выдать ядро мирового бренда за своё практически невозможно - мало переименовать автора и сигналы, нужно ещё перестроить спецификации, что сравнимо с новой разработкой. А вот заплатив несколько тысяч за годовую/пожизненную лицензию на САПР пользователь в большинстве своём получает полный доступ ко многим ядрам - факт. Это практикуется всеми производителями. И это правильно, потому что ПО не должно быть услугой (в идеале), оно сколь угодно тиражируемо и следовательно при массовом использовании его стоимость должна стремиться к нулю. К тому же сам производитель заинтересован открывать код ядер. Это помогает выявлять многие ошибки силами официальных пользователей. Да и пользователи охотнее применяют такие ядра, так как могут легче с ними разобраться и при необходимости модернизировать. Для автора. Судя по 5 стр. документа ядро поставляется исключительно в виде закодированного RTL и не под все семейства. Следовательно, вы врятли сможете купить его исходное описание.

-

Не совсем уверен в цифрах, но кажется вы правы. Была где-то логарифмическая характеристика надёжности от количества каналов. При количестве каналов больше 3-4 существенного прироста уже не происходит из-за пропорционального увеличения количества элементов, которое в свою очередь, уменьшает надёжность.

-

На родном языке: Коваленко А.Е., Гула В.В. - Отказоустойчивые микропроцессорные системы. 1986 Пашковский Г.С. - Задачи оптимального обнаружения и поиска отказов в РЭА (Радио и связь, Надёжность и качество). 1981 Синтез сложных многофункциональных отказоустойчивых систем электроники. А. А. Авакян, В. В. Клюев (Спектр). 2014 Согомонян Е.С., Слабаков Е. В. - Самопроверяемые устройства и отказоустойчивые системы (Радио и связь). 1989 Бортовые системы управления космическими аппаратами: Учебное пособие. Под ред. А.С. Сырова (МАИ-ПРИНТ). 2010 Проектирование и испытание бортовых систем управления. Учебное пособие. Под ред. А.С. Сырова (МАИ-ПРИНТ). 2011 На английском: http://libgen.io/search.php?req=fault+tole...&column=def

-

На родном языке: Коваленко А.Е., Гула В.В. - Отказоустойчивые микропроцессорные системы. 1986 Пашковский Г.С. - Задачи оптимального обнаружения и поиска отказов в РЭА (Радио и связь, Надёжность и качество). 1981 Синтез сложных многофункциональных отказоустойчивых систем электроники. А. А. Авакян, В. В. Клюев (Спектр). 2014 Согомонян Е.С., Слабаков Е. В. - Самопроверяемые устройства и отказоустойчивые системы (Радио и связь). 1989 Бортовые системы управления космическими аппаратами: Учебное пособие. Под ред. А.С. Сырова (МАИ-ПРИНТ). 2010 Проектирование и испытание бортовых систем управления. Учебное пособие. Под ред. А.С. Сырова (МАИ-ПРИНТ). 2011 На английском: http://libgen.io/search.php?req=fault+tole...&column=def

-

OpTiMSoC - многоядерная СнК на OpenRISC