Zeroom

Свой-

Постов

381 -

Зарегистрирован

-

Посещение

Весь контент Zeroom

-

PCI-Express x1 x2 x4 назначение линий при разной разрядности

Zeroom опубликовал тема в Интерфейсы

На горизонте виднеется задача подключить на одну линию SATA и четыре линии PCI-Express от устройства с отладочной платы разъем M.2 под накопитель SSD, который в перспективе может быть как SATA, так и PCI-E x1, x2, x4. В связи с чем возникает совсем новичковый вопрос: каким образом назначаются линии PCI-Express для SSD при различной разрядности шины? Прямо по номерам - №0 для x1; №0 и №1 для x2; №(0-3) для x4? В таком случае независимо от разрядности потребуется дифференциальный переключатель между SATA и PCI-Express по линии №0? Или каким-то образом можно при разрядности x1 и x2 организовать работу по линиям №(1-3) и сделать прямое подключение SATA вместо линии №0? Если можно, ткните носом в страницы спецификации, где это расписано, сходу не нашел. Спасибо. -

Импорт схем Allegro -> Altium

Zeroom ответил Zeroom тема в Altium Designer, DXP, Protel

Проблема решена. Как оказалось, проект платы SP605 сохранен в более старом формате, чем VCU108, в котором схемы хранятся в базе данных формата ICDB, не воспринимаемой Altium'ом. Товарищ по ссылке ниже подсказал тернистый, но верный путь. https://www.eevblog.com/forum/altium/altium-importing-a-dxdesigner-design/ Пришлось экспортировать исходный проект из DxDesigner в формат EDIF, импортировать его в Orcad, сохранить в формате DSN, после чего, наконец, импортировать полученное в Altium Designer через встроенный Wizard. Среди ошибок и особенностей в конечном результате можно отметить рамку с основной надписью, оказавшуюся в итоге УГО компонента с кучей видимых параметров; потерявшуюся на некоторых листах цепь GND; множество расставленных по всей схеме Offsheet Connector'ов; незадействованные пины компонентов и "безымянные" цепи, снабженные метками цепей с автоматически сгенерированными именами. Пример результата прилагается. SHEET_4.SchDoc -

Импорт схем Allegro -> Altium

Zeroom ответил Zeroom тема в Altium Designer, DXP, Protel

Исходные схемные проекты временно разместил в /upload/__TRASH__/ sp605-schematic-source-rdf0038-rev-e.zip vcu108-schematic-source-rdf0358.zip -

Исходные схемные проекты временно разместил в /upload/__TRASH__/ sp605-schematic-source-rdf0038-rev-e.zip vcu108-schematic-source-rdf0358.zip

-

Пожалуйста, прочитайте внимательно: "вопрос к специалистам по DxDesigner'у: какие могут быть различия между данными проектам схем, каким образом можно их устранить, какие действия для этого предпринять? "

-

Добрый день! Есть проект отладочной платы Xilinx VCU108, взят с сайта производителя. Плата выполнена в Cadence Allegro, схема - в DxDesigner. Есть необходимость импортировать схему и плату в Altium Designer. Плату удалось получить относительно легко, используя Import Wizard в Altium'е. Со схемой возникла загвоздка следующего свойства: при попытке преобразования проекта через тот же Import Wizard импортируется только библиотека УГО, содержащая полтора десятка символов вида "одинокий пин". Несколько лет тому назад была успешно решена аналогичная задача с проектом отладочной платы Xilinx SP605, подобных трудностей в процессе не наблюдалось. Однако, тот проект, по всей видимости, был выполнен в более ранних версиях указанных выше программ. В связи с чем возник вопрос к специалистам по DxDesigner'у: какие могут быть различия между данными проектам схем, каким образом можно их устранить, какие действия для этого предпринять? Спасибо.

-

Импорт схем Allegro -> Altium

Zeroom ответил Zeroom тема в Altium Designer, DXP, Protel

Согласен, неточная формулировка. В Cadence Allegro разработана плата, а схема - в DxDesigner. Что не отменяет наличие проблемы, к сожалению. Есть подозрение, что проблема в структуре проекта. Несколько лет тому назад успешно импортировал проект отладочной платы SP605 (схема+плата), ее исходный проект был выполнен в Cadence Allegro 16 и, видимо, в какой-то более ранней версии DxDesigner'а. -

Импорт схем Allegro -> Altium

Zeroom ответил Zeroom тема в Altium Designer, DXP, Protel

Именно это я и пытаюсь сделать: " При попытке импортировать схему Wizard "видит" папку с проектом DxDesigner, но по неясным причинам импортирует только библиотеку компонентов, содержащую небольшой набор каких-то второстепенных УГО." -

Импорт схем Allegro -> Altium

Zeroom опубликовал тема в Altium Designer, DXP, Protel

Имеется исходный проект отладочной платы Xilinx VCU108 (взят на сайте производителя), разработан, судя по всему, в Cadence Allegro 17. При попытке импортировать схему Wizard "видит" папку с проектом DxDesigner, но по неясным причинам импортирует только библиотеку компонентов, содержащую небольшой набор каких-то второстепенных УГО. Как победить эту проблему? -

Altium Designer Version 13.0

Zeroom ответил VladKot тема в Altium Designer, DXP, Protel

Эта версия умеет считать длину цепи с учетом переходных отверстий? -

Корпусированный печатный узел, устанавливаемый в дальнейшем на другую плату как элемент. Доводилось такой проектировать. Борьба была не то что за полумиллиметры, за десятые и сотые доли.

-

Интересуют корпуса, предназначенные для установки в отсек привода компакт-дисков, либо дисковода/винчестера. Есть необходимость разместить устройство собственной разработки (плата с элементами) внутри корпуса персонального компьютера.

-

Крайне желательно именно пустые корпуса с крепежными отверстиями и самим крепежом, так как навскидку нашлись только всевозможные переходные планки для винчестеров.

-

Это не принципиально, Output можно назначить любому выводу или набору выводов, ошибка при этом не пропадает.

-

Все еще актуально

-

И опять про BGA c шагом 0.5

Zeroom ответил Svetlaya тема в Работаем с трассировкой

Заказывать можем только через посредника, посему прислушайтесь к ответу выше. -

В этом варианте удалены элементы DM9000. sdram.zip

-

И опять про BGA c шагом 0.5

Zeroom ответил Svetlaya тема в Работаем с трассировкой

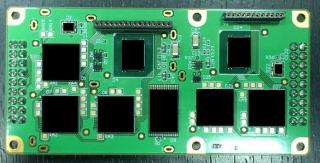

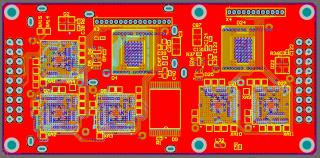

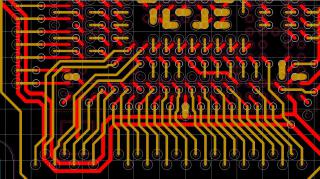

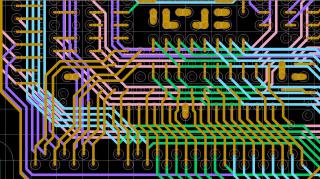

Добавлю свой вариант. Размер платы 83х40 мм. Пять штук BGA с шагом выводов 0,5 мм. На фото представлены смонтированная плата, общий вид в САПР, фрагмент фанаута и трассировки в нем же. Изготовлено в FastPrint, смонтировано в Фаствел. Технологические параметры: стек слоев 1-10-1 (внутренние - 6 сигнальных 4 питания) диаметр площадки под шарик - 0,25 мм переходы с наружних на внутренние слои - внешняя площадка 0,275 мм, внутренняя 0,3 мм, отверстие 0,1 мм переходы во внутренних слоях - площадка 0,4 мм, отверстие 0,2 мм зазор/проводник - 0,1/0,1 толщина платы - проектная 1,5 мм +-10%, действительная 1,58 мм. -

Проверял и даже пробовал корректировать средствами редактора. Не помогает. Модели скачаны у производителей. ibs.zip

-

Большое спасибо за информацию, самостоятельно чего-то не нашел. А по другому вопросу можете что-нибудь подсказать?

-

HyperLynx 8.0 пара вопросов

Zeroom опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Вопрос первый. Как забороть ошибку "DC operating points not valid" в пакетном моделировании? В помощи говорится, что это скорее всего проблема в модели, но что с этим делать - непонятно. Вопрос второй. При импорте PCB в HYP и последующей загрузке его в BoardSim выдается ошибка "Illegal Pad строка такая-то". Полазив по файлу HYP, обнаружил, что в строке вида: {PADSTACK=2, 0.0000 (TOP, 1, 0.0394, 0.0394, 0, M) } в случае, когда она "Illegal", отсутствует второе значение в круглых скобках( в данном случае выглядит так: (TOP, , 0.0394, 0.0394, 0, M)). Понятно, что это описание падстеков. Пытался корректировать указанные площадки в библиотеках и PCB наугад - безуспешно. Кто-нибудь может подсказать, что оно означает? Спасибо. -

Многослойная печатная плата - сборочная единица. На нее выпускается сборочный чертеж. Если слоев больше 5, то номер будет 68726X, X зависит от размеров платы.

-

Насколько помню, защита достигается толщиной стенок корпуса, исходя из заданных параметров облучения и известной эффективности поглощения разными материалами. Мне надежник после расчетов написал сделать внутреннюю крышку на часть внутренностей.

-

1к чего? зелени? для "бел. реальности" это мало, много или в самый раз на прожитуху?