-

Постов

365 -

Зарегистрирован

-

Посещение

Весь контент gosha

-

https://www.newark.com/productimages/standard/en_US/04M5427-40.jpg На фотке м/сх маркировка: PIC16F676-ICD В простой PIC16F676 - не доклали отладчик ?

-

#include <xc.h> #pragma config FOSC = INTRCCLK // Oscillator Selection bits (INTOSC oscillator: CLKOUT function on RA4/OSC2/CLKOUT pin, I/O function on RA5/OSC1/CLKIN) #pragma config WDTE = OFF // Watchdog Timer Enable bit (WDT disabled) #pragma config PWRTE = OFF // Power-up Timer Enable bit (PWRT disabled) #pragma config MCLRE = ON // RA3/MCLR pin function select (RA3/MCLR pin function is MCLR) #pragma config BOREN = ON // Brown-out Detect Enable bit (BOD enabled) #pragma config CP = OFF // Code Protection bit (Program Memory code protection is disabled) #pragma config CPD = OFF // Data Code Protection bit (Data memory code protection is disabled) /*========================================================*/ void __interrupt() timer_isr(void) { if(TMR0IF==1) { TMR0= 101; TMR0IF=0; } if(TMR1IF==1) { TMR1= 101; TMR1IF=0; } RC2=~RC2; } /*========================================================*/ void main(void) { int i; TRISC2= 0; TRISC3= 0; OPTION_REG = 0x07; // Timer0 with external freq and 32 as prescalar TMR0=100; // Load the time value for 1ms delay TMR0IE=1; //Enable timer interrupt bit in PIE1 register GIE=1; //Enable Global Interrupt PEIE=1; //Enable the Peripheral Interrupt while(1) { for(i=0 ; i < 10000; i++) continue; RC3=0; for(i=0; i < 10000; i++) continue; RC3=1; } } Connecting to MPLAB PICkit 3... Currently loaded firmware on PICkit 3 Firmware Suite Version.....01.56.09 Firmware type..............Midrange Target voltage detected Target device PIC16F630 found. Device Revision ID = 4 Device Erased... Programming... The following memory area(s) will be programmed: program memory: start address = 0x0, end address = 0x63 configuration memory Programming/Verify complete The target device is not ready for debugging. Please check your configuration bit settings and program the device before

-

pic16f628а внутрисхемную отладку не поддерживает ? Ругается: "Programming/Verify complete The target device is not ready for debugging. Please check your configuration bit settings and program the device before proceeding. The most common causes for this failure are oscillator and/or PGC/PGD settings."

-

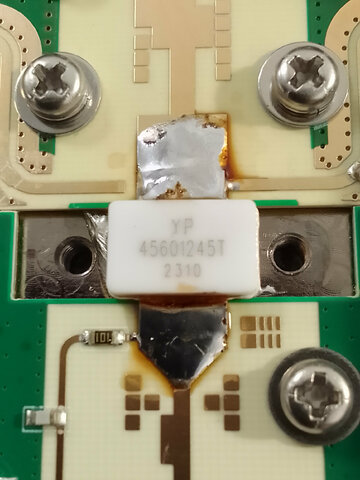

Марку транзистора не подскажете ?

gosha опубликовал тема в RF & Microwave Design

-

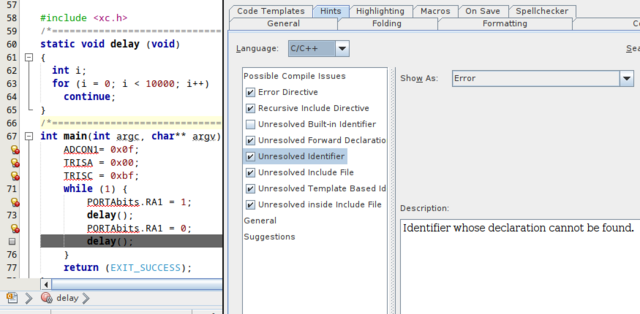

MPLAB-X unresolved identifier TRISA

gosha опубликовал тема в Cредства разработки для МК

MPLAB-X unresolved identifier TRISA Проект компилируется, и работает. А редактор среды подсвечивает ошибку. Ubunta Как победить ? -

Посоветуйте блоки для глушилки БПЛА.

gosha ответил gosha тема в RF & Microwave Design

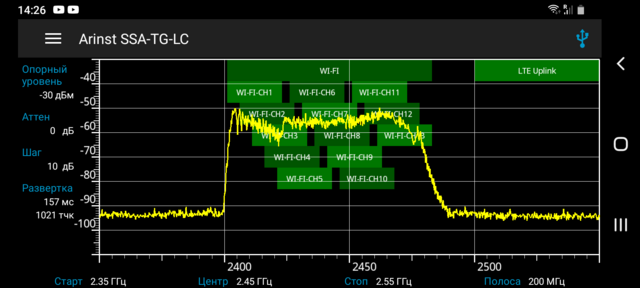

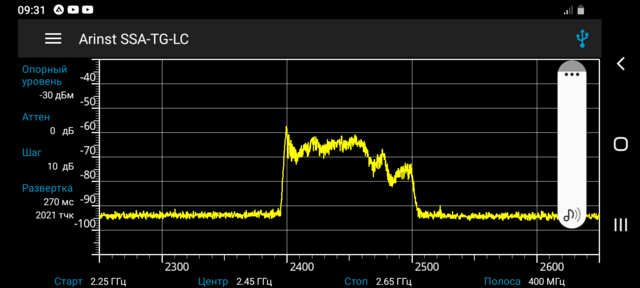

В этой статье принимаемый сигнал усиливается, и излучается обратно. Вероятно, в противофазе ? Это более эффективный вариант ? How to Make A Drone Jammer? (Step by Step Instructions) С панельной антенной, спектр получается немного лучше. Спасибо. -

Посоветуйте блоки для глушилки БПЛА.

gosha ответил gosha тема в RF & Microwave Design

Спасибо. Что означает глушить интрмодуляцией ? Что означает глушить блокированием ? Применение блоков 50 Вт (вместо 10Вт которые сейчас) решит проблему подавления малоразмерных БПЛА Mavic и Autel ? Например, таких: UAV jamming module WIFI UAV jammer eviscer 900MHZ 1.2G 1.5G 2.4G 5.8G 30W 50W Transmitter Power БПЛА Mavic 3 (EIRP) 2.4 GHz: ≤33 dBm (FCC); ≤20 dBm (CE/SRRC/MIC) 5.8 GHz: ≤33 dBm (FCC), ≤30 dBm(SRRC), ≤14 dBm(CE) Почему советуете рупорную антенну ? Один из критериев: удобство пользования, компактность. Исходя из этого, панельная антенна намного хуже вариант ? У KPM12-2400/5000 крокса неплохая диаграмма направленности. И мощность до 50 Вт. Измерительная WiFi антенна KPM12-2400/5000 Получится такой конструктив: D4 Handheld Portable Drone Signal Jammer Какую портативную рупороную антенну по-советуете ? -

Посоветуйте блоки для глушилки БПЛА.

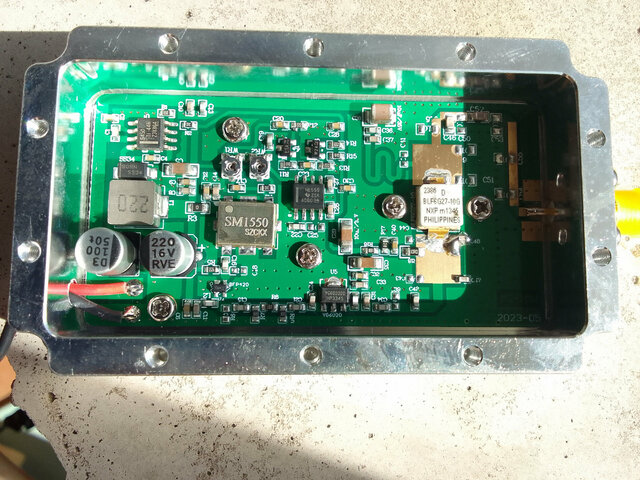

gosha опубликовал тема в RF & Microwave Design

Посоветуйте модули для самодельного ружья против дронов 2.4 ГГц ? Которые модулировали бы несущую шумом в диапазоне частот 2400 - 2483,5 МГц. Купил блоки на алиэкстпрессе. - Не глушат БПЛА. https://aliexpress.ru/item/1005005537625980.html Похоже, они не белым шумом модулируют несущую, а качающейся частотой. м/сх VCO SM1550 установлена. SM1550 - м/сх VCO voltage controlled oscillator 1450-1650MHZ https://aliexpress.ru/item/32846150252.html -

Как называется клейкая тонкая ткань для шлейфов ?

gosha опубликовал тема в Пайка и монтаж

-

https://docs.xilinx.com/r/2021.1-English/ug900-vivado-logic-simulation/Running-the-Vivado-Simulator-in-Batch-Mode https://support.xilinx.com/s/article/63986?language=en_US

-

https://blog.csdn.net/yihuajack/article/details/120714268 https://support.xilinx.com/s/question/0D52E00006hpSEgSAM/bd-412088?language=en_US

-

Xilinx создание coe file

gosha ответил IgorMov тема в Языки проектирования на ПЛИС (FPGA)

coe-File-converter-for-FPGA-programming-master.zip -прикрепленный файл coe-File-converter-for-FPGA-programming-master.zip -

Xilinx создание coe file

gosha ответил IgorMov тема в Языки проектирования на ПЛИС (FPGA)

https://github.com/vortexgpgpu/bin2coe/blob/master/main.cpp -

У меня, задание ручками output_delay только ухудшило ситуацию. Из-за тупости, не смог расчитать верные изначения.. Задание только частот всех синхросигналов - оказывалось всегда достаточным, если топология не кривая. Убрать set_output_delay совсем не пробовали ?

-

Если поможет, проект pcie платы Ethernet c SFP 1G - прикрепленный файл Без DMA. Но, подключенное через SFP, - пингуется. Для платы http://www.alinx.com/en/index.php/default/content/121.html Eth_vnniftri.tar.gz

-

PCI express gen_1 есть y gowin ? Существует ли/приобретается ли Dev_ board gowin PCI express ?

-

Вопрос снят. Переименовал library work в eth, и файлы поместил в эту lib. - Заработало. Почему vivado игнорирует library work- загадка природы.

-

Все так. rx_pack попал в - unreferenced ! Например, Константы не видятся: Проект целиком Vivado_2019: https://drive.google.com/file/d/1rT2sp_43RfLxwJgWoljNy9uKXzIvp_mD/view?usp=sharing rx.vhd rx_pack.vhd ptp_pack.vhd

-

ISE + Synplify

gosha ответил Jackov тема в Среды разработки - обсуждаем САПРы

Проект в synplyfy. Из synplyfy на стадии имплементации вызывается ISE. Или проект в Active_HDL: Настройки: синтезис в synplify, implementation в ISE. В закромах 2013- прекрасно работает,- Пользовал. 2019 работает, но перед пуском каждый раз надо запускать менеджер лицензий. -

--rx_pack.vhd library STD, IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.numeric_std.all; package RX_PACK is function EQUAL (A: std_logic_vector; B: std_logic_vector) return std_logic; package body RX_PACK is function EQUAL (A: std_logic_vector; B: std_logic_vector) return std_logic is begin if A = B then return '1'; else return '0'; end if; end EQUAL; end RX_PACK; --======================================================================== --decode_frame.vhd library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; library work; use work.RX_PACK.all; entity DECODE_FRAME is port( end DECODE_FRAME; architecture RTL of DECODE_FRAME is begin END_OF_PAYLOAD: process (RX_CLK) begin if RX_CLK'event and RX_CLK = '1' then if RESET = '1' then LENGTH_MATCH <= '0'; LESS_THAN_256 <= '0'; LENGTH_ZERO <= '0'; LENGTH_ONE <= '0'; elsif CE_IN = '1' then if END_OF_FRAME = '1' then LENGTH_MATCH <= '0'; elsif DATA_FIELD = '1' then LENGTH_MATCH <= EQUAL(LENGTH_TYPE(10 downto 0), std_logic_vector(DATA_COUNTER(10 downto 0)) ); end if; LESS_THAN_256 <= LENGTH_FIELD and FIELD_COUNTER(0) and EQUAL(RXD, "00000000"); LENGTH_ONE <= LENGTH_FIELD and FIELD_COUNTER(1) and EQUAL(RXD, "00000001") and LESS_THAN_256 and (not LT_CHECK_DISABLE); LENGTH_ZERO <= LENGTH_FIELD and FIELD_COUNTER(1) and EQUAL(RXD, "00000000") and LESS_THAN_256 and (not LT_CHECK_DISABLE); end if; end if; end process END_OF_PAYLOAD; --======================================================================== end RTL; --======================================================================== В Vivado и rx_pack.vhd decode_frame.vhd - в library work поместил. В compile_order правильно: rx_pack.vhd, затем decode_frame.vhd Что делаю не так ?

-

Насчет помех на все неиспользуемые выходы- внутренний pull-down спасает при отсутствии ядерной войны. Чтобы навести помеху на шарик BGA или подлезть к шарику статикой - это надо сильно постараться.

-

Как я полял, - улучшает только защиту от ESD. Если не подключите ESD защиту к каждому pin, - это не спасет. И на дорожки от pin будут наводиться помехи.

-

Собираетесь работать без браслета, и тыкать пальцем в xilinx ?? На опыте. Плисины не дохнут, не глючат.

-

есть лицензия license mager^ source, 2025 Когда собираю проект, включающий сгенерированную IP (tri_mode_ethernet_mac) - проект bitstream собирается. Когда из IP проекта беру исходники от tri_mode_ethernet_mac, удаляю IP( tri_mode_ethernet_mac) из проекта ---- выдает что нет лицензии при создании bitstream. Что делаю не так ? Как победить ? Нужно для небольшой модиификации исходников tri_mode_ethernet_mac в проекте. Разобрался. Вопрос снят.

-

Не используемые- не запрограммированные. Которые не планируете использовать pin - не надо программировать совсем. И никуда не надо подключать. Никогда проблем не было. Не усложняйте топологию. Есть оция pull-up и pull-down внутри ПЛИС, если хотите параноидальную подтяжку. BITSTREAM.CONFIG.UNUSEDPIN PULL-UP