Aleks17

Свой-

Постов

245 -

Зарегистрирован

-

Посещение

Весь контент Aleks17

-

Ведущий инженер-программист FPGA

Aleks17 ответил Оля UserGate тема в Предлагаю работу

Предположим слова знакомые, но вы вилку зарплат хотя бы обозначьте. -

Простите мой сарказм, не могу удержаться. Хорошо что шеф не отправил вас работать хирургом. :). Я боюсь что вашу задачу не получится решить с помощью форума, нужно что-то посерьёзнее. Например профильное образование.

-

Круто. Шикарные железки, но пока мимо. 6063 думаю и нынче не сильно дороги, а тут большая плата с кучей микросхем, SFP корзинами и т.п. :).

-

Вот уже и очередь собралась. :).

-

Железок со свичами Marvell не оттает?:) Было бы интересно.

-

Собственно в шапке всё написано. Может у кого есть в загашнике, может сэмплы кто выписывал с Texas. Нужно то немножко, штук 20, просто Texas (как и многие прочие) навернулся в плане сроков поставки.

-

Трафареты

Aleks17 ответил A_D тема в Пайка и монтаж

Периодически заказываем трафареты в китае, как правило на том же пцбвэй. Проблем как таковых не возникало ни разу. При этом надо понимать что сроки изготовления и правда 1-2 дня, а вот идти может сильно дольше (особенно с учётом того, что наши тварцы законов любят палки в колёса вставлять периодически). Соответственно если сроки горят - лазер-трафарет, ценник правда сильно отличается. Для мелко/средне серийного производства имеет смысл размещать top/bottom на одном трафарете. Т.к. китайцы денег за апертуры не берут то выходит дешевле. -

SGMII SFP

Aleks17 ответил Realking тема в Цифровые схемы, высокоскоростные ЦС

Модули c PHY на борту как правило можно настраивать, зависит от используемого PHY. Например большая часть медных модулей построена на Marvel 88E1111 c выводом TWSI на ноги модуля (параллельно EEPROM, только адрес другой - как правило 80h (вместо A0 для EEPROM)). Так что можете по крайней мере почитать регистры статуса PHY. Ну или включить loopback если он имеется. А вообще интересное решение - вместо простой и дешёвой гигабитной оптики ставить более дорогой модуль с PHY на борту - в чём тайный смысл? Проверьте link с другой стороны оптики - там случайно не гигабит поднялся? -

имхо, Atmel целенаправленно шёл к закрытию. Продажа для них хороший выход. На мой взгляд главная их беда не отсутствие нового, или скажем плохой софт, а наплевательское отношение к кастомерам. После последнего (второго на моей памяти) косяка с поставками, когда после продажи фабрик сроки поставки микросхем выросли до года, в нашей конторе на продукции Atmel был поставлен жирный крест.

-

Бюджет SFP vs 1X9

Aleks17 ответил MIKS тема в Fast Ethernet/Gigabit Ethernet/FibreChannel

Правильно кажется. SFP трансиверы это скорее 30-40$ + 2-3$ за корзину+разъём. Имеет смысл для гигабитного линка, там бюджеты SFP и 1х9 примерно одинаковы + появляется большая гибкость (скажем можно воткнуть медный SFP если вдруг появится необходимость). С другой стороны при использовании 1x9 модуля вам на этапе монтажа платы необходимо знать длину волны, тип волокна и дальность что несколько уменьшает гибкость применения. Да и вообще, имхо, 100-мбитная оптика медленно но верно умирает. Если планируется длительный срок производства может стоит задуматься о гигабитном линке. -

Помню несколько лет назад ловили на мостовой схеме странные низкочастотные помехи, которые появлялись и пропадали с периодом от нескольких минут до нескольких часов. Дело оказалось в плохих цепях питания (в смысле в низком PSRR) а шум появлялся при включении компрессора у холодильника в соседней комнате :).

-

R200 - это нагрузка, я правильно понимаю? Давайте начнём с того что напряжение на затворе блокирующего транзистора будет 27-80 вольт (недолго :)).

-

Ну так то вам правильно сказали. Для начала стоить определить где теряются пакеты. Как я понял есть два линка (сеть - PHY - FPGA - switch) и (switch - CPU). Switch управляемый ? Содержит счётчики принятых/отправленных/ошибок? Flow control присутствует где-нибудь? Нет ли потери пакетов в софте процессора?

-

Исходя из практического опыта - можно. Выпущена не одна тысяча устройств и работают уже более 10 лет. Объединялись именно с целью увеличения выходного тока по 3 ноги Cyclone.

-

Физика у всех этих режимов одна и та же - согласно спецификации 1000Base-X. SGMII - расширение от фирмы CISCO, позволяющее подключать PHY и осуществлять автоматическую настройку speed/duplex... (при этом надо заметить что даже при установившейся в PHY скорости 100Мбит/с - скорость в SGMII, всё равно останется 1.25 Gbps). Если отключать SGMII auto-negotiation и задавать скорость и дуплекс вручную - всё будет работать. Cross - chipа у 6131 нет. Все режимы выбираются программно. Предпочтение тому или иному - только на основании того, что будет с другой стороны - если это порт внутри устройства и заранее известно, что там будет другой 88E6131 - выбирайте что хотите и задавайте принудительно линк, скорость и дуплекс. Если открытый порт и возможно подключение других устройств, либо другая м/сх опциональна - выбирайте режим с автоопределением. Для cross-chip-а это будет 1000Base-X.

-

Register packing включён. Синхронный сброс (включение- выключение) тоже не влияет. Ситуацию удалось побороть отключив в fitter-е опцию "optimize hold timing for all paths". Уж не знаю, что там quartus себе придумал но он решил разнести carry chain и регистры подальше в устройстве. Дизайн полностью синхронный, clock-и глобальные. Все те счётчики (и их ввходные и выходные регистры) - в одном clock домене. Не понимаю, что там за проблемы с hold timing-ом могут быть (кстати hold violation для этих сигналов не появляются ни с опцией, ни без неё).

-

Как заставить Quartus экономить LABы

Aleks17 опубликовал тема в Среды разработки - обсуждаем САПРы

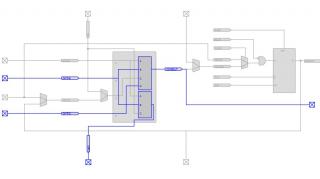

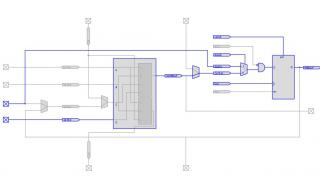

Ситуация такова : есть некий проект (Ethernet-устройство). Чип - Cyclone IV GX, утилизация - 99% (не стоит кидать в меня камнями, сам знаю что нельзя так работать, но бОльшего устройства в этом корпусе нет). Так вот, занялся оптимизацией ресурсов - обратил внимание, что счётчики занимают ровно в 2 раза раза больше LCELL-ов, чем их (счётчиков) разрядность. Стал копать - ситуация примерно следующая. Счётчик, описанный следующим образом : link_timer : LPM_COUNTER generic map ( LPM_WIDTH => 22, LPM_DIRECTION => "UP", LPM_TYPE => "LPM_COUNTER", LPM_PORT_UPDOWN => "PORT_UNUSED" ) port map ( clock => tx_clock, SCLR => link_timer_reset, COUT => link_timer_cout, ACLR => reset ); Размещается на кристалле следующим образом : каждый разряд занимает 2 LCELL-а. В одном - логика (carry chain и сумматор), в другом - собственно регистр с синхронным и асинхронным сбросом. При этом синхронный сброс на регистр заведён как SLOAD а нога SDATA приходит с некой LCELL, порожденной воспалённым мозгом компилятора , называемой GND (что это вообще) !!! (вход DATAD это непосредственно combout ячейки с LUT) По моему представлению (да и по размещению) описанная сверху схема должна занимать ровно столько LCELL-ов, какова разрядность счётчика. Как в этом убедить квартус ? P.S. Максимальная длинна carry цепочек задана как 70. Цепочки строятся, только почему-то располагаются отдельно от регистров. Никаких констрэйнов на размещение этих регистров нет. -

А есть у кого-нибудь валидное лекарство для этой версии ? Воспользовался лекарством из закромов, но что-то signal tap, тьфу logic analyzer отказывается собираться при использовании ILA v2.0. "ERROR: [Chipscope 16-111] License check failed for Vivado Analyzer feature - aborting debug core implementation..."

-

Я всегда думал, что главная задача такой индуктивности - ограничить скорость нарастания тока при скажем КЗ или резкой остановке (заклинивании мотора), для того чтобы успели сработать цепи защиты или обратной связи по току.

-

Новосибирск, весна пришла

Aleks17 опубликовал тема в Встречи и поздравления

Ни разу не был на форумовстречах. давайте организуем. Чинно, степенно, электроника, водка, танцы.. Шашлыки могу взять на себя. По дате - начало июня - скажем 01.06 - 02.06. Формат свободный, фраки оставляем дома. Насчёт места пока вопрос, можно коттедж взять, но для того надо хотя-бы несколько желающих. Устроить битву роботов... Открыть чёрные дыры, закрыть белые... В-общем, культурная программа обсуждается. -

А кто поможет с лицензией? У нас почему-то старая лицензия работать перестала. SOPC builder говорит "Encrypted license not found. Defaulting to OCP evaluation license (produces a time-limited SOF)".

-

MEMS генераторы против кварцев

Aleks17 опубликовал тема в Компоненты

Задача такая : нужен генератор 125МГц с LVDS выходом (пойдёт на Cyclone IV GX трансиверы). Насколько я понимаю, без PLL не обойтись в любом случае : и в случае кварца и при использовании MEMS. Включил сегодня два мемса - поразился что частоты (друг относительно друга) плавают туда-сюда (в пределах +-2ppm) - но именно плавают, а не просто одна больше другой. Вот и вопрос : проглотит ли альтеровский PLL такой сигнал. Есть у кого-нибудь опыт применения MEMS генераторов в высокоскоростных цепях (1/10 Gigabit Ethernet к примеру)? -

Проблема с AVR Dragon

Aleks17 ответил Titivanich тема в AVR

Сегодня наблюдали подобный глюк в Dragone. После connect-а выполняет только одну операцию (erase, read ID, read fuses и т.п.) - любую, но только одну. После этого - связь дохнет. Дисконнект (закрытие окошка) и повторное открытие - и снова можно выполнить одну операцию. Вылечилось переводом ISP частоты со 100Гц до 500кГц. -

Вы видимо спали последние несколько месяцев, 10$ теперь - очень хорошая оптовая цена. Для автора - http://www.serialflash.com/framework.php?UID=88 . Выбирайте. Я лично рекомендую взглянуть на Numonyx и SST - не так давно они оказались наиболее доступными и дешевыми.

-

Ну вообще-то по этой самой ссылке видно что в 2000-м году они были по 25$.