djhall

Свой-

Постов

222 -

Зарегистрирован

-

Посещение

Весь контент djhall

-

Продскажите, пожалуйста, возможно ли подключить внутренний АЦП в FPGA MAX 10 к temperature sensing diode (TSD) для измерения температуры кристала, так чтобы IO в банке 1A можно было использовать как general purpose IO? Сейчас выдаёт такую ошибку, хотя вход АЦП я не использую:

-

Овальные отверстия

djhall ответил djhall тема в Разрабатываем ПП в САПР - PCB development

Сообщение в логе при генерации NC Drill в Cadence PCB Editor: WARNING(SPMHMF-365): This design contains 4 slot holes that can NOT be drilled. WARNING(SPMHMF-366): They can be processed by NC routing instead. -

Овальные отверстия

djhall ответил djhall тема в Разрабатываем ПП в САПР - PCB development

Поправьте если я не прав: 1. По сути такое отверстие это просто выфрезерованное прорезь. Для её создания нужно генерировать не NC Drill, а NC Route файл. 2. Внутри файла NC Drill есть указание какое отверстие металлизированное, а какое нет. NC Route файле такого указания нет. Праильно ли я понимаю, что производитель должен узнать о метализации отверстия из сборочного чертежа? -

Овальные отверстия

djhall опубликовал тема в Разрабатываем ПП в САПР - PCB development

На печатной плате есть овальные метализированные отверстия. Обычно для круглых отверстий я создаю файл NC Drill и этого достаточно, но в этот раз появилось сообщение, что овальные отверстия не могут быть просверлены. Подскажите, пожалуйста, какой выходной файл необходимо передать производителю, чтобы получить эти отверстия? -

Смысл это действа вестьма прост, во всяком случае по задумке. Интеловские ПЛИС невозможно купить, причём не только в России, но и в Китае, может и вообще нигде. Если что-то и есть ценник на них просто конский - если бы их делали из золото возможно они были бы дешевле. Далее лёгкий поиск по digikey показал, что если интеловских ПЛИС в наличии считай нет, то Lattice присутствует. Следовательно переходим на Lattice. Далее подумалось о Gowin. А что посоветуете Вы?

-

Быстрое переключение на Lattice

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Задача у меня "простая" - быстро переключиться с FPGA Intel на FPGA Lattice. Подскажите как бы мне это наиболее безболезненно сделать, т.е. воссаздать всю инфраструктуру для разработки. 1. Программное обеспечение. Для Intel это Quartus. Что для Lattice? На их сайте много ПО - Lattice Diamond, Lattice Radiant, Lattice Propel. Что из этого использовать? 2. Процессор. Для Intel это Nios. Что для Lattice? 3. Platform Designer или QSys для создания систем с процессором и IP блоками для Intel. Что для Lattice? 4. Разработка ПО для процессора. Nios II Software Build Tools for Eclipse для Intel. Что для Lattice? 5. Симуляци IP блоков. ModelSim и сгенерированные Quartus библиотеки для Intel. Что для Lattice? 6. IP блоки - DDR, CPU и пр. Входят в Quartus и доступны в нём или в Platform Designer. 7. Лицензия. FTP для Intel. Что для Lattice? Буду признателен за разъяснения. -

USB 3 и USB Type-C

djhall опубликовал тема в RS232/LPT/USB/PCMCIA/FireWire

Доброго! Мне необходимо подключить микросхему Cypress FX3 (CYUSB3014) к разъёму Molex USB Type-C (1054500101). Но вот не могу уяснить кое что. Вот ссылка с описанием различных вапиантов подключения: https://community.infineon.com/t5/Knowledge-Base-Articles/Designing-Type-C-products-based-on-EZ-USB-FX3-and-CX3-KBA218460/ta-p/251806 1. FX3 Type-C Plug Design - без использования мультиплексора. 2. FX3 Type-C Receptacle Design - с использованием мультиплексора. Вопросы: 1. Правильно ли я понимаю, что разъём USB Type-C полностью симетричен и его можно подключать любой стороной, как это мы делаем в смартфонах. 2. Правильно ли я понимаю, что линии RX и TX можно менять местами и хост перенастроит линии необходимом образом. 3. Правильно ли я понимаю, что если использовать вариант подключения без мультиплексора, то разъём всё равно можно будет переворачивать и хост перенастроит линии необходимом образом. 4. Зачем тогда мультиплексор? -

FPGA + SD card

djhall ответил djhall тема в Работаем с ПЛИС, области применения, выбор

Как ни странно, но получилось. ПЛИС Cyclone V на плате SOCKit - там есть перемычка позволяющая изменять напряжение в банке. В прошивке установлено - 3,3 LVCMOS, фактически подано 1,8В, подтягивающие резисторы внутренние. Пока проэкспериментировал только на одной карте ёмкостью 512Гбайт. -

FPGA + SD card

djhall ответил djhall тема в Работаем с ПЛИС, области применения, выбор

Попробую, но есть опасения что 1.8 В мало для логической единицы. -

FPGA + SD card

djhall ответил djhall тема в Работаем с ПЛИС, области применения, выбор

Вообще максимальная скорость на 3,3 вольтах, которую мне удавалось получать это ~23 Mбайт/сек, но хотелось бы больше. @djhall Ого, если не секрет, - могли бы сфотографировать карточку? (не срочно) Да нечего там особо фотографировать обычная карточка десятого класса или лучше, в режиме SD, по 4 пинам. -

FPGA + SD card

djhall ответил djhall тема в Работаем с ПЛИС, области применения, выбор

Вообще максимальная скорость на 3,3 вольтах, которую мне удавалось получать это ~23 Mбайт/сек, но хотелось бы больше. Правильно ли я понимаю, что можно сделать прошивку с питанием банка от 3,3В, а затем переключить внешний источник питания банка на 1,8В и продолжить работу уже с уменьшинным напряжением питания? Какие же будут уровни нуля и единицы входа если в прошивке запрограммированно 3,3В, а реально подано 1,8В? -

FPGA + SD card

djhall опубликовал тема в Работаем с ПЛИС, области применения, выбор

Задача у меня простая - повысить скорость записи на SD карту. Для этого требуется перевести карту в режим работы с сигналами напряжением 1,8В, вместо 3,3В. Для этого импользуется микросхема преобразования уровней NVT4857. Но работает она как-то плохо - вроде карта и иницивлизируется при тактовой частоте около 400кГц, но на нормальной скорости карта не отвечает. Возможно как-то подключить SD карту непосредственно к ПЛИС и затем в нужный момент переключать питание банка с 3,3В на 1,8В? Вероятно пири этом нужно проводить реконфигурацию ПЛИС. Например в используемой мной ПЛИС MAX10 возможно хранить две прошивки в памяти. Или может кто-нибудь работал с микросхемой NVT4857 и поделится опытом. -

Вроде оно - https://platform.efabless.com/design_catalog/ip_block/ Но что-то я не наблюдаю там ничего открытого.

-

Видел эти примеры, спасибо. Там у этого чувака ещё много интересного есть в репозитарии и плюс на гугл-диске. Тут недавно предлагали создать профессиональную ассоциацию по микроэлектронике. Вот бы ей заниматься созданием открытых проектов для обучения.

-

IO pads

djhall опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

Я пытаюсь сделать простенькую микросхемку - своего рода помигать светодиодом. Использую GPDK45nm из закромов. В Innovus -> Import design добавляю: 1. Нетлист после синтеза 2. Lef файлы: ..../gsclib045/lef/gsclib045_tech.lef ..../gsclib045/lef/gsclib045_macro.lef ..../giolib045/lef/giolib045.lef 3. IO файл 4. Power: VDD VSS 5. MMMC файл В итоге я ожидаю получить кольцо ножек кристала где жёлтые треугольники (io pins) привязаны к IO Cell и после разводки нетлист присоединяются к IO кристала. А получаю, что ничего ни к чему не присоединяется и после разводки io нетлиста располагаются в примерно одной точке floorplan'а и ни к чему не присоединяясь. Подскажите как делать правильно. -

Я имел ввиду, что через iScape можно указать только папку CDROM1 - она определяется как пакет и может быть установлена. Папка CDROM2 не содержит необходимых файлов и как пакет не определяется.

-

Там какая-то непонятка с установкой. Там две папки - CDROM1 и CDROM2. А как их указывать при установке? CDROM1 можно указать, а CDROM2?

-

Ну так-то я понимаю, что они существуют в природе. Имелось ввиду всё же нечто доступное для скачивания. AMSKIT кит есть в закромах, но что-то пока его не удалось включить.

-

Ну на мой взгляд вы описали три разных составляющих знания - знание инструментов (cadence и пр.), теоритические знания (из книжек и пр.) и примеры (теоритическое описание реактивного двигателя и его воплощение довольно сильно отличаются ввиду множества практических и технических нюансов). Так что вопрос остаётся открытым. В закромах есть такие штуки: AMSKIT51 и EDI - это оно или нет? Кто-нибудь пользовался? Есть ли что-то ещё доступное?

-

Reference designs

djhall опубликовал тема в Разработка цифровых, аналоговых, аналого-цифровых ИС

Подскажите, пожалуйста, возможно ли где-нибудь достать референс дизайны для микросхем желательно под Cadence по типу https://platform.efabless.com/projects/public? -

На вход мы подаём изображение размером 2048 x 2048, где каждый элемент характеризует свет падающий на поверхность CMOS матрицы, например, световой поток. На выходе мы получаем изображение размером 2048 x 2048, где каждый элемент результат преобразования свететовой энергии в электрическую с учётом всех шумов, времени выдержки, разрядности АЦП и пр. - в конечном итоге для 12-ти разрядного АЦП, мы получим числа от 0 до 4095.

-

Моделирование изображения CMOS матрицы

djhall опубликовал тема в Оптика и оптоэлектроника

Например есть такая CMOS матрица Gpixel GSENSE2020 (это чисто для примера), которая обладает определёнными характеристиками: - Resolution (разрешение): 2048 x 2048 pixels - Frame rates (частота кадров): 45 - 93 Fps - Pixel size (размер пикселя): 6.5 μm - Dynamic range (динамический диапазон): 87 dB - Full Well Capacity (ёмкость пикселя): 45 000 e- - Readout noise (шум чтения): 2 e− - Signal to noise ratio(сигнал/шум): 46 dB - Exposure range (время выдержки): 8 μs - 30 s Ну и видимо есть ещё куча прочих характеристик таких как темновой шум, квантовый выход и пр. Плюс к этому есть источник света заданной интенсивности, например звезда или флюоресцирующая молекула или что угодно ещё. Подскажите, пожалуйста, как возможно смоделировать получаемое изображение. -

Tcl интерпретатор

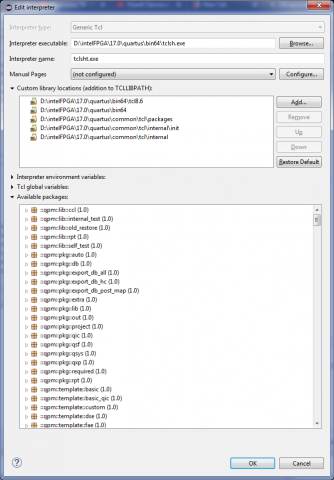

djhall ответил djhall тема в Языки проектирования на ПЛИС (FPGA)

Меня просто возмущает, что ни command line ни Tcl скрипты нельзя отлаживать, например тот же Python прекрастно выполняется по шагам и ни каких проблем нет. Конечно всегда можно отлаживать и просто выводя результаты в консоль, но это как будто бы прошлый век. Поэтому мне хотелось бы иметь возможность пошагово отлаживать .tcl скрипт. Я установил Eclipse, модуль для поддержки Tcl и отладчик. Указал в качестве интерпретатора интерпретатор от Quartus и подключил (прописав в TCLLIBPATH - там есть это в настройках при выборе интерпретатора) пакеты из папки quartus\common\tcl\packages А вот подключить пакеты ::quartus::flow, ::quartus::project и прочие не удаётся. Может быть они действительно находятся где-то в .dll-ках или ещё где. Но это не значит, что их нельзя подключить. Может кто укажет как это сделать. -

Tcl интерпретатор

djhall опубликовал тема в Языки проектирования на ПЛИС (FPGA)

В Quartus используется язык Tcl для создания проектов, разного рода присвоений, компиляции и др. И соответстенно есть консоль для ввода комманд: Tcl Console. Там можно загружать package ну и работать вообщем. Но ведь Tcl это это интерпретируемый язык программирования, имеющий свой интерпретатор - это tclsh.exe в папке quartus\bin64 Но вот если запустить этот интерпретатор, то стандартные действия языка Tcl производить можно, а вот всё что относится непосредственно к Quartus не запускается. Пишет, что не может найти соответстующий пакет. Подскажите можно ли догрузить квартусовский функционал непосредственно через интерпретатор? Может быть даже не через родной интерпретатор? -

А можно какой-нибудь пример или ссылку на пример. Я понял так: например, мне нужно просимулировать двадцать вариантов дизайна, чтобы выбрать лучший или просто убедиться в их работоспособности. Я с помощью скрипта .tcl выбираю нужные файлы копирую их в отдельную папку и отдельно создаю файл с параметрами, компилирую, запускаю симуляцию, сохраняю отчёт и далее по кругу 20 раз. Да спасибо огромное это очень похоже на то что нужно. Уже изучаю. Ну то есть нужно запускать симуляцию для каждого параметра, а параметр менять скриптом. Лучшее решение сохранить разные варианты IP или систем Qsys ну и скриптами генерить Qsys и перемещать по разным папкам для дальнейшей работы, как по ссылке https://gitlab.com/camlab/xilinx-vivado-bullet/wikis/Fpga build system ? Может есть какой промышленный стандарт для таких вещей, по типу https://gitlab.com/camlab/xilinx-vivado-bullet/wikis/Fpga build system ну или просто опробированное решение?