RobFPGA

-

Постов

3 315 -

Зарегистрирован

-

Посещение

-

Победитель дней

8

Сообщения, опубликованные RobFPGA

-

-

15 hours ago, makc said:

Есть большой шанс, что ПЛИС не успеет выполнить реконфигурацию, т.к. на некоторых платах длительность PERST# при тёплой перезагрузке бывает около 10-15 мс. Т.е. это в итоге будет выстрел себе в ногу

Вообще то при горячем ресете не должно быть реконфигурации FPGA.

-

Несколько лет назад сталкивался в некоторых матерях с такой "фичей"/проблемой - если PCIe линк не поднимался/пропадал то система отключала клок на этом слоте и метила его как "проблемный" и потом поднять этот линк можно было только рестартом.

-

On 11/14/2023 at 3:12 PM, fguy said:

Даже и не представляю себе как люди жили без подсветки акси-шин по адресу.

Бедно жили, перебивались на sed-е и grep-e ...

-

-

55 minutes ago, fguy said:

Зато "рюшечек" навешали.

Значит эти "рюшечки" нужны большему числу недовольных ...

-

20 minutes ago, fguy said:

Хорошо осваивать когда все работает так как обещают, а когда в виваде глюк на глюке и глюком погоняет - радости мало. Проблем с покупкой вроде особых нет - пол крышки только зашлифовано - вот и вся разница.

Я пока особых отличией от того что обещают не находил. А глюки они есть всегда, в любом SW|HW можно найти, и даже в своих поделках ...

И часто бывает что то что кажется вам глюком, другим видится особенностью реализации, или вообще киллер-фичей.

В этом и состоит радость освоения - понять, простить и использовать то что есть ... -

3 minutes ago, Maverick_ said:

память может бы и из регистров или на LUT RAM

51 minutes ago, jenya7 said:у меня уже total memory bits 64% занято. мне вобще то нужно было оставить 50% свободных.

Прежде чем решать "как делать" определитесь "что вы хотите". Как вы предполагаете будет идти передача (побайтно или сразу бурст полным пакетом)? Каков максимальный размер пакета? Что должны делать другие модули когда передатчик занят (ждать, или накапливать данные в своем буферe)? и.т.д, и.т.п

И после всего этого может стать понятно что можно вообще без памяти обойтись, а достаточно будет простого арбитра ... -

4 hours ago, fguy said:

Вивадо и так опосля 2018.3 сплошной косяк - тем кто осваивает новые чипы (Версаль и т.п.) можно только посочувствовать.

Не надо им сочувствовать, у них все хорошо. Лучше посочувствуйте тем кто не может осваивать новые чипы ...

-

1 hour ago, Maverick_ said:

"развод" или правда?

Почему же развод?

Для TDC вполне стандартное решение, как и использование TDC для такого типа ADC.

Вопрос лишь в качестве и повторяемости результатов реализации такого ADC и зависимости их от окружающих факторов. -

18 minutes ago, Lotos said:

Но можно нарваться и придется переделывать на data_in, data_out и data_oe.

Последнее где я помню что такое было это был древний XIlinx Foundation ISE 3-й 4-й версии в далеких 2000-х.

Если боятся нарваться на такие древности то тогда и в "лес" ходить не надо ... -

8 hours ago, Plain said:

Тогда это не устойчивые, а обычные метастабильные триггеры, лишь каким-то способом упорядоченные.

Так я так и писал.

И кажется мне что "устойчивых" к метастабильности триггеров нет. На первый взгляд тот же триггер Шмитта думаю не спасет так как метастабильность в первой защелке возникает в момент когда замыкается общая ПОС. Поэтому малая локальная ПОС особой роли не будет играть. -

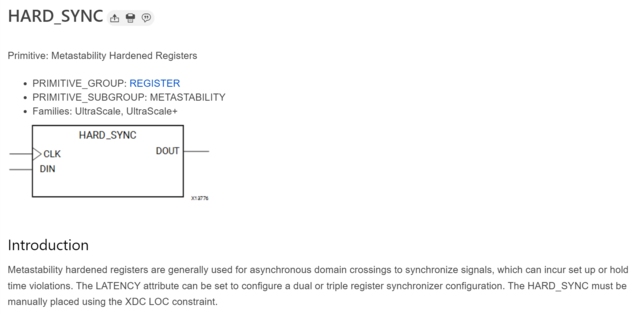

1 hour ago, _4afc_ said:

Однобитный?

Именно так,

1 hour ago, _4afc_ said:Шину в 32 бита сначала надо растянуть по кристаллу до 32шт HARD_SYNC, а потом собрать вместе?

Как и любую другую шину в FPGA ...

Да и передавать 32 бит шину через CDC такого типа нехорошая практика.

Хотя блоки BRAM имеют свои выделенные локальные хард-блоки CDC адресов для использования в режиме асинхронного FIFO -

1 hour ago, Plain said:

Но память раскидана по краям, и таких регистров можно было бы там же накидать, будь для них в языке свой тип, или хотя бы конструкция.

О каком языке вы говорите?

А конструкция она есть, и на Verilog и на VHDL.

Но это все равно - классический 2-3 триггерный синхронизатор, регистры которого выделены в отдельный хард-блок за счет чего минимизированы задержки что положительно влияет на MTBF при высоких тактовых.QuoteHARD_SYNC #( .INIT(1'b0), // Initial values, 1'b0, 1'b1 .IS_CLK_INVERTED(1'b0), // Programmable inversion on CLK input .LATENCY(2) // 2-3 ) HARD_SYNC_inst ( .DOUT(DOUT), // 1-bit output: Data .CLK(CLK), // 1-bit input: Clock .DIN(DIN) // 1-bit input: Data ); -

46 minutes ago, makc said:

Так это не сработает в ПЛИС, у которых вся прелесть в однородной структуре. Получится, что все асинхронные фифошки будут жёстко прибиты к определенному месту/местам на кристалле и это крайне неудобно.

Как раз такой метод и используется как минимум в нескольких последних семействах Xilinx ... Оптимизировано для CDC на высоких частотах

-

4 hours ago, Plain said:

Уже говорил в других темах, здесь явно какая-то политика, потому что есть куча способов сделать устойчивый триггер

Поделитсь способами?

Да и бесплатного "сыра" почти не бывает, любая оптимизация под что-то одно обычно идет за счет чего-то другого ...

-

1 hour ago, yes said:

а какие конкретно? я не одобряю этого, но хотелось бы знать...

Последние Vivado вроде как.

-

18 minutes ago, Jackov said:

Да это всё понятно. Вопрос в том чтобы пробросить третье состояние вывода по модулям вверх по иерархии.

Проброс tristate идет через порты inout, как у вас во втором примере.

-

43 minutes ago, _4afc_ said:

Про структуры не знаю, а просто wire из субмодуля доставался и в Modelsim и имплементировался в GoWin на verilog.

Это не структуры, это доступ по иерархии к сигналам, таскам и функциям внутри дизайна в симе. Причем `OR1200_TOP, `CPU_cpu, `CPU_rf, это макросы которые задают актуальное имя инстанса top в TB и cоответвенно модулей внутри топа.

В синтезе раньше поддерживался доступ по иерархии в пределах модуля. Например доступ к сигналам внутри именованного блока begin end в generate.

В последнее время ряд синтезаторов начали ограниченно поддерживать и кросс-модульный доступ по иерархии. -

4 hours ago, addi II said:

gpr = `OR1200_TOP.`CPU_cpu.`CPU_rf.rf_a.get_gpr(gpr_no);

Иерархический доступ возможен только при компиляции в симуляторе.

-

1 minute ago, andrew_b said:

Там нет ASYNC_REG, насколько помню.

Зато там есть:

Quotealtera_attribute = "-name SYNCHRONIZER_IDENTIFICATION FORCED_IF_ASYNCHRONOUS; SUPPRESS_DA_RULE_INTERNAL=R102; SUPPRESS_DA_RULE_INTERNAL=R101"

-

3 minutes ago, andrew_b said:

Про Xilinx это всё хорошо. Но насколько я помню другие темы этого автора, он использует Альтеру.

В Altera/Intel все тоже самое ...

-

Вот собственно все актуальные (UG835 (v2023.2) October 18, 2023) рекомендации из доки для report_synchronizer_mtbf

QuoteAsynchronous clock domain crossings (CDCs) can fail due to metastability as data is captured asynchronously and may settle to different values on different loads in the circuit. Synchronizer registers are used to improve overall circuit reliability for designs which contain multiple clock domains, in which asynchronous data transfers occur, or in which external asynchronous signals are captured with an internal clock. A synchronizer chain consists of two or more registers connected sequentially with the first stage capturing the data signal from the asynchronous clock domain. The successive register stages provide additional settling time for metastable events and increase MTBF. The synchronizer registers must have ASYNC_REG properties with values of TRUE. Besides reporting MTBF, the ASYNC_REG properties instruct synthesis, simulation and implementation tools to optimize for increased MTBF and improve overall behavior of the synchronizer circuit

и никакой "полу-асинхронщины" ...

-

6 hours ago, des00 said:

самый лучший вариант из первых рук: сгенерировать xilinx gtp/gtx с полным обвесом и отреверсить) где то года с ~2019 там стали использоваться занятные переходы между доменами, которые до этого момента делались по другому.

Ох уж эти переходы в GTP/GTX ... Вот как раз с ними приходится сейчас разбираться так как они ломают все DRC которые сами же Xilinx и пишут.

И я не увидел там ничего "полу-асинхронного", обычные цепочки триггеров с кучей потенциальных проблем. Но поскольку в большинстве этих проблемных мест входное toggle-rate мизерное поэтому IMHO разработчики и забили на возможные глюки. Как и на другие глюки которые судя по всему проявляются в редко используемых конфигурациях ...

А для проверки надежности используемых решений CDC в Vv есть report_cdc и report_synchronizer_mtbf. Очень бывает поучительно посмотреть получаемые циферки для разных решений.

-

On 10/29/2023 at 8:04 AM, jenya7 said:

и всё таки даже сейчас раз в 4000 - 80000 обращений одно ломается. правда последующие отрабатываются нормально до следующей поломки.

А сигнал SPI_CS тоже асинхронный с внешнего пина? И тоже без синхронизации? ...

Реализация кольцевого буфера

в Языки проектирования на ПЛИС (FPGA)

Опубликовано · Пожаловаться

Прежде чем беспокоить DSP или зазря переписывать always есть смысл посмотреть логи и понять что же является узким место в плане времянки.

Из приведенного куска кода вопрос может вызывать только

assign last_out = (read_ptr == write_ptr - 1) ? 1'b1 : 1'b0;Так как сравнении идет с не с регистром, а с разностью - и это может влиять на времянку.