LeonY

Админ-

Постов

661 -

Зарегистрирован

Весь контент LeonY

-

Yes, it works. Thanks

-

-

Похоже edit работает и для PLL. Не знаю что я делал неправильно, но все заработало.

-

Не понял вопроса 🤔. Если есть simulation model (или behaviour model), а она должна быть в simulation folder, создаю testbench, все это гружу в Modelsim ну и далее по стандартному сценарию. Проблема в том, что почему-то Megawizard не создаёт simulation model, хотя должен и раньше все работало на ура

-

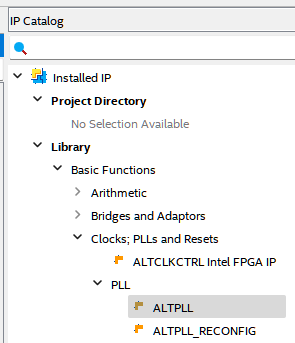

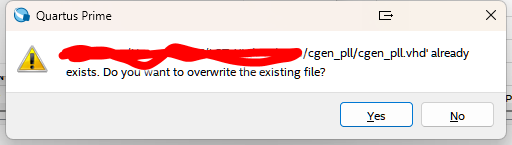

Нужна помошь коллективного разума. Ниже собственно вопрос на английском - это копия с моего-же поста в Intel Support и очень лень переводить: I'm running Quartus 18.1 Std and the project is targeted to MAX10 device. I need to use ALTPLL from the standard IP Catalog. On the previous Quartus versions I used Megawizard to configure/instantiate the IP, now Quartus is doing the same from the IP Catalog itself and starts Megawizard in the background. It's fine. It generates *.cmp, *. ppf, *.qip and *.vhd as expected. My problem is the absence of a simulation model for Modelsim. I don't see any options to tell the "Megawizard" to do it. The second "Megawizard" related question is "How to edit previously created/configured/instantiated IP?". Based on my previous experience the Megawizard had File-Open command. Now I don't see how to do the task. Please assist.

-

Variant Manager

LeonY опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Прошу помощи гуру: Имеется плата на которой стоит микропроцессор (точнее SoC) с набором периферийных устройств, FPGA ну и еще всякое "по мелочам". Планируется производить плату для разных клиентов в различных конфигурациях: - микропроцессор в 4-х различных реинкарнациях - FPGA в 4-х различных реинкарнациях - SSD 3 варианта размера - DDR микропроцессора - 2 варианта размера - DDR FPGA - 2 варианта размера - и т.д. и т.п. Количество возможных вариантов зашкаливает и поддерживать их вручную выглядит не слишком реальным. Попытка работать с Variant Manager успехом не увенчалась из-за принятой в компании структуры библиотек и дебильности VM. У нас в CL хранится минимальное количество символов (1 резистор, 1 конденсатор and so on), а все остальное берется из DxDatabook. Похоже, что Variant Manager не поддерживает работы с DxDatabook и категорически отказывается подменять атрибуты при замене типа компонента (Manufacture Part Number). Соответственно неправильно генерируются BOMs. И все... Есть ли какой-то выход из этой дурацкой ситуации? Может мы делаем что-то не так (изменение CL не предлагать)? Может задачу можно решить каким-нибудь не-менторовским софтом? Заранее благодарен за помощь. -

Intel Apollo Lake IoT вопросы

LeonY ответил LeonY тема в Все остальные микроконтроллеры

Не может быть!!! Вопрос задан для тех, кто знает Интеловские процессоры, а не для произнесения пустых звуков. Sorry ... -

Intel Apollo Lake IoT вопросы

LeonY ответил LeonY тема в Все остальные микроконтроллеры

Конечно есть - иначе нафига бы мы это делали -

Intel Apollo Lake IoT вопросы

LeonY опубликовал тема в Все остальные микроконтроллеры

Занимаюсь запуском платы на Intel Apollo Lake IoT (семейство E39xx, в частности первая плата на E3940). Уткнулись в следующую проблему: BIOS должен грузиться с SPI Flash, что и происходит. Но очень быстро все умирает, грузится только первый блок (4KByte, на самом деле даже меньше), содержащий параметры Flash памяти, SoftStraps и базовую конфигурацию периферийных устройств. После этого должен быть переход на загрузку BootLoader (address 0x1000), но этого не происходит. Тот же самый BIOS продолжает загрузку как и должнО на 2-х демо платах: Oxbow Hill & Apollo Island. BIOSы с названных плат на нашей ведут себя также как и наш BIOS - затыкаются на начальном блоке. Какие-нибудь идеи??? -

PDF есть, но под NDA. Так что скинуть, к сожалению, не могу. Про DDI я на гугле ничего особенно не нашел, полно инфы про DP, HDMI и т.д. Там действительно упоминается LVDS. Что меня смущает по поводу IO standard - для DP требуются "дикие" частоты (8GHz +) - может ли LVDS тянуть это? В datasheet умный Intel пишет "IO type - Display PHY" и "IO voltage - 1.05V" - понимай как хочешь :(

-

Связка Atom с Cyclone

LeonY опубликовал тема в Работаем с ПЛИС, области применения, выбор

Нужно подключить DDI (Digital Display Interface) с процессора Atom E39xx к Cyclone. Совершенно непонятно какой IO стандарт надо задавать на Cyclone. Может кто-нибудь знает??? -

Makc - спасибо, но, судя по описанию, это не то, что я ищу. Пока безъуспешно борюсь с RefdesPrototype2013_NEW - чего-то оно делает, но не то, что бы хотелось. И логики в действиях выявить не удается :( Может быть кто-нибудь сможет посоветовать Settings, чтобы делать следующее: - никаких префиксов-суффиксов не добавлять (это работает) - нумеровать в пределах листа (вроде тоже работает) - нумеровать сверху-вниз ("по столбцу") - нумеровать слева-направо ("по строке")

-

Вроде то что надо, хотя пока не понял как заставить скрипт делать то, что нужно. Буду разбираться...

-

Как придать порядок RefDes в DxD

LeonY опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Пожалуйста на пинайте ногами за дурацкий вопрос, который, я уверен, обсуждался неоднократно - просмотреть все темы в разделе просто нереально. Вопрос такой - как заставить DxD расставлять RefDes хоть в каком-нибудь порядке (сверху вниз - слева направо или слева направо - сверху вниз). В данный момент речь идет о новом проекте, где надо нумеровать все подряд. В дальнйшем, конечно, понадобится и корректная нумерация добавленных компонентов. Но сейчас, хотя-бы, первая задача. Заранее спасибо -

Спасибо - очень интересная информация. Какой порядок цен? Есть ли IBIS модели?

-

DDR3L ECC - возможные конфигурации

LeonY опубликовал тема в Цифровые схемы, высокоскоростные ЦС

Занят разработкой платы, которая должна содержать 1 или 2 канала 72-битных DDR3L памяти (64 бита + ECC). Плата очень маленькая (размер кредитки) и поэтому приходится экономить место. Дальше буду писать об одном канале - для второго все аналогично. Просматривается 3 возможных архитектуры: - 9 8-ми битовых кристаллов; все стандартно - должно работать, но занимает до фига места - 4 16-ти битовых кристалла + 8-ми битовый для ЕСС (естественно с теми же таймингами) - будет ли работать? Вариант не идеален с точки зрения приобретения, но как-бы это не моя проблема. - 5 16-ти битовых кристаллов, где один будет использован только на половину ширины DQ шины - будет ли работать? Каких еще подводных камней можно ожидать? -

Мыша и DxDesigner

LeonY ответил LeonY тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Спасибо !!! :a14: -

Мыша и DxDesigner

LeonY опубликовал тема в Siemens EDA - Xpedition, PADS (ex. Mentor)

Мне приходится все время прыгать по множеству разных програм и только в DxDesigner реакция на колесо мыши совершенно отличная от всего остального. Можно ли заставить DxDesigner работать "по-человечески": ну что-то типа Cntrl-WheelUp -> ZoomIn Cntrl-WheelDown -> ZoomOut WheelUp -> ScrollUp (PanUp) WheelDown -> ScrollDown (PanDown) WheelLeft -> ScrollLeft WheelRight -> ScrollRight А то достало... -

Windows 7

LeonY ответил LeonY тема в Операционные системы

Это точно НЕ железо - видна рамка окна, иногда фон заполнения, только часть площади окна мигает, а не весь экран. А чем можно мониторить запущенные/запускаемые процессы? Посмотрел Sysinternals, у них полно какого-то софта с очень похожими названиями - что именно использовать? Спасибо - попробую -

Windows 7

LeonY опубликовал тема в Операционные системы

Скорее всего пишу не по профилю раздела, но "общий треп" отсутствует, так что срашиваю здесь. После очередной установки седьмой Выни возникла очень странная проблема, которой раньше никогда не было и упоминаний о чем либо подобном я нигде не встречал. Проблема не катастрофическая, но раздражает капитально. Попробую описать конфигурацию системы и саму проблему ниже: Железо (цетральная часть - ессесно вокру еще всякого барахла куча): MB: P8P67 Deluxe CPU: i5-2500K RAM: 8GB Video: ATI Radeon HD5670 Monitor(s): 2 штуки Dell 1200x1600 на DVI Soft: Win 7 x64 Ultimate SP1 со всеми заплатами Все последние версии дров Исчо куча всего разного Проблема: На вторичном мониторе в его нижней части время от времени выскакаивает какое-то окошко. Пишу "какое-то" не потому что не могу понять что за оно, а потому что прочитать невозможно - время его наличия ничтожно - вспышка. Выглядит это, если не пялиться прямо на монитор, именно как вспышка (вначале даже подумал, что это броски по питанию). Происходит это не всегда - при некоторых загрузках все нормально, так, например, вчера весь день проработал без этих миганий. Хотя это, наверное, ни о чем не говорит - похоже, что положение этого окна самопроизвольно меняется и оно могло просто уползти за границу экрана. Поубивал почти все background apps - ни фига не помогает; что смог, поубивал в сервисах - никакого эффекта. В попытках выяснить чё это такое, запустил видео-захват экрана (SnagIt) - ни фига не видно, чистый экран. Вот тут и обращаюсь к сообществу - какими средствами можно: - выяснить что это за такое??? - УУУУБББИТЬ???? Любые другие идеи - Welcome as well!!!! -

Altium 10

LeonY ответил Ilia тема в Altium Designer, DXP, Protel

А акции все продолжают падать.... хотя, казалось бы, дальше уже некуда :( -

Специфический Crossbar Switch

LeonY опубликовал тема в Работаем с ПЛИС, области применения, выбор

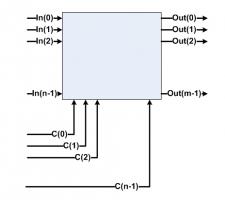

Вдруг возникла на первый взгляд простейшая задача, но при попытке реализации "уткнулся в стену" - ничего разумного в голову не приходит :twak: . Может у кого-то что-то подобное уже было (есть) или будут удачные мысли . Задача в следующем: - есть черный ящик с n входами In(0) ... In(n-1) m выходами Out(0) ... Out(m-1) m всегда меньше n n-битовая управляющая шина C(0) ... C(n-1) количество активных ("1") бит на шине С всегда меньше или равно m (если это не соблюдается, то желательно выставлять сигнал ошибки, но это не проблема) - требуется для каждого активного бита из С (например C(k)) подключать соответствующий вход In (в данном случае In(k)) к любому из выходов Out (я написал к "любому", но можно и более определенно - если C(k) является наименее значимым (LSB) из всех активных битов - то подключать к Out(0), для следующего активного бита - к Out(1) и так далее, хотя это несущественно). Реальные значения для моей задачи таковы: - максимальное n - 32 - максимальное m - 8 - ширина шин In и Out - 64 бита (а может и 72 - пока не решил) Хочется все это сделать на комбинаторной логике, а не на State Machine - второй вариант тривиален, но потребует буферирования на FIFO всех 32-х входных каналов, чего хочется избежать любыми способами из-за ограничений силикона, и достаточно экономично (по тем-же причинам). Но на данный момент я не могу придумать не только экономичного решения, но вааще никакого, так что :help: -

Это уже что-то. Сейчас начну задавать глупые вопросы: - можно ли получить на схеме (автоматом, внеся "праильные" Links) с помощью Add Suplier Links что-то подобое? : U1 +---------+ | | | | | | | | +---------+ abc123xyz nkt785sdf-01 za0445fd где U1 - элемент; abc123xyz, nkt785sdf-01, za0445fd - эквивалентные замены (предполагаем, что SCH Symbol & PCB Footprint одни и те же для всех замен) - будет ли генерироваться автоматически BOM, похожий на картинку ниже?: Ref | Manuf. | Manuf. |Comp. |Qty. | Des | PN | |# | | ___________________________________________________________________ U1 abc123xyz TI 01123 1 nkt785sdf-01 Fairchild Semi 56783 za0445fd LT 90871 ___________________________________________________________________ ну это типичный пример Variant

-

ну это мы уже обсудили - совместимость оставим разработчику... и не только BOM. про симуляцию я уже писал, и этот путь скажется отрицательно на всех Downstream операциях а можно подробней про Add Suplier Links - как это может решить проблему??? Не решение!!! я имею ввиду случай, когда замена компонента не порождает новый Variant, т.к. все замены "равноценны", и что именно ставить не есть проблема разработчика, а производства, точнее - снабженцев