-

Постов

181 -

Зарегистрирован

-

Посещение

-

Победитель дней

5

Variant99 стал победителем дня 15 июля 2023

Variant99 имел наиболее популярный контент!

Репутация

-7 ПлохойИнформация о Variant99

-

Звание

Частый гость

- День рождения 9 декабря

Посетители профиля

Блок последних пользователей отключён и не показывается другим пользователям.

-

EGR - регистр принудительной (программной) генерации событий. Вот что говорит манулал по этому поводу: Bit 1 CC1G: Capture/Compare 1 generation This bit is set by software in order to generate an event, it is automatically cleared by hardware. 0: No action 1: A capture/compare event is generated on channel 1: If channel CC1 is configured as output: CC1IF flag is set, Corresponding interrupt or DMA request is sent if enabled. If channel CC1 is configured as input: The current value of the counter is captured in TIMx_CCR1 register. The CC1IF flag is set, the corresponding interrupt or DMA request is sent if enabled. The CC1OF flag is set if the CC1IF flag was already high. Bit 0 UG: Update generation This bit can be set by software, it is automatically cleared by hardware. 0: No action 1: Reinitialize the counter and generates an update of the registers. Note that the prescaler counter is cleared too (anyway the prescaler ratio is not affected). The counter is cleared if the center-aligned mode is selected or if DIR=0 (upcounting), else it takes the auto-reload value (TIMx_ARR) if DIR=1 (downcounting). Бит 1 CC1G: генерация захвата/сравнения Этот бит устанавливается программно для генерации события, он автоматически сбрасывается аппаратно. 0: нет действия 1: Событие захвата/сравнения генерируется на канале 1: Если канал CC1 сконфигурирован как выход: Флаг CC1IF установлен, соответствующее прерывание или запрос DMA отправляется, если включен. Если канал CC1 сконфигурирован как вход: Текущее значение счетчика фиксируется в регистре TIMx_CCR1. Флаг CC1IF установлен, соответствующее прерывание или запрос DMA отправляется, если включен. Флаг CC1OF устанавливается, если флаг CC1IF уже был высоким. Бит 0 UG: Генерация обновления Этот бит может быть установлен программно, он автоматически сбрасывается аппаратно. 0: никаких действий 1: Повторная инициализация счетчика и обновление регистров. Обратите внимание, что счетчик предварительного делителя также очищается (в любом случае коэффициент предварительного делителя не затрагивается). Счетчик очищается, если выбран режим выравнивания по центру или если DIR=0 (прямой счет), в противном случае он принимает значение автоматической перезагрузки (TIMx_ARR), если DIR=1 (нисходящий счет).

-

О боже, что это? 🥵 альтернативная вселенная? Я никогда не видел такой формы записи кода. А скажите, автор сам это хоть как-то понимает? Я вот чисто по памяти опознаю CR1: 0001 - это TIM3->CR1 = TIM_CR1_CEN

-

STM32 нужна помощь с кнопками

Variant99 ответил MaximDV тема в ARM, 32bit

Так не ставьте кондеры по 47 мкФ, чтобы не было больших токов разрядки. -

Если бы jcxz хоть раз делал бы частотный привод, он бы знал, "насколько оперативно" надо :))) А коль спрашивает - значит не делал. :)))

-

А один участвующий поцык тут обещал "~1 такт (ARM)" 🙂 А тут уже и 8, и 30 тактов. Эх, вот так и верь ...

-

Так это ж алгоритм DDS

-

Энкодер как бы намекает на то, что это будет частотный привод для асинхронного трехфазного электромотора. Энкодер позволяет расширить диапазон регулирования скорости вращения.

-

С импортозамещением на STM32 будет туго. 😄 Это еще хорошо, что ST Microelectronics не сделала так, как Analog Devices или Texas Instruments, и не закрыла доступ к документации и сайту в целом, а ограничилась только закрытием скачивания ПО. Так что тут лучше объяснять просто желанием самостоятельно участвовать в процессе, а не тупо прикручивать скотчем готовые куски. Тем более, что это будет то же самое, только сделанное самим. А это тоже немаловажно для чисто творческого процесса. Потому что если не делать самому, то еще проще - взять на той же Алишке готовый частотник и вообще не париться изобретениями того, что уже вообще было сто раз сделано.

-

Спецам по MIDI протоколу. Аккорды

Variant99 ответил Trashy_2 тема в В помощь начинающему

Аккорд - это одновременно взятые три или более ноты. В MIDI нет специальной команды для описания аккорда (нескольких нот), а значит, аккорд образуется передачей последовательно трех-четырех команд NoteOn. Да, возможно, нужно перед этим отправить команду Poly On.- 4 ответа

-

- 1

-

-

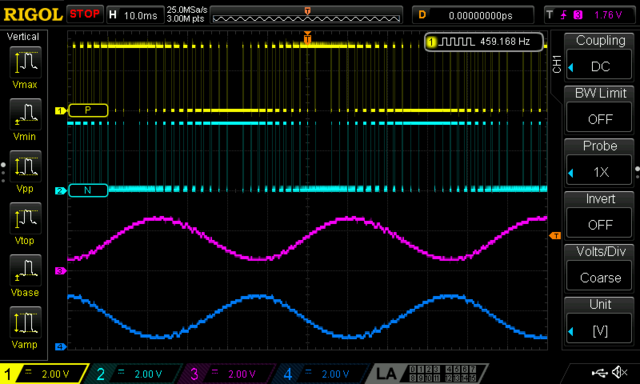

Да всё нормально делает топикстартер. Он просто вначале сумбурно описал хотелки, я тоже мало чего понял вначале, какие там "треугольники" и что конкретно не получается. Но на последней его фотке видно, что он получил. И как оказалось, всё в поряде изначально, просто на осцилле неверно настроил захват сигнала и картинка неверно его информировала. Так что всё норм. Ширина импульса меняется по синусоидальному закону, с тем, чтобы на выходе ШИМ поставить RC-фильтр и получить отфильтрованнное напряжение, изменяющееся по синусоидальному закону. Вот типа такого: Топикстартер использует три канала, это наводит на мысль, что он пытается крутить трехфазный BLDC-моторчик.

-

А, ну дак время развертки на осцилле у вас короче, чем интервалы изменения ШИМа. Я уж было достал плату и анализатор, показать на деле...

-

Да без вопросов, конечно можно. Однако, если использовать таблицу только на четверть периода, то не получится - DMA считать назад не умеет, да и проводить вычитание константы тоже нет. Ну и автор сказал, что он хочет вычислять значение в каждом шаге, потому что значения в формуле могут меняться. В принципе, его право, пусть делает как хочет.

-

Во-первых, можно писать просто TIM1->SR = ~TIM_SR_UIF; там для сброса бита имеет значение только 0, запись 1 на биты не влияет никак, поэтому выполнять &= не нужно. Во-вторых, добавьте после этой строчки еще несколько строчек прог.кода или просто __NOP(); Такое поведение известно с таймерами. А если в обработчике шагаете по шагам, то пока вы шагаете, интервал времени проходит и успевает выставиться новое прерывание. Чтобы этого не происходило, можно в регистре DBGMCU включить бит DBG_TIM1_STOP для остановки таймера во время пошаговой отладки.

-

правда-правда. Вначале посмотрите, что там написано, потом будете писать очередную глупость. Автор конечно написал мессагу так, что ничего непонятно, какие "треугольники счета" и что именно не получается. Возможно, невыставленный бит предзагрузки OC1PE, возможно, слишком долго идет расчет флоатов, возможно, вообще неверно построил алгоритм. Нет особого смысла высчитывать в каждом приращении угла синусоиды новое значение, можно брать из заранее просчитанной таблицы для периода. Или полупериода. Или даже четверти периода. Функция то симметричная по двум осям. Перезаписывать новым значением регистр CCR1 нужно с частотой шагов приращения угла синуса, то есть, от второго таймера, задающего частоту синусоидального сигнала, получаемого в результате фильтрации ШИМ. Вообще, ШИМ - это ШИМ. Его частота - это частота ШИМ, влияющая на фильтрацию выходного сигнала. А частота синусоидальной огибающей выходного сигнала, получаемого после фильтрации ШИМ - это уже другая частота, она не связана с частотой ШИМ. Вернее, она конечно может быть кратна ей, но это частный, необязательный случай.

-

Заранее обсчитайте таблицу синуса, заполните массив. А потом подставляйте в CCR1 значения из этого массива, по событию (прерыванию) обновления счета. При этом, должна быть включена буферизация записи CCR. Ввиду того, что расчет синуса занимает много процессорного времени, таблицу желательно иметь заранее сгенерированную.