-

Постов

9 -

Зарегистрирован

-

Посещение

-

Nik99997 изменил фотографию своего профиля

-

Скорее всего Вы правы, благодарю

-

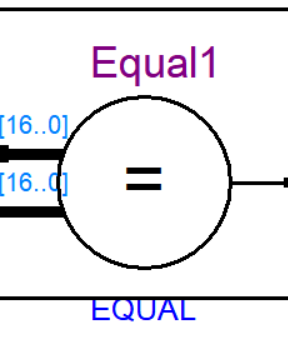

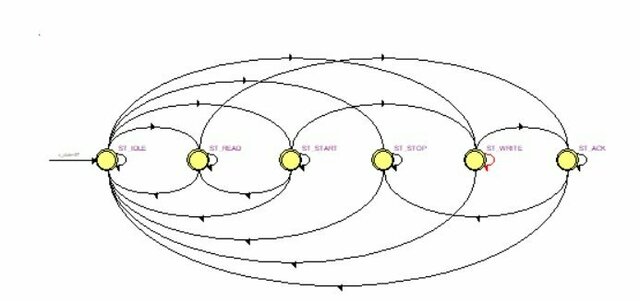

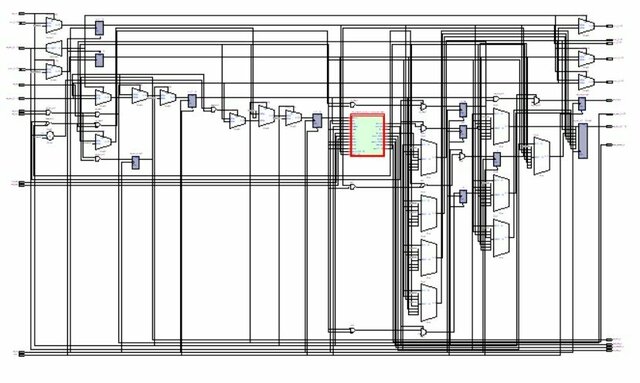

На базе всемозможных логических вентилей: И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и тд; D-триггеров, которые будут составлять регистры; мультиплексоров; дешифраторов; сумматоров. Касаемо элемента во вложении не могу сказать, что это конкретно, но он тоже входит в состав схемы. Подключение должно быть таким же как в проекте и с теми же входами и выходами.

-

Возможно ли тогда в каких то других программах схемотехнического моделирования это реализовать, если в Micro-Cap не выйдет?

-

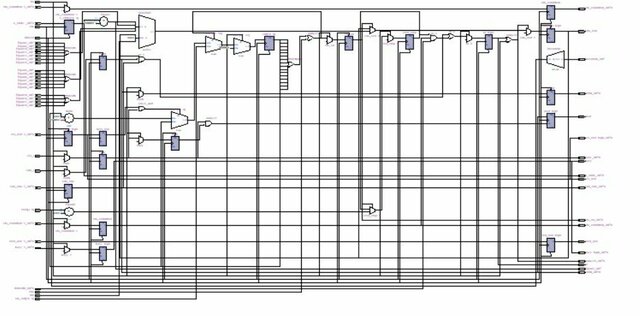

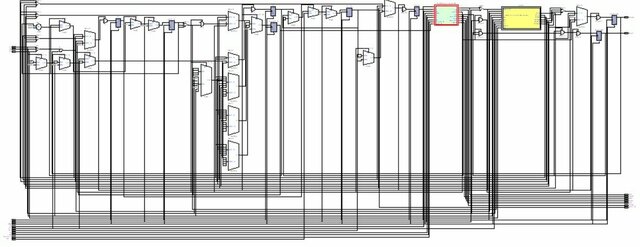

Добрый день! Необходимо перечертить схему протокола передачи данных I2C (i2c master core) из проекта Quartus в Micro-Cap. Пытался сам, ничего не выходит. Ряда элементов не было в библиотеке элементов в Micro-Cap, либо я не нашел их сам. Есть готовый проект в Quartus. Открыв RTL Viewer, можно увидеть саму схему. В ней присутствуют триггеры, мультиплексоры, обычные лог вентили и пр. Также есть макроблоки со схемами внутри. Один из макроблоков составляет граф цифрового автомата, судя по всему его надо реализовать в виде логической схемы, а затем собрать в макроблок с соответствующими входами и выходами. После того как будет собрана схема, в Micro-Cap надо будет ее промоделировать и сравнить с результатами моделирования в ModelSim. Возможно ли вообще такое сделать? Во вложении сам проект и скриншоты схем. i2c .zip

-

Хочу данную схему перерисовать в Micro-Cap и также промоделировать ее, посмотреть что получится. Хорошо, еще раз очень Вам благодарен) и с майскими праздниками! Из чего то подобного знаю только высказывание г.Форда "Время не любит, когда его тратят впустую"), а конкретно в Вашей формулировке даже и не могу сказать автора, к сожалению)

-

Благодарю за помощь! Сильно выручили) Сама схема у меня получалась следующая (вложение) Только вопрос: как из этого архива запустить проект, через какой файл? Или надо по новой его собирать? Возможно я что-то не понимаю, либо же путаю

-

С этим будет сложновато. Может проще использовать второе вложение? Чистый исходник, без собранного проекта? И по новой его собирать и моделировать? Также по инструкции с интернета собирал проект в Quartus на основании 2го вложения (из папки i2c-rtl-verilog (5 файлов)). В виду чего образовался следующий каталог с папками и файлами. (db, incremental_db, simulation) ____________________________________________________________________________________ 1) Simulation - это мои тщетные попытки произвести моделирование (естественно безуспешные) 2) incremental_db - дополнительная база данных, которая содержит информацию о датах модификации файлов и о том, откуда взялась определенная логика. Это используется функцией "Быстрая перекомпиляция", чтобы пропустить шаги обработки, ввод которых не изменился. (сам этого не знал, погуглил назначение данной папки) 3) Насчет папки db могу сказать следующее (опять же погуглил): База данных - это внутреннее представление проекта, которое используется компилятором. quartus_map Программа считывает входные файлы и сохраняет их содержимое в базе данных. После считывания всех входных данных те компоненты, которые фактически использовались, копируются в отдельную область внутри базы данных, представляющую весь проект. На этом представлении выполняются оптимизации, такие как распространение постоянных сигналов и удаление неиспользуемых выходов. Затем quartus_fit программа принимает это представление и находит отображение на фактическое оборудование. Затем это отображение записывается обратно в базу данных. quartus_asm Программа извлекает данные отображения из базы данных и генерирует файлы программирования. Поскольку формат базы данных является внутренним, его можно довольно хорошо оптимизировать, что экономит немного времени при компиляции. ____________________________________________________________________________________ i2c_master.qpf - сам проект Quartus, через него м запускаю проект и через Tools-NetList Viewers-RTL Viewer получаю принципиальную схему. Единственное что странно, почему у меня там два одинаковых исходных файла "i2c_master_top.v". Это объяснить не могу. Это все что могу Вам сообщить, сам мало чего знаю. Извиняюсь.

-

Во вложении. Это уже то, с чем работаю (i2c_master.rar). Также прикрепляю исходник с testbench (i2c.rar) i2c_master.rar i2c.rar Благодарю за совет

-

Добрый день! Скачал с сайта OpenCores проект по протоколу I2C (файлы Verilog для Quartus и testbench для ModelSim) Сам проект собрать вышло и скомпилирована схема принципиальная. Самая сложность возникает с получением временных диаграмм. Пытался внедрить ModelSim в Quartus по статьям из интернета, ничего не получается. Выдает ошибку под конец (Во вложении скрин) Подскажите как можно решить эту проблему и наконец уже промоделировать данный проект) Заранее благодарю. Сам просто новичок мягко говоря.