Alex77

-

Постов

721 -

Зарегистрирован

-

Посещение

-

Победитель дней

1

Сообщения, опубликованные Alex77

-

-

SVN

У Xilinx есть, до кучи, как цеплять разные системы

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

Мож не в тему - однако по пробовал в TCL консоли в открытом проекте в вивадо 2017.4.1

set proj_name [current_project]

get_property directory $proj_name

Оно выдало путь до места где расположен XXX.XPR

Что я делаю не так ?

Теперь понял - Спасибо.

А вот хотелось бы все-таки узнать, если ли возможность изнутри прошивки узнать part-номер ПЛИС, на котором данная прошивка крутится.Кто-нибудь знает?

глубоко не копал - может стоит посмотреть в сторону ICAP ? (или как там его? для частичной реконфигурации ПЛИС). к примеру ug470

-

Здравствуйте!

Использую вивадо на удаленном сервере, на рабочем компе нет САПР, на нем Ws10

Вопрос что можно использовать в свободном доступе для программирования Artix-7

Пробовал безуспешно с последним IMPACT для спартана и с Chipscope Pro

Однако...

Я не уверен (не пробывал) "IMPACT для спартана" для "Artix-7" вообще как класс.

и с другой стороны Это вроде как раз по теме:

"Vivado Lab Solutions - 2017.4 Full Product Installation Important Information

Vivado Lab Edition is a new, compact, and standalone product targeted for use in the lab environments. It provides for programming and logic/serial IO debug of all Vivado supported devices. Lab Edition requires no certificate or activation license key.

Vivado Hardware Server enables Vivado Design tools to communicate with a remote target system."

-

Подскажите, плиз, где можно взять (скачать) проверенную версию Vivado +System Generator, чтобы гарантированно работала эта связка. Заранее благодарен!

Все версии Vivado можно "найти" на сайте Xilinx - это по поводу "где".

По теме "гарантировано" качать по очереди и проверять, начиная с крайней свежей.

Это при условии гарантировано "правильного исходного текста проекта".

-

Vivado Design Suite - HLx Editions: Update 1 - 2017.4

Vivado Design Suite 2017.4 Update 1 is now available with support for

Production Devices

Zynq UltraScale+ MPSoC (-1L/-2L) Devices

ZU4CG/EG/EV, ZU5CG/EG/EV, ZU7CG/EG/EV, ZU11EG

Kintex UltraScale+ FPGA (-1L/-2L) Devices: - KU11P

Virtex UltraScale+ FPGA (-3) Devices:

VU11P, VU13P

Devices enabled in WebPack:

XC7A25T, XC7A12T, XC7S25, XCZU4 EG/CG/EV, XCZU5 EG/CG/EV, XCZU7 EG/CG/EV

For customers using these devices, Xilinx recommends installing Vivado 2017.4.1. For other devices, please continue to use Vivado 2017.4.

NOTE: This update must be applied to an existing installation of Vivado 2017.4. After updating, the Vivado version will be 2017.4.1.

-

Коллеги, досталась мне плата HTG-707 от хайтек глобал. К сожалению без документации. Писал в саппорт - благополучно отфутболили. Может у кого есть юзергайд на эту плату? Поделитесь пожалуйста.

ОФФТОП

-

Всё качается и ставиться в частности под вин10.

-

Добрый день. Работаю с прерываниями в microblaze на отладочнике Spartan3e. Прерывания формирую от дип-переключателя на плате. Подтверждение прерывания вывожу через uart на ноут. Проблема в следующем: прерывания происходят и по фронту и по спаду. Я так понимаю, что контроллеру без разницы. Он реагирует только на изменение состояния?

"дип-переключателя" имеют славную традицию "звенеть" - как следствие куча сигналов прерываний.

-

Всё, что мне нужно - это операция (2x+1), инкремент и сумма двух чисел.

Я уже сказал, операция 2x + 1 на логике в любом случае будет быстрее, так как это можно сделать за единицу времни. Т.е есть на входе схемы число X из 8000 бит, на выходе X*2+1, простая логическая схема.

Почему-то мне кажется что некорректно описано задание.

"X*2+1" - сиё означает умножение на 2 те сдвиг и пририсовывание бита 1.

Всё это реализуется "статическим сдвигом (т.е. реального сдвига нет)" и добавления вечной 1-цы.

Таким образом схема будет работать на максимальной скорости в 500МГц.

А на словах задание звучит как "А+Б+1".

Что Автору требуется ?

-

Spartan никуда не планируется. Просто есть стартер кит - учусь работать + microblaze.

А как можно посмотреть состояния регистров контроллера прерываний? У меня в дебаггере только регистры самого микроблейза.

Решил забить и скачал ISE 14.7 со стороннего сайта. Там и EDK и Chipscope. На данный момент глюков не обнаружил, чего нельзя сказать о 9.2.

Все регистры отображаются на память, а содержимое памяти можно вывести в окошко просмотра.

С версии 13.1 "поломали" моделирование в моделсиме спартана3е+микроблаз+программа в браме.

Когда починили и если вообще починили я не знаю.

-

У меня отладочный модуль на Spartan3e. Cable USB там на CPLD реализован. Без Chipscopa у меня в дебаггере отображаются только регистры microblaze. А хотелось бы и контроллер прерываний посмотреть.

Сигналы на входе "контроллере прерываний" ? тогда оптимально Chipscop

Если значение регистров "контроллера прерываний" тогда Chipscop не нужен совсем.

ПС: если не склероз вроде как бы не удалось подружить одновременно Chipscop и отладчик Eclipsa Для Microblze.

ПС: в "теории" Spartan3e как бы на последнем издыхании - закладывать его в новое это прямой убыток.

ПС: самое оптимальное для Spartan3e это ISE12.4 всё что надо есть. ise+modelsim+chipscop+sdk+edk

-

И еще один вопрос. В EDK есть возможность подключить в дебаге ядра Chipscope. Но для их использования нужен установленный Chipscope?

Для коих целей?

Если для отладки железа - то не помню.

Если для отладки ПО тамошнего процессора достаточно JTAG (коробка Platform Cable USB) - те Chipscope не требовался.

-

Граждане, а следующая версия будет 17.4, или 18.1?

Где-то можно почитать, что они планируют добавить в следующей версии?

я ставлю на 17.4

скорее всего добавят чипы из cs в продакшен, уберут одни глюки и добавят новых.

-

Использую виртуальную машину на windows 7 64-bit. Запускаю несложный проект, который без проблем выполнялся у знакомых.

Пункт open elaborated design выполняется, а при run simulation появляется окошко:

В чём может быть проблема? Кто-нибудь сталкивался с подобным?

ну так переустановить требуется. криво поставилось. виртуалки иногда глючат.

-

After the update to Windows 10 1709 (Fall Creators Update) starting Vivado aborts with error "R6025 - pure virtual function call".

While this update for Windows 10 is not officially supported with Vivado 2017.3, the following work-around is available:

- Navigate to (Vivado Installed Directory)\2017.3\bin\unwrapped\win64.o

- Backup 'vivado.exe' by renaming it to 'vivado.exe.backup'

- Copy 'vivado-vg.exe' and paste it into the same folder.

- Rename 'vivado-vg - Copy.exe' to 'vivado.exe'

After the above steps are followed, Vivado will launch normally.

PS: Xilinx, Altera, Microsoft и др. все глючат в том или ином виде - давайте жить дружно.

-

https://www.xilinx.com/support/documentatio...all-license.pdf

Что то замутили с лицензиями - пока не понял.

Device Support

The following devices are in production:

Zynq UltraScale+™ MPSoC:

XCZU11EG (-1, -2)

Kintex UltraScale+:

XCKU11P (-1, -2)

XA UltraScale+ MPSoC:

XAZU2EG and XAZU3EG (-1Q)

Spartan-7

XC7S50 (-1Q)

XA Spartan-7

XA7S50 (-1Q)

Additional devices introduced in this release

Zynq UltraScale+ MPSoC:

XCZU4EV/CG/EG, XCZU5EV/CG/EG, XCZU7EV/CG/EG

XA Zynq UltraScale+ MPSoC:

XAZU4EV and XAZU5EV

Spartan-7

XC7S25

Artix-7

XC7A12T

New Avalon to AXI bridge IP.

-

Пробовал. Не помогает.

вивадо полная? не вебпак?

все файлы с лицензиями поместите в корень c:\.xilinx

и чтоб без "+" итд.

???

-

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

Здравствуйте!У меня вопросы к разработчикам на ПЛИС Altera.

На сайте у них заявлено средство HLS Compiler.

Хотелось бы знать, это часть Quartus Prime или отдельная среда?

Доступна ли она сейчас?

Где про нее можно почитать (ничего кроме ссылки на платные курсы и двух документов по несколько страниц у меня найти не получается)?

Спасибо!

Я конечно слепой... :rolleyes:

но на указанной выше странице есть КНОПКА на пол экрана, где написано что для "Доступа к бета версии над обратиться к дилерам"

позвоните и Вам может быть расскажут всё.

удачи.

пс: что такое "HLS Compiler" можно посмотреть и пощупать живьём у xilinx в vivado 2016.4

-

-

-

Можно и не ждать

В полдень ещё не было... :crying:

У них ещё ночь была. Сейчас они вышли на работу...

-

Ждём релиз.

А пока читаем что "нового"

https://www.xilinx.com/support/documentatio...all-license.pdf

-

Перешел на 2016.4_0124_1 с 2015.2.

Про стабильность - вылетел один раз просто сам по себе, когда я пиал HDL.

По времени компиляции - оно тормознутее чем 2015.2. Проект толком не разводится, время компиляции увеличилось на 30 мин ~50 %.

Думаю вернуться на 2015.2, и со временем свалить на Альтеру.

может просто проект несколько не удачно написан ?

-

Господа! Нужна срочная помощь! Замучились уже!

Квартус версии 13.0.1, лицензионный, стоит на новом ноуте с 10ой виндой. У компа какие-то есть определённо проблемы с видеокартой, или с дровами для неё, но в остальных программах со шрифтами всё нормально. А в Квартусе вот - как на картинке. В лучшем случае срезаются концы последних символов, в худшем - вообще целый символ. Как я понимаю, у Квартуса неправильная информация о размерах шрифта. Перерыли весь Инет, чего только не делали: меняли все шрифты в самом Квартусе, меняли шрифтовые настройки в винде, пытались шрифты скормить из предыдущих версий виндовозов - не в какую!

Ну наверное же кто-то сталкивался с таким, помогите, плиз!

масштабирование в виндах включено ? те не 100% а к примеру 150% ?

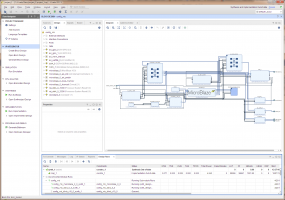

Система контроля версий для FPGA проектов.

в Среды разработки - обсуждаем САПРы

Опубликовано · Изменено пользователем Alex77 · Пожаловаться

smartsvn

или

консольные команды svn.exe