TSURKOV

Участник-

Постов

38 -

Зарегистрирован

-

Посещение

Весь контент TSURKOV

-

QNX отладка

TSURKOV опубликовал тема в Операционные системы

Здравствуйте не могли бы вы поделиться информацией по следующему вопросу. У меня процессорная плата pc104 работаю с ней под qnx4. Мне необходимо научится работать с ней через технологический ComPort (стандартная задача для встраиваемых систем). Я бы хотел иметь полный доступ к процессорной плате, насколько я понимаю, есть терминальные программы позволяющие через внешний компьютер управлять платой. Как они называются? где их можно достать? буду очень признателен за любую информацию по данному вопросу. -

-

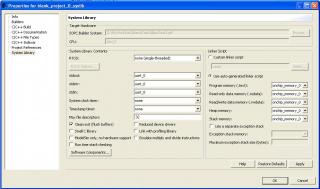

NIOS-UART ?

TSURKOV опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Здравствуйте подскажите пожалуйста в чем может быть дело. Никак не могу заставить работать UART в NIOSII. Открываю документацию раздел UART CORE и вроде, ничего сложного нет, приведены примеры. #include <stdio.h> #include <string.h> int main() { char* msg = "Detected the character 't'.\n"; FILE* fp; char prompt = 0; fp = fopen ("/dev/uart1", "r+"); //Open file for reading and writing fwrite (msg, strlen (msg), 1, fp); } Компилятор выдает непонятную ошибку Unable to reach errno (at 0x00000820) from the global pointer (at 0x000091b4) because the offset (-35220) is out of the allowed range, -32678 to 32767.[/build/nios2/bin/nios2-gnutools/src/newlib/newlib/libc/reent/fstatr.c] blank_project_0 -

Вопрос по организации модулей в VERILOG

TSURKOV опубликовал тема в Языки проектирования на ПЛИС (FPGA)

У меня задействовано два конечных автомата, находящихся в двух раздельных модулях проекта. Эти автоматы должны работать с одной памятью, первый выполняет функции записи в память, второй чтения из нее (память двух портовая). Как описать память или где расположить код ее описания, чтобы к ней был возможен совместный доступ как их одного модуля (файла), так и из другого? -

???????????????????????????????????????????????????????????????????????????????????????????????????? А как быть если в состоянии мне надо совершить только одно действие и затем перейти в другое (например изменение адреса)?В двух разных состояниях выдается два разных адреса?.. Так в чем тогда проблемы? Присваивайте в одном состоянии один адрес, по клоку переходите в другое состояние и выдавайте там новый адрес. ???????????????????????????????????????????????????????????????????????????????????????????????????? Спасибо что откликнулись. Как раз проблема в том, что если я изменяю адрес "adr = adr + 1", в цикле который работает не по клоку а по state регистру "always @ (state) ", адреса многократно меняются, вместо того чтобы один раз переключиться. На каждый конкретный адрес заводить состояние я не могу, слишком их много.

-

Вопрос по АВТОМАТУ в квартусе.

TSURKOV опубликовал тема в Языки проектирования на ПЛИС (FPGA)

В квартусе есть шаблоны автоматов. Как правильно описать автомат в контексте этого шаблона? Первый always цикл принято считать логикой переходов, второй логикой выходов, целиком с этим согласен так путаницы меньше. Меня смущает always цикл выходной логики главным образом то, что он чувствителен не к глобальным тактам синхронизации а к состоянию state регистра. Причем он реагирует не на изменение состояния, а на нахождение в нем. А как быть если в состоянии мне надо совершить только одно действие и затем перейти в другое (например изменение адреса)? Автомат пример которого я привел ведет себя адекватно только если второй цикл как и первый чувствителен к клокам. Но это не в концепции шаблона ! //////////////////////////////////////////////////////////////////////////////////////////////// parameter set = 1'h1, clr = 1'h0; parameter reset_state = 8'd0, wait_byte = 8'd1, read_byte = 8'd2, next_adr = 8'd3, check_adr = 8'd4, idle = 8'd5; reg [7:0] state; reg [7:0] adress_write; reg [7:0] buffer [255:0]; reg rd; always @ (posedge clk or negedge reset) begin if (!reset) state <= reset_state; else case (state) reset_state: if(reset == set) state <= wait_byte; wait_byte: if(rxf == clr) state <= read_byte; read_byte: state <= next_adr; next_adr: state <= check_adr; check_adr: begin if(adress_write < 8'd10) state <= wait_byte; else state <= idle; end idle: state <= idle; endcase end //******************************************************************************** **** always @ (state) begin case (state) reset_state: begin rd = set; adress_write = 8'h0; end wait_byte: if(rxf == clr) rd = clr; read_byte: begin buffer[adress_write] = data[7:0]; rd = set; end next_adr: adress_write = adress_write + 8'h1; endcase end -

Инициализация ROM в квартусе

TSURKOV опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Видел примеры инициализации ROM в книгах НАПРИМЕР $fread(“proga.dat”, mem[0]); ИЛИ readmemb(“proga.dat”, mem); Ни фига они не работают в квартусе. Удалось только создать LPM память в визарде там же ее проинициализировать файлом, и в верилог подключить как модуль. Тогда все ОК. Но я хотел все таки сам ее описать и загрузить как в примерах выше. Возможно ли это в квартусе ??? -

Вопрос по настройкам автомата

TSURKOV опубликовал тема в Среды разработки - обсуждаем САПРы

Господа, подскажите пожалуйста, что означают опции в настройках <Analysis & Synthesis Settings> А именно State Machine Processing: - AUTO - MINIMAL BITS - ONE HOT - USER ENCODED У меня в проекте стояло AUTO и автомат то и дело глючил, поменял на MINIMAL BITS и картина резко изменилась в лучшую сторону почему? -

Как инизиализировать ROM?

TSURKOV опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Господа, подскажите пожалуйста как на Verilog проинициализировать ПЗУ данными из файла. Заранее большое спасибо. -

Уважаемые коллеги

TSURKOV опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Большое спасибо за ваши ответы на прошлый вопрос. Я только начал разбираться с Verilog и вопросов пока много ! Не могу удержаться и хочу спросить вас еще об одной вещи, с которой разбираюсь. Если вам не трудно поделиться своими знаниями и опытом, то еще раз большое спасибо. Я пытаюсь понять как правильней мне привязать некую последовательность действий к событию. Например по ISA я записываю в альтеру байт, который дальше мне надо сдвинуть по SPI. Я подумал что это можно сделать воспользвавшись конструкцией <task> Я подразумеваю что TASK выполняется параллельно начиная с момента вызова и до момента когда он выполнит все свои операторы (как обычная программа). Так ли это? Вызов своего task я планировал делать обработчике always в котором выполняется запись IO регистра, можно ли вызывать задачу на параллельное выполнение и при этом выйти из always? И правильно ли я мыслю решение такой задачи в целом, может ее лучше решать иначе? Если кто может поделиться исходниками примерами работы конструкций <task> буду очень рад. И еще раз большое спасибо всем !!!! -

Вопрос по VERILOG

TSURKOV ответил TSURKOV тема в Языки проектирования на ПЛИС (FPGA)

Увжаемый Gate большое спасибо за ваш отзыв. Я раньше работал с альтерой в схемном режиме, но в душе больше программист поэтому решил заняться верилогом. В связи с этим пока много вопросов. По поводу Initial из ворниногов я понял что квартус его не поддерживает и выкидывает всю конструкцию. Может я не прав? или что-то надо установить? Квартус по описанию, что я приводил выше генерит тригер с еденицей на входе и clk на тактовом входе, отсюда ед на выходе. НО ПОЧЕМУ ???? -

Вопрос по VERILOG

TSURKOV опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Господа подскажите пожалуйста почему не работат эта конструкция. В Quartus в симуляторе на тест сразу лог ед, а я ожидаю что он в начале в нуле потом десять раз проклокает и встанет в ед. ////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// reg test always @ (posedge clk) begin test = 0; repeat(10) @ (posedge clk) begin test = ~test; end test = 1; end ////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////// Заранее большое спасибо !!!!