TSURKOV

Участник-

Постов

38 -

Зарегистрирован

-

Посещение

Весь контент TSURKOV

-

Спасибо за информацию. Уточняю данные по проекту. Работаю с системой на кристале HPS - ARM, Cyclone-V, ОС linux - сборка ядра Angstrom v2013.12 - Kernel 3.10.31 - ltsi - 02861 - g801a40f Прерывание хочу обрабатывать от собственного модуля, подключаемого к HPS по avalon шине (вроде того что в ссылке которую привел в начале)

-

нашел статью с примером https://zhehaomao.com/blog/fpga/2014/05/24/sockit-10.html не получается подключить библиотеки module.h nit.h kernel.h fs.h ioport.h sched.h даже не могу найти заголовочные файлы на диске. Слышал что эти библиотеки входят в состав какой то другой обобщающей библиотеки. Прошу помощи !!!

-

Алгоритм нормировки для ПЛИС

TSURKOV опубликовал тема в Работаем с ПЛИС, области применения, выбор

Здравствуйте Коллеги. Проектирую фазовый детектор. Требуется нормировать отчеты сигнала относительно максимума. Подскажите какой наиболее эффективный алгоритм лучше использовать для реализации на ПЛИС, в проекте с частатой дискритехации 100 Мгц. Спасибо. -

Алгоритм нормировки для ПЛИС

TSURKOV опубликовал тема в Алгоритмы ЦОС (DSP)

Здравствуйте Коллеги. Проектирую фазовый детектор. Требуется нормировать отчеты сигнала относительно максимума. Подскажите какой наиболее эффективный алгоритм лучше использовать для реализации на ПЛИС, в проекте с частатой дискритехации 100 Мгц. Спасибо. -

Спасибо. Я тоже такую штуку в интернете нашел. Смутило что на плате AVRISP стоит mega128 а в списке утилиты такой схемы нет.

-

Здравствуйте. Подскажите как оживить программатор AVRISP mkII - он завис в режиме обновления и теперь не удается к нему подключиться! Можно его оживить? и как ? или уже все?

-

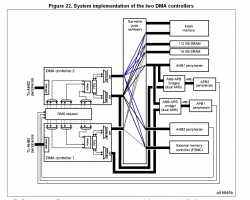

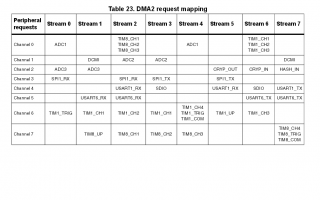

Я тоже обратил внимание на выход к шине. но в таблице каналов и потоков не обнаружил FSMC интерфейса !?

-

Уважаемые коллеги. Хотел уточнить, правильно ли я понимаю ситуацию, что stm32f207 не имеет возможности работать по DMA в режиме внешняя память-> внешняя память !?

-

Уважаемые знатоки lwip стека. Подскажите пожалуйста как грамотно контролировать tcp соединение, как его перезапустить. Насколько я понимаю для этой цели используется функция poll, она периодически вызовется, но в момент ее вызова я не наблюдаю отправки каких либо сообщений в сторону сервера. О закрытии соединения меня информирует флаг (es->pcb->state == CLOSE_WAIT) находящийся в функции обработки принятых сообщений, по нему, пытаюсь закрывать клиента, и потом пере запускать (где то пока подглючивает). А как быть если сервер просто завис в установленном соединении, а потом его перезапустили? Как определить его зависание на stm ? В таком случае мне нужно, определить сбой соединения и установить новое соединение, значит я должен периодически посылать запрос серверу (tcp_connect) до момента подключения?

-

Еще раз большое спасибо. ;) Все отлично заработало, проблема оказалась в программе на ПК.

-

Интересно, а могу я на уровне пользователя lwip стека, убедится, что переданное мной сообщение получено, и только после передавать новое. Где и какие это могут быть флаги!?

-

Помогло. Но правда в другом. После вызова tcp_write стал делать вызов tcp_output (подсмотрел в Вашем коде). Скорость возросла более чем в два раза, местами до полу мегабайта дотягивает. Но этого все равно маловато, видимо это не основная причина, попрежнему много коллизий и перезапросов как с одной так и с другой стороны. Когда тестирую две программы на PC все передается чисто, равномерно, с процессором из за перезапросов все дергается. Периодически отправляет несколько раз один и тот же пакет данных. Буду думать дальше. Спасибо за помощь.

-

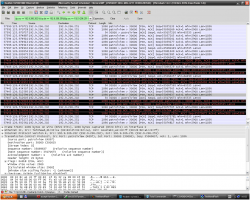

скриншот wareshark. Такое впечатление, что процессор не получает некоторые подтверждения от PC и повторно шлет пакеты. Что и снижает общую скорость.

-

Насколько я понимаю подтверждение tcp_recived это для случая когда процессор принимает. Во всяком случае я так делал. err_t tcp_client_recv(void *arg, struct tcp_pcb *tpcb, struct pbuf *p, err_t err) { // обработка принятого пакета tcp_recved(tpcb,p->tot_len); pbuf_free(p); } Для случая передачи я просто вызываю calback функцию tcp_sent(ptcp_pcb, tcp_client_sent) Хотя ее смысл мне не понятен (функцию взял из примера) в if программа не заходит. err_t tcp_client_sent(void *arg, struct tcp_pcb *tpcb, u16_t len) { struct tcp_client_struct *es; LWIP_UNUSED_ARG(len); es = (struct tcp_client_struct *)arg; if(es->p_tx != NULL) { tcp_client_send(tpcb, es); } return ERR_OK; } вообще мой обработчик передачи крутится в основном цикле и выглядит примерно так void SendDataHandler(void) { // запаковка данных if(tcp_sndbuf(ptcp_pcb) >= msg_len) { err = tcp_write(ptcp_pcb,&tx_tcp_msg,msg_len,1); tcp_sent(ptcp_pcb, tcp_client_sent); } } если err == ERR_OK значит данные переданы.

-

Увеличение размера сообщения результата не дало. Посмотрел повнимательнее в wireshark и увидел что там есть странные сегменты красным на черном фоне надпись tcp previous segment not captured. Если снижаю размер буффера до 264 байт, то подобных сообщений нет. Может как то с этим связанно ?

-

Низкая скорость передачи данных по TCP как быть? Здравствуйте коллеги. Работаю с STM32F207, столкнулся с непонятной для меня ситуацией. Скорость передачи информации по протоколу tcpip в реализации lwip стека максимум до 120 килобайт в секунду (для сообщений длинной 512 байт). Пробовал менять длину пакетов, 512 байт кажется оптимальной. Принимает процессор куда быстрее, удавалось обмениваться со скоростями до 1000 килобайт в секунду. Пользовательских настроек стека не видел. В FareShark вижу что передает мои сообщения одним пакетом, и принимает тоже от PC одним пакетом. Вроде все одинаково но передача в 10 раз медленнее работает и мне это кажется очень странным. Кто-нибудь сталкивался с подобной ситуацией ?

-

1- В SOPCBUILDER ->INTERFACE TO USER LOGIC я задаю двухстороннею шину данных и там есть закладка <type> в ней два параметра <data> <export>. Подскажите пожалуйста, что они означают? 2- В Avalon Tristate Bridge есть закладки <registred> <not registred> Это означает что для всех входных сигналов устанавливается входной синхронизирующий регистр? 3- Я правильно понимаю что в неактивном режиме шина данных в INTERFACE TO USER LOGIC находится в третьем состоянии? Спасибо

-

IOWR_8DIRECT( BASE, OFFSET ) Помогло спасибо Вам БОЛЬШОЕ. А вот IORD_8DIRECT( BASE, OFFSET ) по прежнему пытается читать 32разрядное слово Понятно. Еще раз спасибо !!!

-

Не знаю насколько это корректно, но сделал шину на 32бита (при подключении к 8ми разрядному устройству) и вроде заработало.

-

Создал USER_DEFINED_INTERFACE (Avalon memory slave) и наблюдаю странную картину. При работе с моей логикой сигналы read и write формируемые NIOS состоят из пачки импульсов (4-6 импульсов на один цикл чтения или записи). Если в настройках SOPC-BUILDER->USER_DEFINED_INTERFACE->TIMING во все три параметра (setup, wait, hold) поставить в нуль, тогда цикл записи вроде как одиночный импульс, цикл чтения пачка импульсов. Как только хоть чуть, чуть изменяю эти параметры на не нулевые значения импульс записи превращается также в пакет импульсов. Что тут может быть подскажите пожалуйста ? Такое впечатление что пишется 32-х разрядное слово в 8-ми разрядную шину Такое впечатление что пишется 32-х разрядное слово в 8-ми разрядную шину А как заставить NIOS через IOWR(USER_DEFINED_INTERFACE_0_BASE,0,(alt_u8)0xaa); писать байт?

-

Да вы правы. Я тоже уже к этому пришел. спасибо большое

-

IOWR_ALTERA_AVALON_DMA_STATUS(DMA_0_BASE,0x0); IOWR_ALTERA_AVALON_DMA_CONTROL(DMA_0_BASE,0x0); IOWR_ALTERA_AVALON_DMA_RADDRESS(DMA_0_BASE,(alt_u32)&data[0]); IOWR_ALTERA_AVALON_DMA_WADDRESS(DMA_0_BASE,UART_0_BASE); IOWR_ALTERA_AVALON_DMA_LENGTH(DMA_0_BASE,8); ch = ALTERA_AVALON_DMA_CONTROL_BYTE_MSK | ALTERA_AVALON_DMA_CONTROL_GO_MSK | ALTERA_AVALON_DMA_CONTROL_LEEN_MSK | ALTERA_AVALON_DMA_CONTROL_WCON_MSK; IOWR_ALTERA_AVALON_DMA_CONTROL(DMA_0_BASE,ch); Я правильно понимаю, что в режиме передачи UART через DMA я указываю в RADDRESS - адрес памяти где хранятся передаваемые данные и он будет использоваться DMA контроллером для чтения памяти. А в WADDRESS я указываю физический адрес UART и он должен быть статичным при установке бита WCON. В этом случае физический блок UART должен соединяться с NIOS через master порт шины данных NIOS, помимо того, что UART еще соединен с master портом DMA. И это обязательно !?

-

Я так и делал. IOWR_ALTERA_AVALON_DMA_STATUS(DMA_0_BASE, 0x00000000); IOWR_ALTERA_AVALON_DMA_LENGTH(DMA_0_BASE,5); IOWR_ALTERA_AVALON_DMA_RADDRESS(DMA_0_BASE,0x00001800); IOWR_ALTERA_AVALON_DMA_WADDRESS(DMA_0_BASE,0x00001800); IOWR_ALTERA_AVALON_DMA_CONTROL(DMA_0_BASE,9); i = IORD_ALTERA_AVALON_DMA_STATUS(DMA_0_BASE); DMA_STATUS возвращает -2, т.е. он занят. Такое впечатление, что UART не забирает данные.

-

NIOS-DMA-UART ?

TSURKOV опубликовал тема в Системы на ПЛИС - System on a Programmable Chip (SoPC)

Уважаемые коллеги помогите пожалуйста разобраться с бональной ошибкой. При организации взаимодействия NIOS-DMA-UART функция txchan = alt_dma_txchan_open("/dev/dma_0") возвращает нулевой адрес в указателе. Соответственно не работает и передача по DMA. По документации вроде все понятно, а результат отрицательный. Все устройства (NIOS DMA RAM UART) синтезированы на EP1C6. Память в SOPSbuilder как я только не пробовал крутить. Делал через одну – 4кб, делал RAM1 - 3кб (рабочая), RAM2 – 1кб (DMA), пытался реализовать и в одно и в двух портовом режиме. DMA молчит как убитый. Посоветуйте на что обратить внимание. Спасибо. http://files.mail.ru/I6ZQJJ?t=1[/img]