demsp

Участник-

Постов

39 -

Зарегистрирован

-

Посещение

Весь контент demsp

-

Блок always

demsp опубликовал тема в В помощь начинающему

Могут ли вентили размещаться в блоке always? -

Напечатать какой-нибудь символ в блокноте. На сайте marsohod есть такой проект, но там плата может как принимать сигналы от компьютера, так и отправлять для печати в блокноте различные символы.

-

Тогда надо, наверное, внешний кварцевый генератор на 12800-12900 подключать?

-

Делитель частоты clock-сигнала для клавиши

demsp опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Вот пример make-кода клавиши, генерируемого клавиатурой PS2 Частота ALTUFM_OSC (частота штатного генератора) 5.5 МГц (MAX II EPM240 CPLD Minimal Development Board). Вот пример модуля, использующего штатный генератор module inner_Clock ( output reg LED); ALTUFM_OSC osc( .oscena(1'b1), .osc(clk)); reg signal; reg [24:0] osc_counter; reg [24:0] const_data = 25'b10110111000110110000000; initial begin signal = 1'b0; osc_counter = 25'b0; end //досчитываем до 6 000 000 и обнуляем счетчик osc_counter always @(posedge clk) begin osc_counter <= osc_counter+ 1'b1; if(osc_counter == const_data) begin signal <= ~signal; osc_counter <= 25'b0; end LED = signal; // LED мигает ~1 раз в сеунду. end endmodule Здесь мы 5,5 МГц делим на 6 млн, получаем примерно 1 Гц. Для того, чтобы "сгенерировать частоту" 12.88КГц необходимо чтобы const_data = ~ 427 (decimal) = 1 1010 1011 (binary). Правильно? Как отсчитать 11 тактов? -

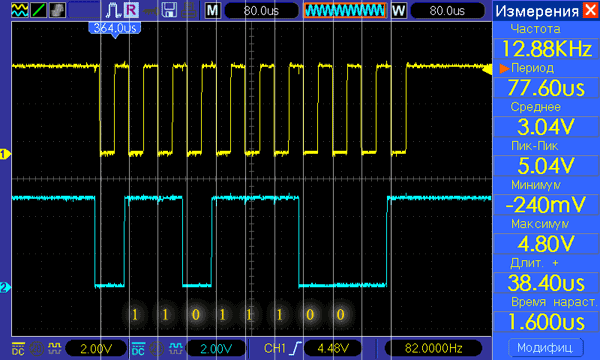

форма сигнала клавиатуры PS2

demsp ответил demsp тема в Форумы по интерфейсам

Спасибо, просто смутило, что для клавиши ALT, код которой равен 11 (что равно десятичному 17), я получаю 0 1000 1000 11, где бит чётности равен 1. -

форма сигнала клавиатуры PS2

demsp опубликовал тема в Форумы по интерфейсам

Как видно на картинке из этой статьи, при передаче символа J мы получаем сигнал с нулевым битом чётности, хотя код символа J равен 3B (чётное число) -

avrdude вывод по UART

demsp опубликовал тема в MCS51, AVR, PIC, STM8, 8bit

В этой статье есть пример работы с Arduimo на Си В Makefile изменил DEVICE изменил CLOCk изменил настройки AVRDUDE Светодиод мигает.Далее, пытаюсь загрузить во flash программу, которая должна выводить в терминал сообщение по UART. Программу взял из этой статьи Заменил в этой программе частоту на 1000000 и боды на 115200. Программа компилируется и загружается во flash, но в терминал ничего не выводится -

Pull-down резистор Quartus

demsp ответил demsp тема в Среды разработки - обсуждаем САПРы

Спс -

Pull-down резистор Quartus

demsp ответил demsp тема в Среды разработки - обсуждаем САПРы

Спасибо. А resource property editor - это отдельная программа, или функция Квартуса (Quartus II). У меня Max II EPM240 CPLD развития доска эксперимент обучения макет -

Pull-down резистор Quartus

demsp опубликовал тема в Среды разработки - обсуждаем САПРы

Можно ли подключить стягивающий резистор к пину? читал про resource property editor - но не нашёл, как его подключить. -

Наверное, с Saleae проще разобраться

-

Китайский 8-каналный логический анализатор

demsp опубликовал тема в Cредства разработки для МК

Спасибо, а логический анализатор надо прошивать? Например, LCSOFT CY7C68013A mini board - вроде бы у него только ОЗУ (ПЗУ нет), значит прошивку надо каждый раз загружать заново? -

lcd 4470 avr

demsp ответил demsp тема в В помощь начинающему

Спасибо, но пока не работает (( Кстати, по диаграмме из даташита необходимо подавать управляющие сигналы на DB4-DB7 "после положительного фронта" на входе Е (подаём 1 на Е, задержка, подаем 1 на DB4-DB7, подаём 0 на Е (запись по спаду), задержка, подаем 0 на DB4-DB7), т.е. должно быть так (в 4bit режиме) int main(void) { DDRD = 0b11111100; PORTD = 0b00000000; _delay_ms(20); //задержка 20ms после подачи питания PORTD = 0b0000 1000; //E=1; _delay_us(40); //задержка 40us PORTD = 0b0011 1000; //PD4=1; PD5=1; E=1; _delay_us(40); //задержка 40us PORTD = 0b0011 0000; //PD4=1; PD5=1; E=0; (запись по спаду) _delay_us(40); //задержка 40us PORTD = 0b0000 0000; ... } Так правильно? -

lcd 4470 avr

demsp опубликовал тема в В помощь начинающему

Можно ли инициализиовать дисплей 44780, подавая биты на входы дисплея #include <avr/io.h> #define F_CPU 16000000UL //16MHz #include <util/delay.h> int main(void) { DDRD = 0b11111100; PORTD = 0b00000000; _delay_ms(20); //задержка 20ms PORTD = 0b0011 0000; //PD4=1; PD5=1; PORTD = 0b0000 1000; //E=1; // тут нужна задержка? PORTD = 0b0000 0000; //E=0; _delay_us(40); //задержка 40us PORTD = 0b0000 1000; //E=1; PORTD = 0b0000 0000; //E=0; _delay_us(40); //задержка 40us PORTD = 0b0000 1000; //E=1; PORTD = 0b0000 0000; //E=0; _delay_us(40); //задержка 40us PORTD = 0b0010 0000; //PD5=1; PORTD = 0b0000 1000; //E=1; PORTD = 0b0000 0000; //E=0; _delay_us(40); // ... } A=PD2 (RS) E=PD3 DB4=PD4 DB5=PD5 DB6=PD6 DB7=PD7 -

Подключение LCD ЖКИ к CPLD max II

demsp опубликовал тема в Работаем с ПЛИС, области применения, выбор

Хочу подключить знакосинтезирующий дисплей (например МЭЛТ MT-10S1) к MAX II epm 240 minimal development board. В даташите к контролеру ЖКИ написано про питание 3-5v. Т.е. можно подключить lcd к тем 3.3v, от которых питается ПЛИСка. В то же время на ПЛИСке установлен регулятор питания (ams1117), т.е. можно (наверное) lcd и плиску подключить к 5v? -

Да, спасибо, в реальной схеме сброс вообще не нужен, но в симуляции использую сброс для инициализации регистров нулями

-

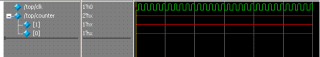

Спасибо. А как это сделать? Если написать module top; reg clk; wire [1:0] counter; count tcount (clk, counter); initial begin clk = 0; forever #10 clk = !clk; counter=0; end endmodule то компилятор выдаёт ошибку Error: C:/.../tcount.v(9): (vlog-2110) Illegal reference to net "counter". Наверное, надо делать счётчик с загрузкой и загружать значение "ноль"

-

Симуляция счётчика в ModelSim

demsp опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Подскажите, как запустить счетчик, чтобы вместо красных линий (нулей) были зелёные линии module count (input clk, output reg [1:0]counter); always @(posedge clk) counter <= counter + 1; endmodule Test bench module top; reg clk; wire [1:0] counter; count tcount (clk, counter); initial begin clk = 0; forever #10 clk = !clk; end endmodule -

Антидребезг

demsp ответил demsp тема в Языки проектирования на ПЛИС (FPGA)

Спасибо. Мне надо реализовать антидребезг для одной кнопки на CPLD Тогда надо включить ТШ в настройках пина, а на пин повесить конденсатор. Так? -

Антидребезг

demsp ответил demsp тема в Языки проектирования на ПЛИС (FPGA)

Спасибо, а вот ещё в мануале MAX II Device Handbook написано про триггеры Шмитта, которые обеспечивают гистерезис на буфере входных сигналов, предотвращая дребезг контактов. Я в Pin Planer включил триггер Шмитта на входном пине, но дребезг остался. Наверное, надо внешний конденсатор повесить? -

Антидребезг

demsp опубликовал тема в Языки проектирования на ПЛИС (FPGA)

Как устранить дребезг кнопки? Прочитал, что можно включить Weak Pull-Up Resistor (Assigments -> Assigment Editor) который идет на R3. А на каком пине висит R3? -

Частота штатного генератора

demsp ответил demsp тема в Языки проектирования на ПЛИС (FPGA)

Спасибо, с генератором на 5.5Мгц более-менее понятно. А как подключить генератор на 50МГц? В этой схеме показано, что генератор должен идти на вывод 64. Но на синей плате нет вывода 64. -

Частота штатного генератора

demsp ответил demsp тема в Языки проектирования на ПЛИС (FPGA)

Досчитываю до 6 000 000. LED мигает примерно 1 раз в секунду. module M ( output reg LED); ALTUFM_OSC osc( .oscena(1'b1), .osc(clk)); reg signal; reg [24:0] osc_counter; reg [24:0] const_data =25'b10110111000110110000000; initial begin signal = 1'b0; osc_counter = 25'b0; end always @(posedge clk) begin osc_counter = osc_counter+ 1'b1; if(osc_counter == const_data) begin signal = ~signal; osc_counter = 25'b0; end LED = signal; end endmodule -

Иосиф Григорьевич, спасибо (внимательно посмотрел)