-

Постов

43 -

Зарегистрирован

-

Посещение

Весь контент Jul'etta

-

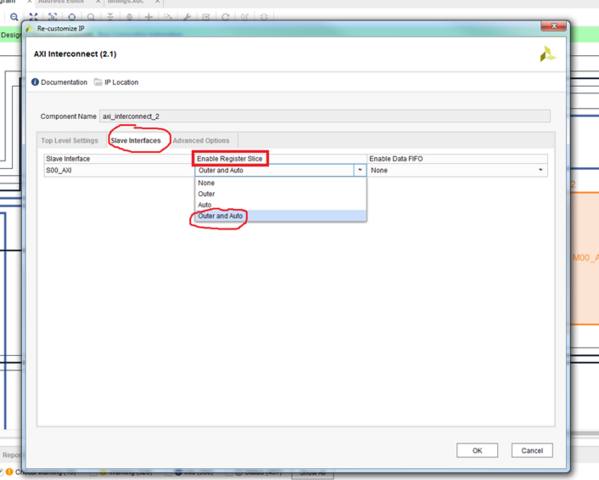

Добрый день. кажется, получилось. Поставила "enable register slice" в блоке axi interconnect, куда подключен блок pcie. Это решило одну проблему с критическими путями (отрицательное значение slack по параметру tsetup). Вторую проблему (отрицательное значение slack по параметру thold) помогли решить 2 строчки в файле констрейнов: set_clock_groups -asynchronous -group [get_clocks PCIe_RefClkn] set_clock_groups -asynchronous -group [get_clocks PCIe_RefClkp] Спасибо за отличные статьи и дельные советы.

-

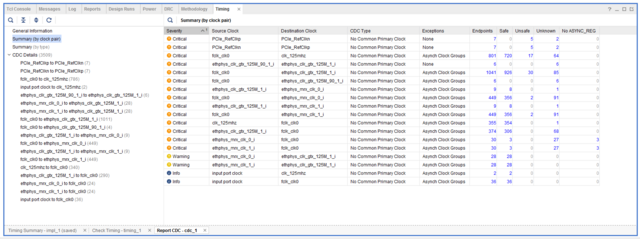

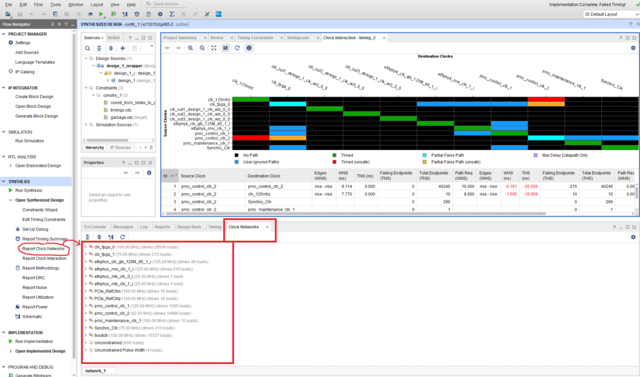

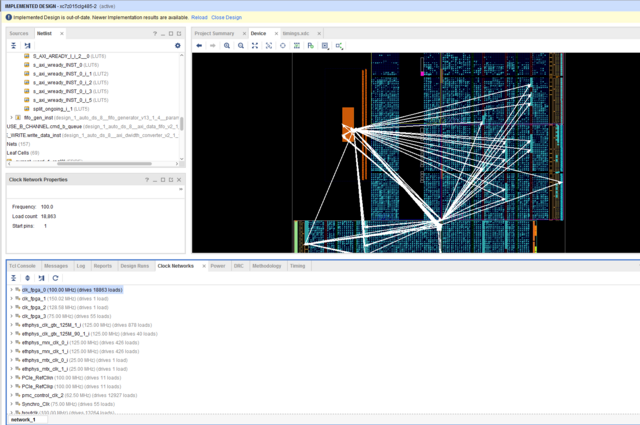

Спасибо! Информация из Report CDC (картинку прикрепила). Там имеется мой проблемный домен (один из) - clk_125mhz - во вкладке exception указано, что он относится к асинхронной группе. Что это значит? ведь все равно ругается на него.

-

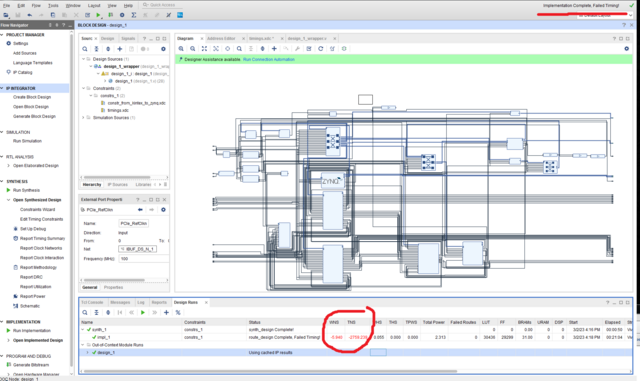

да, дикая дичь... но надо разрулить. Меня обнадеживает то, что проект укладывается по ресурсам девборда. Объективно ли судить по "отчету" задействованных ресурсов на вкладках power и project summary? Ладно бы, если проект на этапе трассировки/размещения валился, а то ведь вот вроде все разместилось на кристалле, только тайминги подправить - и усе. Но вот это пока что не решаемая задача, как ни прописываю тайминги. И документации много - ug903 и ug906 изучаю, и статьи, что вы мне посоветовали, прочитала - но общего понимания синтаксиса, что и как прописать, применительно к моему проекту, увы, пока не имею. Кстати, изначально проект был под Kintex-7, конкретно xc7k325tffg676-2. А у меня сейчас под Zynq-7000 xc7z015clg485-2

-

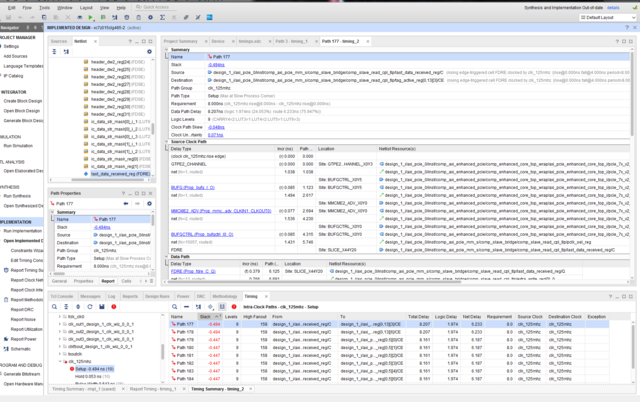

Спасибо за ответы. Прикрепила скриншот одного из путей - path177. Во вкладке с общими сведениями о пути указаны и источник и пункт назначения. Каков должен быть синтаксис, если для этого пути прописать set_false_path ? Пока написала так: create_clock -period 8.000 -name clk_125mhz -waveform {0.000 4.000} [get_nets design_1_i/axi_pcie_0/inst/comp_axi_pcie_mm_s/comp_slave_bridge/comp_slave_read_cpl_tlp/last_data_received_reg/C] set_clock_groups -asynchronous -group [get_clocks clk_125mhz] У меня до этого ругался еще на fclk_clk0 и fclk_clk1, прописала для них следующее: create_clock -period 50.000 -name fclk_clk0 -waveform {0.000 25.000} [get_nets design_1_i/processing_system7_0/FCLK_CLK0] set_clock_groups -asynchronous -group [get_clocks fclk_clk0] create_clock -period 50.000 -name fclk_clk1 -waveform {0.000 25.000} [get_nets design_1_i/processing_system7_0/FCLK_CLK1] set_clock_groups -asynchronous -group [get_clocks fclk_clk1] Помогло. Надо ли для каждого из десятка путей для клокового домена clk_125mhz указывать асинхронные клоки? или для каждого прописывать set_false_path ?

-

Timing Report смотрела, проблемы с какими часами знаю. Вот как раз в этом я и прошу помощи, научите, чем лечится :) За статью спасибо, ознакомлюсь.

-

Implementation complete, failing timing!

Jul'etta опубликовал тема в Среды разработки - обсуждаем САПРы

Здравствуйте. Уже пару недель бодаюсь с проблемой таймингов в проекте. Задача такая: портировать проект с одной платформы на другую. Был проект под Kintex с программным процессором микроблейз, нужен под Zynq с аппаратными процессорами арм. Соответственно, править начала с блочного дизайна в Vivado. Этап синтеза проходит без ошибок, далее имплементация - и вот тут начинается интересное. Проект пока не проходит по таймингам. Что было сделано: ознакомилась с документом "UG903 Using Constraints". Файл с временнЫми ограничениями (timing constraints) перешел ко мне от старого проекта, в соответствии с документом разобралась как это пишется. Прочитаны статьи по конвейеризации проекта (как один из вариантов решения проблем с временем распространения сигналов) - но не пойму куда (в какое место в коде) тут надо вставлять регистры, да и поможет ли это? Прочитана статья по стратегиям синтезатора. Подскажите, пожалуйста, в каком направлении копать? Разбираться ли плотней с конвейеризацией схемы или лучше изучить стратегии синтезатора или прописывать новые и новые временнЫе ограничения в файле? timings.xdc -

это просто магия. Я еще раз перезагрузила комп, заново создала тестовый проект ядра. заново выполнила скрипт (в окошке консоли запустила), появился и лог в папке, как у вас. Все получилось! Проект просинтезировался. Буду запускать теперь основной проект. Премного благодарна вам, RobFPGA, и всем, кто помогал и делом и советом. Надеюсь, это поможет еще кому-нибудь, кто столкнется с такой же проблемой.

-

я так и сделала. Распаковала архив в папку с установленной вивадой, инструкция то несложная. Прочитала readme, запустила patch.py, быстренько окошко консоли показалось и закрылось. На этом усе. Дальше перезагрузила комп, снова открыла многострадальный проект test_v_tpg, далее: clear cache - reset output products - generate output products (режим OOC), потом run synthesis. вуаля - снова эта ошибка. Лога как у вас нету.

-

Простите за глупый вопрос, а где смотреть этот лог? тут уже их столько пересморено везде где только можно) лог под названием vivado_hls.log? таки там опять эта ошибка в конце

-

ахах, точно, я ожидала, что подстветится красным, ан нет :) ctrl+f мне в помощь :) Т.е. патч не сработал/не правильно установился? я все сделала по инструкции (хотя теперь, конечно, не могу утверждать наверняка).

-

очень много букв вывалилось в tcl concole. Положила их в файл *.txt tcl_console_log.txt Там только ворнинги, ошибок нет (?)

-

сейчас проверю файлы design_1_v_tpg_0_1.tcl

-

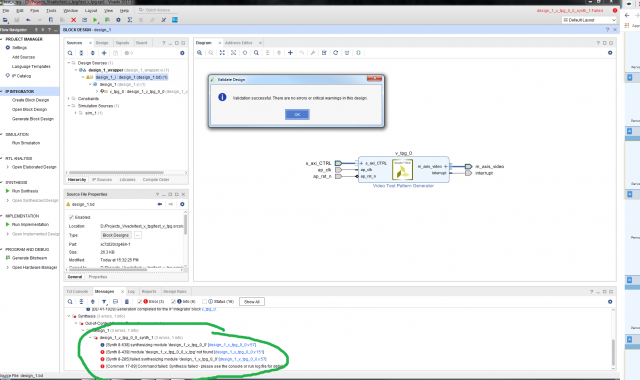

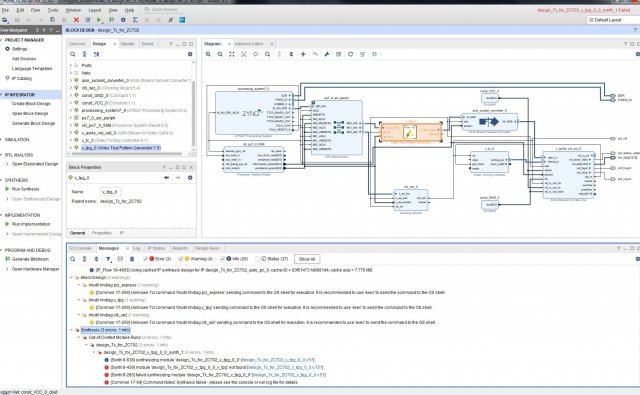

Есть! заодно научилась чистить кэш в виваде :) спасибо за инструкцию Ниже скопировала лог: *** Running vivado with args -log design_1_v_tpg_0_1.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source design_1_v_tpg_0_1.tcl ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:55:03 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source design_1_v_tpg_0_1.tcl -notrace compile_c: Time (s): cpu = 00:00:00 ; elapsed = 00:07:17 . Memory (MB): peak = 310.199 ; gain = 5.633 config_ip_cache: Time (s): cpu = 00:00:00 ; elapsed = 00:00:06 . Memory (MB): peak = 311.992 ; gain = 1.793 Starting RTL Elaboration : Time (s): cpu = 00:00:02 ; elapsed = 00:00:03 . Memory (MB): peak = 386.945 ; gain = 74.953 INFO: [Synth 8-638] synthesizing module 'design_1_v_tpg_0_1' [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:57] ERROR: [Synth 8-439] module 'design_1_v_tpg_0_1_v_tpg' not found [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:151] ERROR: [Synth 8-285] failed synthesizing module 'design_1_v_tpg_0_1' [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:57] Finished RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:04 . Memory (MB): peak = 426.008 ; gain = 114.016 ERROR: [Common 17-69] Command failed: Synthesis failed - please see the console or run log file for details *** Running vivado with args -log design_1_v_tpg_0_1.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source design_1_v_tpg_0_1.tcl ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:55:03 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source design_1_v_tpg_0_1.tcl -notrace *** Running vivado with args -log design_1_v_tpg_0_1.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source design_1_v_tpg_0_1.tcl ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:55:03 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source design_1_v_tpg_0_1.tcl -notrace compile_c: Time (s): cpu = 00:00:00 ; elapsed = 00:06:37 . Memory (MB): peak = 310.758 ; gain = 5.633 config_ip_cache: Time (s): cpu = 00:00:00 ; elapsed = 00:00:06 . Memory (MB): peak = 312.184 ; gain = 1.426 Starting RTL Elaboration : Time (s): cpu = 00:00:02 ; elapsed = 00:00:03 . Memory (MB): peak = 386.668 ; gain = 74.484 INFO: [Synth 8-638] synthesizing module 'design_1_v_tpg_0_1' [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:57] ERROR: [Synth 8-439] module 'design_1_v_tpg_0_1_v_tpg' not found [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:151] ERROR: [Synth 8-285] failed synthesizing module 'design_1_v_tpg_0_1' [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:57] Finished RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:04 . Memory (MB): peak = 425.730 ; gain = 113.547 ERROR: [Common 17-69] Command failed: Synthesis failed - please see the console or run log file for details *** Running vivado with args -log design_1_v_tpg_0_1.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source design_1_v_tpg_0_1.tcl ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:55:03 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source design_1_v_tpg_0_1.tcl -notrace compile_c: Time (s): cpu = 00:00:00 ; elapsed = 00:06:33 . Memory (MB): peak = 310.578 ; gain = 5.637 config_ip_cache: Time (s): cpu = 00:00:01 ; elapsed = 00:00:06 . Memory (MB): peak = 311.805 ; gain = 1.227 Starting RTL Elaboration : Time (s): cpu = 00:00:02 ; elapsed = 00:00:03 . Memory (MB): peak = 387.387 ; gain = 75.582 INFO: [Synth 8-638] synthesizing module 'design_1_v_tpg_0_1' [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:57] ERROR: [Synth 8-439] module 'design_1_v_tpg_0_1_v_tpg' not found [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:151] ERROR: [Synth 8-285] failed synthesizing module 'design_1_v_tpg_0_1' [d:/Projects_Vivado/test_v_tpg/test_v_tpg.srcs/sources_1/bd/design_1/ip/design_1_v_tpg_0_1/synth/design_1_v_tpg_0_1.v:57] Finished RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:04 . Memory (MB): peak = 426.199 ; gain = 114.395 ERROR: [Common 17-69] Command failed: Synthesis failed - please see the console or run log file for details

-

любопытная тенденция намечается спасибо за ссылки! путь к файлу у меня около 120 символов (имею ввиду названия всех папок, с нижними подчеркиваниями и слэшами), т.е. вроде не очень длинный.

-

огого... это лог синтеза всего проекта, а как отдельно отсинтезировать ядро? в отдельном проекте?

-

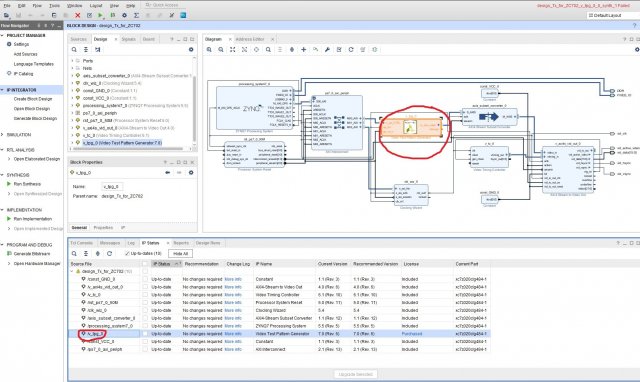

лог синтеза я прикрепляла выше, продублирую еще раз *** Running vivado with args -log design_Tx_for_ZC702_v_tpg_0_0.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source design_Tx_for_ZC702_v_tpg_0_0.tcl ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:55:03 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source design_Tx_for_ZC702_v_tpg_0_0.tcl -notrace compile_c: Time (s): cpu = 00:00:01 ; elapsed = 00:06:18 . Memory (MB): peak = 311.258 ; gain = 5.566 config_ip_cache: Time (s): cpu = 00:00:00 ; elapsed = 00:00:06 . Memory (MB): peak = 313.285 ; gain = 2.027 Starting RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:03 . Memory (MB): peak = 389.176 ; gain = 75.891 INFO: [Synth 8-638] synthesizing module 'design_Tx_for_ZC702_v_tpg_0_0' [d:/Projects_Vivado/HDMI_Tx_design_for_ZC702/HDMI_Tx_design_for_ZC702.srcs/sources_1/bd/design_Tx_for_ZC702/ip/design_Tx_for_ZC702_v_tpg_0_0/synth/design_Tx_for_ZC702_v_tpg_0_0.v:57] ERROR: [Synth 8-439] module 'design_Tx_for_ZC702_v_tpg_0_0_v_tpg' not found [d:/Projects_Vivado/HDMI_Tx_design_for_ZC702/HDMI_Tx_design_for_ZC702.srcs/sources_1/bd/design_Tx_for_ZC702/ip/design_Tx_for_ZC702_v_tpg_0_0/synth/design_Tx_for_ZC702_v_tpg_0_0.v:151] ERROR: [Synth 8-285] failed synthesizing module 'design_Tx_for_ZC702_v_tpg_0_0' [d:/Projects_Vivado/HDMI_Tx_design_for_ZC702/HDMI_Tx_design_for_ZC702.srcs/sources_1/bd/design_Tx_for_ZC702/ip/design_Tx_for_ZC702_v_tpg_0_0/synth/design_Tx_for_ZC702_v_tpg_0_0.v:57] Finished RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:04 . Memory (MB): peak = 429.242 ; gain = 115.957 ERROR: [Common 17-69] Command failed: Synthesis failed - please see the console or run log file for details задала вопрос в техподдержку Xilinx, посмотрю, что ответят.

-

-

я просто отдельно создала новый проект и поставила только это ядро. Ожидала какую угодно ошибку - но опять появилась та же.

-

я прикрепила в первом посте этот файл, на который ругается. Лежит он на месте, никто его не трогал) гм, этот способ не пробовала. Ок, сейчас займусь, благодарю.

-

Приветствую. К сожалению, патч не помог. Все сделала, как в инструкции на сайте Xilinx, перезагрузила, отправила свой проект на синтез - та же ошибка. Пора переходить на полностью свои ядра? :)

-

1. *** Running vivado with args -log design_Tx_for_ZC702_v_tpg_0_0.vds -m64 -product Vivado -mode batch -messageDb vivado.pb -notrace -source design_Tx_for_ZC702_v_tpg_0_0.tcl ****** Vivado v2017.1 (64-bit) **** SW Build 1846317 on Fri Apr 14 18:55:03 MDT 2017 **** IP Build 1846188 on Fri Apr 14 20:52:08 MDT 2017 ** Copyright 1986-2017 Xilinx, Inc. All Rights Reserved. source design_Tx_for_ZC702_v_tpg_0_0.tcl -notrace compile_c: Time (s): cpu = 00:00:01 ; elapsed = 00:06:18 . Memory (MB): peak = 311.258 ; gain = 5.566 config_ip_cache: Time (s): cpu = 00:00:00 ; elapsed = 00:00:06 . Memory (MB): peak = 313.285 ; gain = 2.027 Starting RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:03 . Memory (MB): peak = 389.176 ; gain = 75.891 INFO: [Synth 8-638] synthesizing module 'design_Tx_for_ZC702_v_tpg_0_0' [d:/Projects_Vivado/HDMI_Tx_design_for_ZC702/HDMI_Tx_design_for_ZC702.srcs/sources_1/bd/design_Tx_for_ZC702/ip/design_Tx_for_ZC702_v_tpg_0_0/synth/design_Tx_for_ZC702_v_tpg_0_0.v:57] ERROR: [Synth 8-439] module 'design_Tx_for_ZC702_v_tpg_0_0_v_tpg' not found [d:/Projects_Vivado/HDMI_Tx_design_for_ZC702/HDMI_Tx_design_for_ZC702.srcs/sources_1/bd/design_Tx_for_ZC702/ip/design_Tx_for_ZC702_v_tpg_0_0/synth/design_Tx_for_ZC702_v_tpg_0_0.v:151] ERROR: [Synth 8-285] failed synthesizing module 'design_Tx_for_ZC702_v_tpg_0_0' [d:/Projects_Vivado/HDMI_Tx_design_for_ZC702/HDMI_Tx_design_for_ZC702.srcs/sources_1/bd/design_Tx_for_ZC702/ip/design_Tx_for_ZC702_v_tpg_0_0/synth/design_Tx_for_ZC702_v_tpg_0_0.v:57] Finished RTL Elaboration : Time (s): cpu = 00:00:03 ; elapsed = 00:00:04 . Memory (MB): peak = 429.242 ; gain = 115.957 ERROR: [Common 17-69] Command failed: Synthesis failed - please see the console or run log file for details спасибо, сейчас ознакомлюсь

-

эм, это все относится к моей проблеме?) У меня версия 2017.1

-

Vivado module not found

Jul'etta опубликовал тема в Работаем с ПЛИС, области применения, выбор

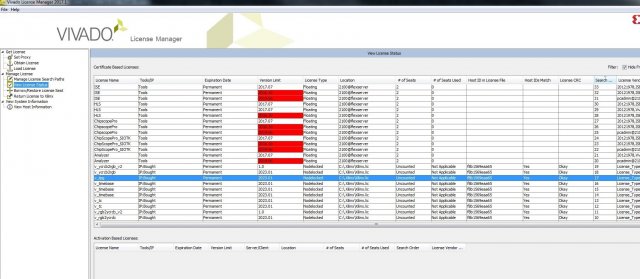

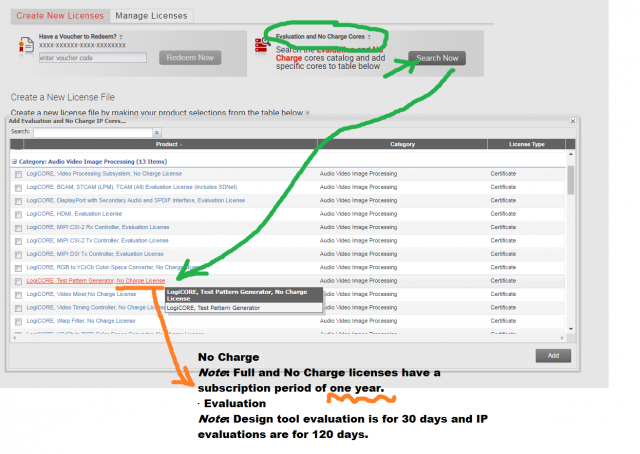

Приветствую. Столкнулась с такой проблемой: рабочий проект перестал синтезироваться, ошибку вивада (2017.1) выдает о том, что не может найти модуль генератора тестовых шабловов - v_tpg (картинку прикрепила). Первая мысль - закончилась лицензия на ядро. Стала копать в эту сторону, проверила - лицензия оформлена в июне 2021 года и, исходя из описания документа ug973, действует до июня 22 года (тип лицензии - No charge). Дальше исходя из ошибки, перешла на строчки кода верилог, на который ругается виввада (картинку прикрепила, сам файл тоже). Это описание ядра, сгенерированное автоматически, ничего там я не меняла. Ругается на экземпляр модуля? Не совпадают имена в коде? Помогите, пожалуйста, кто уже сталкивался с стакой проблемой? Спасибо за любой дельный совет :) design_Tx_for_ZC702_v_tpg_0_0.v -

HDMI на Artix AC701

Jul'etta ответил Jul'etta тема в Языки проектирования на ПЛИС (FPGA)

Здравствуйте! Смотрели документ pg236 для rx и tx? Там в разделе Running the example design приведена сборка проекта как раз под кинтекс. Только обращайте внимание на версию (год) документа :) А вообще очень классные уроки по HDMI вот тут https://support.xilinx.com/s/question/0D52E00006hpsS0SAI/xilinx-video-series-and-blog-posts?language=en_US -

Я Ваш преданный читатель! Цикл руководств по Микроблейзу бережно хранится на самом видном месте на рабочем столе. Конференцию видела, да что-то страшно, там такие темы заявлены, окромя слов мезонин и констрейны ничего больше знакомого не встретила :) Спасибо за приглашение, если наберусь смелости, приду :)

- 16 ответов

-

- microblaze

- arty

-

(и ещё 2 )

C тегом: