-

Постов

3 420 -

Зарегистрирован

-

Посещение

-

А зачем? Для сравнения достаточно совпадения кодов.

-

Вопрос по применению файла quartus_pgm.exe

_sda опубликовал тема в Среды разработки - обсуждаем САПРы

Коллеги, применяю этот файл для записи загрузочных EEPROM давно, выполняет свои функции исправно. Но вот понадобилось мне прочитать прошивку из девайса для сравнения, а прочитанная и записанная в файл прошивка совершенно не совпадает с оригинальным файлом. Для программирования в батнике применяю такую строчку: .... @c:\intelFPGA\18.1\quartus\bin64\quartus_pgm -m JTAG -o pvbi;"%full_path%\%name_jic%" Читаю прошивку штатным программатором Квартуса. И что интересно, если записать программатором Квартуса а потом прочитать им же то файлы совпадают. А вот если записать с помощью pgm , а потом прочитать программатором Квартуса то файлы получаются совершенно разные. Такое ощущение что проблема в настройках. Буду рад любой подсказке. -

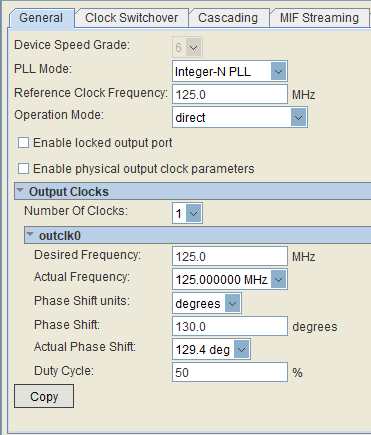

Странное поведение PLL в пятом циклоне

_sda опубликовал тема в Работаем с ПЛИС, области применения, выбор

Впервые сталкиваюсь с таким поведением. В новом проекте от одного опорного генератора запитаны два PLL, к одной PLL из этой пары замечаний нет, а вторая PLL при включении питания примерно в одном случае из пяти формирует на выходе клок с непредсказуемой фазой. У обоих используется один выход, настройки простые. Кто нибудь сталкивался с таким поведением? Небольшое уточнение. Фаза выходного клока хоть и не предсказуема после включения питания (само значение), но держится стабильно. -

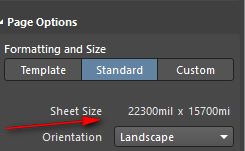

Как восстановить sheet size

_sda опубликовал тема в Altium Designer, DXP, Protel

Коллеги, пропала возможность изменить размер листа в настройках схемного редактора. Altium V24.1.2 Можно это как-то исправить? Сорри, разобрался. -

Пободался немного, сдался, переустановил Квартус. Работает нормально.

-

Нечаянно попробовал законнектиться с девайсом для отладки, а в это время работал сигнал-тап. выскочила ошибка и проект ниос больше не компилится. Удалил проект, создал новый, при компиляции ругается: /H-x86_64-mingw32/nios2-elf/bin/ld.exe: address 0x20800 of ar2023rx_app.elf section `.bss' is not within region `ram_sys' Но если посмотреть в system.h то видно что вроде его там и не должно быть, у него другое адресное пространство. #define ALT_MODULE_CLASS_ram_sys altera_avalon_onchip_memory2 #define RAM_SYS_ALLOW_IN_SYSTEM_MEMORY_CONTENT_EDITOR 0 #define RAM_SYS_ALLOW_MRAM_SIM_CONTENTS_ONLY_FILE 0 #define RAM_SYS_BASE 0x10000 #define RAM_SYS_CONTENTS_INFO "" #define RAM_SYS_DUAL_PORT 0 #define RAM_SYS_GUI_RAM_BLOCK_TYPE "AUTO" #define RAM_SYS_INIT_CONTENTS_FILE "nios2_ram_sys" #define RAM_SYS_INIT_MEM_CONTENT 1 #define RAM_SYS_INSTANCE_ID "NONE" #define RAM_SYS_IRQ -1 #define RAM_SYS_IRQ_INTERRUPT_CONTROLLER_ID -1 #define RAM_SYS_NAME "/dev/ram_sys" #define RAM_SYS_NON_DEFAULT_INIT_FILE_ENABLED 1 #define RAM_SYS_RAM_BLOCK_TYPE "AUTO" #define RAM_SYS_READ_DURING_WRITE_MODE "DONT_CARE" #define RAM_SYS_SINGLE_CLOCK_OP 0 #define RAM_SYS_SIZE_MULTIPLE 1 #define RAM_SYS_SIZE_VALUE 65536 #define RAM_SYS_SPAN 65536 #define RAM_SYS_TYPE "altera_avalon_onchip_memory2" #define RAM_SYS_WRITABLE 1 Какая-то путаница с адресами. Коллеги, очень поджимает время, может кто знает как отремонтировать?

-

Ага, спасибо! Как то не подумал обратиться к любимой Вике...

-

Как вычислить фазу импульса ЛЧМ?

_sda опубликовал тема в Вопросы системного уровня проектирования

Коллеги, известны следующие параметры: частота дискретизации, начальная частота, конечная частота, длительность импульса. Как зная начальную фазу в начале импульса вычислить фазу ЛЧМ в конце импульса? -

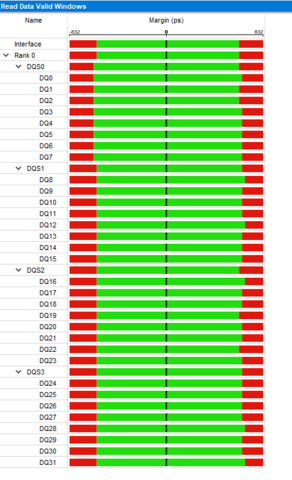

Отладка проекта с DDR3

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Спасибо всем участникам обсуждения! Все платы заработали, калибровка проходит. От себя добавлю - внимательность и ещё раз внимательность. Больше ничего не потребовалось. -

Отладка проекта с DDR3

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Никакая не глупость, мне самому, например, попадались FPGA с маркировкой несуществующей в природе. Да, скорее всего рискну перепаять, пока других мыслей нет. Паяли сами, рентген-контроля нет. -

Отладка проекта с DDR3

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Стрёмно как-то, могу и рабочей платы лишиться... Частота уж больно высокая, нет соответствующего оборудования. У осциллографа полоса 200 МГц. И ещё сложилось впечатление что корка затыкается на нерабочих платах (если не проходит калибровка). При попытке записать данные шина не оживляется. -

Отладка проекта с DDR3

_sda опубликовал тема в Работаем с ПЛИС, области применения, выбор

Коллеги, у меня спаяно 6 новых плат, три из них работают, три - нет. Работаю с FPGA Intel. Картинка результата тестирования рабочей платы: На мой взгляд очень неплохо. А на нерабочих тест вообще не проходит. Вроде всё уже проверил: номиналы резисторов, целостность связи FPGA - DDR3, напряжения питания... В прошлом году сделал десяток таких плат, но слава Богу такого затыка не было. Возможно кто-то поделится опытом как выходили из такой ситуации. На что ещё обратить внимание? -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Я вроде уже разобрался, отремонтировал. Спасибо за желание помочь. -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Хех... Перегенерил BSDL-файл с признаком post. В самом файле эта ножка описывается как выход: --BSC group 185 for Family-specific output pin F21 "555 (BC_4, *, internal, X)," & "556 (BC_1, *, control, 1)," & "557 (BC_1, IOF21, output3, X, 556, 1, Z)," & А в TopJTAG всё равно описывается как вход: Ничего не понимаю. Что ему ещё нужно? -

Вопрос по TopJTAG

_sda ответил _sda тема в Работаем с ПЛИС, области применения, выбор

Вроде разобрался, опять подвела память. Буду устранять дефект.