-

Постов

1 957 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о sonycman

-

Звание

Любитель

- День рождения 06.09.1977

Контакты

-

Сайт

Array

-

ICQ

Array

Информация

-

Город

Array

Retained

-

Звание

Array

Посетители профиля

16 267 просмотров профиля

-

А когда Agilex в продаже наконец появятся, никто не в курсе?

-

Периодические stall/отвалы на шине USB

sonycman ответил sonycman тема в Интерфейсы

И второе, что заметил - если смотреть сниффером не перед хабои, а после, то видно много каких-то периодических инвалид пакетов, то ли это SOFы бьются, то ли что. В общем налицо какая-то аппаратная проблема, позже посмотрю осциллографом. После компьютера, опять же, ничего такого нет. Питание шины 5в формируется dc-dc а-ля кренка с интегрированной катушкой, плюс стоят доп. керамика и танталы. Ну и кабели потыкаю разные... -

Периодические stall/отвалы на шине USB

sonycman опубликовал тема в Интерфейсы

Приветствую. Поднял несложный USB хост под baremetal Zynq Ultrascale, контроллер Synopsys DWC3, xhci, на скорости HS и ниже, Super Speed не использую. PHY USB3320. Подключаю только хаб, клаву, мышь и геймпад, и в общем-то все работает, но беспокоят периодические STALLы от мышки (в основном) при энумерации, в ответ на различные стандартные запросы дескрипторов. То есть 10 раз энумерация проходит, а на 11 ошибка. Сниффером заметил вот что. Так как хаб high speed, а мышь full - хост шлет хабу split пакеты, но поражает их предельное количество - complete split запрос каждые 2 микросекунды! То есть один start split, а затем несколько десятков complete split каждые 2 мкс до тех пор, пока несчастный хаб вместо NYET наконец-то ответит ACK. Посмотрел как работает хост компьютера - там только один комплит запрос, но не сразу, а спустя время, и хаб отвечает сразу ACK. В драйвере xhci в контекстах эндпоинтов никаких полей, регулирующих частоту запросов контроллера не нашел. Не знаю, может это и нормально, просто шина свободна и у контроллера много времени, вот он и спамит хаб? В глобальных регистрах DWC3 тоже не увидел нужных настроек... -

А в последнем Витисе тоже нет прогресса, или, может быть, пофиксили?

-

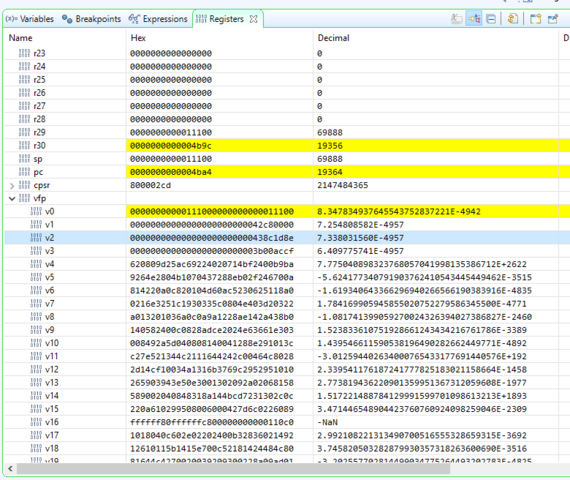

В 2019 SDK то же самое 😞 Причем для Cortex-A9 все нормально, v, s и d регистры, а для A53 руки не дошли, что-ли?

-

Приветствую. Смотрю в дебаггере код для Cortex-A53, регистры FPU в окне отображаются только как 128 битный вектор, и никак не могу переключить отображение как 32 бит float или 64 бит double. Это я туплю, или витис такой деревянный?

-

Приветствую! Коллеги, если у кого-то вдруг имеется схема или другая документация на модули фирмы Enclustra, в частности Mercury XU5 и материнской платы Mercury+ ST1 - нижайше прошу поделиться. Мануал их сайт даёт скачать без проблем, но схему нет - запрашивают фирму\адрес\и т.п., а я физ. лицо, не светит мне ничего... :(

-

Чертовщина творится. Убрал схему VGA выхода - PLL стала стабильно выдавать 32 МГц, выше пока не пробовал. До этого выше 29 МГц не поднималось. Что изменилось в разводке - если раньше в моей схеме был один MMCM и одна PLL в одном CMT блоке, то теперь вивадо развёл их по разным CMT, на разных сторонах чипа. Плюс раньше вивадо в цепи заворота тактовой между IOBUF и входом PLL вставлял BUFG, то теперь его нет. Больше вроде ничего не поменялось. Как объяснить повышение частоты PLL?

-

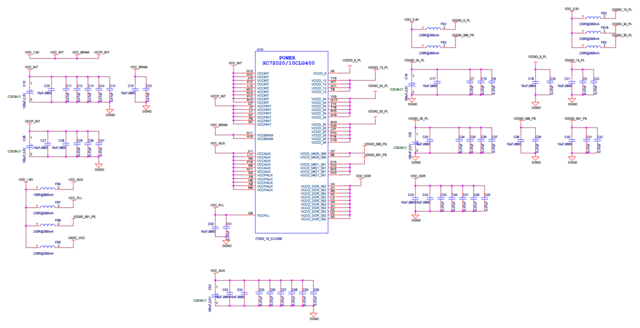

Плата используется такая: Z-Turn v1. Вот схема питания: Настройка пина: LVTTL, FAST, 8ma. Можно попробовать настройку с бОльшим током... Дифф. стандарт тоже пока не пробовал, надо глянуть в эту сторону. В этом-же банке работает VGA выход на 28.5 МГц, который можно выключить, в принципе. По поводу фазового шума, думаю, вся эта идея не укладывается в спецификацию. В настройке PLL джиттер выставил по максимуму - 1 нс. Какой он там по факту - не скажу, но вероятнее всего поболее будет. Есть ещё идея уменьшить разрядность oserdes с 8-ми до 6-ти бит, то есть снизить коэфф. умножения до 6-ти, чтобы уменьшить входную частоту PLL. Но джиттер в этом случае только вырастет, мне кажется.

-

Работает без проблем с часотой до 29 МГц, выше PLL не лочится и нормального клока на ее выходе нет. Получается,, входной пин не берет частоту выше 232 МГц (29 * 8)?

-

Beby Благодарю за помощь, собралось, когда PLL инстанциировал как у Вас, в исходнике, а не через блок-дизайн. Дальше пришлось пин, через который генерируется клок, повесить на свободно висящий пин чипа, иначе 250МГц уже не схватывается входным буфером. Всё заработало, 576р @27МГц монитор подхватил как родные! С 32 битным счётчиком такой генератор позволит мне подгонять частоту с отклонением менее наносекунды от кадра к кадру!

-

А если попробовать полноценный oserdes и завести CLK_2 на вход pll?

-

Для идеального выравнивания сигналов по времени фрейма делаю HDMI клок чуть быстрее, а лишние такты клока блокирую через BUFGCE. Не получается без вывода клока наружу. Только используя два пина - выходной и входной...

-

Видеосигнал VGA, различной частоты.

-

Только для проверки. Мне нужно генерировать частоту под входящий различный видеосигнал и синхронизироваться под него с точностью до нескольких сотен наносекунд на фрейм. На такое куцые ФАПЧ простого цинка не способны, к сожалению...