Leka

Участник-

Постов

1 769 -

Зарегистрирован

-

Посещение

Репутация

0 ОбычныйИнформация о Leka

-

Звание

Профессионал

Контакты

-

ICQ

Array

Посетители профиля

5 018 просмотров профиля

-

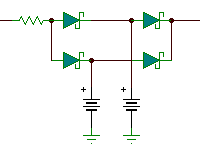

У меня другое решение появилось благодаря дискуссии - два аккумулятора через диоды в параллель. Возможны два варианта работы: или ток заряда разделится примерно поровну (по ~0,05С в каждый), или один будет отдуваться под полным зарядным током (~0,1С), и работать стабилитроном, а другой отдыхать заряженным. Общая надежность повысится.

-

Для незаряжаемой литиевой батарейки это тоже м/б проблемой - по остаточной емкости, как определять ? Для аккумулятора можно предусмотреть несложную схему оценки внутреннего сопротивления (один транзистор для кратковременного подключения мощной нагрузки), для незаряжаемой батарейки такой метод не подойдет. Или Ni-MH может потечь до деградации таких электрических параметров, как напряжение и внутреннее сопротивление ? Мне Ni-MH (которые с низким саморазрядом) нравятся своей неприхотливостью, использую уже давно. -

-

У, VARTA, например, есть отдельный раздел: "for bridging applications", а еще для новых Ni-MH допускается неограниченное время подзарядки током 0,1С при потере емкости до 80%. https://www.varta-ag.com/fileadmin/varta_microbattery/downloads/service/battery-documentation/nickel-metal-hydride/Sales-Literature-201810_HANDBOOK_Rechargeable_Button_Cells_NiMH_en.pdf Сейчас только нашел этот документ, так что вопрос можно считать закрытым - буферный режим допустим для Ni-MH, изготовленных по новой технологии. Надо будет только получше поискать документацию у других производителей, для сравнения.

-

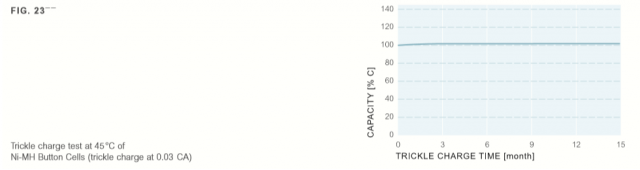

Нет. Режим "continuous overсharge" (или "trickle charge") подразумевает, что ток подзаряда существенно больше тока саморазряда, и аккумулятор работает в режиме стабилитрона. Далеко не все аккумуляторы допускают такой режим. Пример из даташита:

-

Именно это и имеется в виду, в даташитах этот режим еще может называться "trickle charge", и работать годами без деградации (при токе непрерывного подзаряда < 0,1С). Например, не менее 6 лет при токе не более 0,03С (попалось такое в одном даташите). Перезаряда не происходит, аккумулятор работает, как стабилитрон.

-

Увидел, в даташитах пишут параметр "continuous overсharge", например: 0,1С в течении года. Как при этом деградирует аккумулятор, не пишут (не увидел).

-

Постоянный (годами) подзаряд LSD Ni-MH током 0,1C

Leka опубликовал тема в В помощь начинающему

Несколько лет назад прочитал в даташите (на сайте производителя, сейчас на сайтах только реклама, даташиты сходу не находятся), что Ni-MH с низким саморазрядом допускают постоянный подзаряд малым током. Это существенно упрощает схемотехнику. Есть у кого какая практика/информация по такому режиму работы аккумулятора ? -

tjournal.ru 14 марта 2022 года сайт издания заблокирован на территории России по требованию Генеральной Прокуратуры РФ

-

Человеческий мозг заканчивает свое развитие к 20 годам. Обучать чему-либо после этого возраста - получится белковый робот. Нужно что-то большее - снижать порог вхождения.

-

Крупный ФАБ столько за час производит.

-

Новейшая история. На складе модель NNN закончилась, нужно 1000000 штук, ближайшая поставка - XXX недель. Аналог есть? Есть, но другой набор периферии. Переписать программу. И другой корпус. Переделать плату.

-

Бег по кругу, 2022 --> 1970.

-

Это еще почему ? Упрощенно говоря, микропроцессору нужно много тактов для реализации какого-либо простого алгоритма, жесткой логике - 1 такт. Именно поэтому переходят на жесткую логику, если требуется производительность или энергоэффективность. Почему предлагаю реанимировать толстые техпроцессы - из-за существенно более низкого порога вхождения. Ниже порог вхождения - больше вероятность, что в эту отрасль попадет тот, кто впоследствии сможет вытянуть ее на передовой уровень.

-

А какой он, требуемый уровень ? https://ru.wikipedia.org/wiki/Список_микроэлектронных_производств